When performing BD file validata design, an error is reported:

[BD 41-237] Bus Interface property FREQ_HZ does not match between /DMA_AXIS_MM2S(100000000) and /axi_dma_0/M_AXIS_MM2S(200000000)

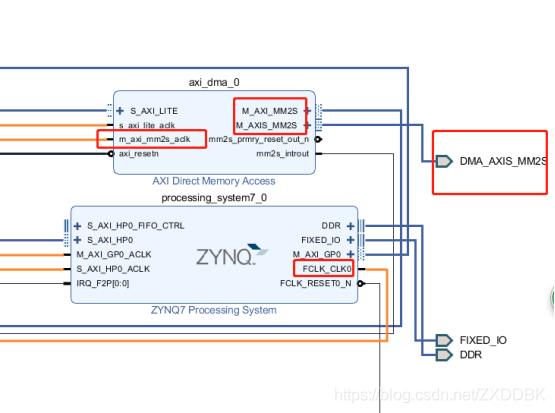

As shown in the figure, I have defined an extended interface DMA_AXIS_MM2S. The default frequency of the extended interface is 100M, but the clock from FCLK_CLK0 on the PS side is 200M, so the two frequencies do not match.

Solution:

Right-click the extended interface, select "external interface pproperties", and change FREQ_HZ to 200M in "CONFIG".