学习摘要

1、 PCIe是PCI的一种拓展,这意味着虽然物理层面上和PCI不同,但是逻辑上是一脉相承的。事实上,只要操作系统支持PCI总线的协议,那么即使是PCIe也可以正常的在PCI bus上工作,而不会产生任何问题。

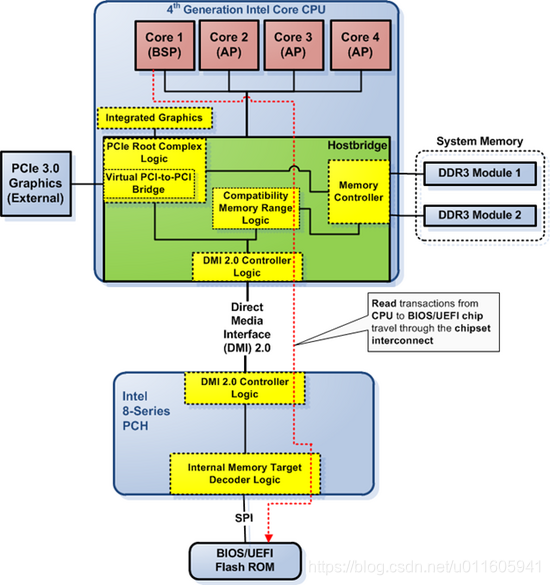

2、 Platform firmware一般指的是在reset阶段用来初始化平台的代码,也就是BIOS或UEFI代码,代码一般保存在flash ROM chip或主板上。

3、

4、 上图表示了CPU通过PCH来访问BIOS/UEFI的flash内容。PCH和flash之间是SPI总线。平台要做的是向下兼容,即可以正常跑DOS或32bits的系统。

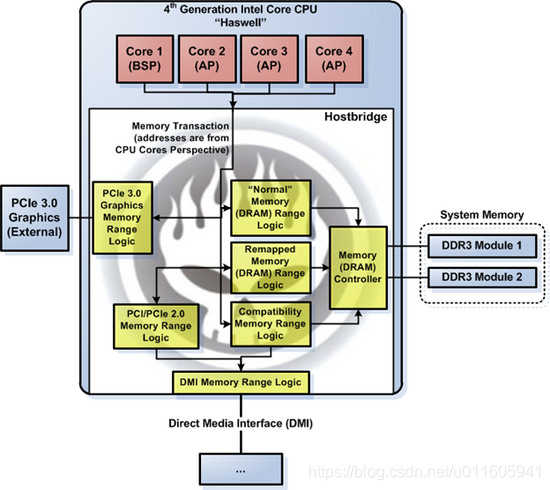

5、 CPU中并非所有的核都是平等的,在BIOS或UEFI阶段,其中的一个核会被标志为boot strap processor (BSP),剩余的核被称为application processors (AP)。在系统第一次启动或硬件复位的时候,只有BSP核会正常工作,其余的核不会工作。AP核是在系统初始化时才会被激活。BSP中跑的是BIOS的代码。

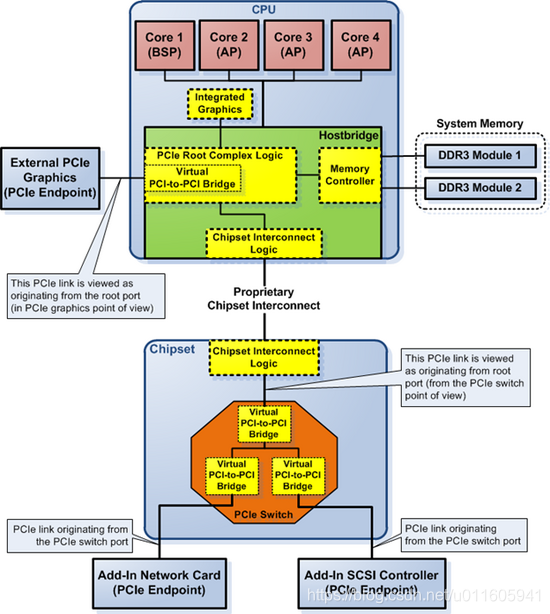

6、 PCIe作为一个PCI设备,有的还包含PCI to PCI bridge。例如the root port (“outgoing” port from the root complex)就是一个逻辑上的PCI-to-PCI

bridge。另外,PCIe switch也是逻辑上的多个PCI-to-PCI bridge。一个PCI Root Bridge是PCI树结构的根节点,从它往下可以挂不同的设备。PCI Root Bridge下的总线一般称为BUS(0),不过需要注意这里的0并非表示实际的总线地址是0,因为一个Host Bus Controller下可能存在多个PCI Root Bridge,所以实际的地址要根据PCI Root Bridge的个数来分配。例如有两个PCI Root Bridge,而一个Host Bus Controller下总线的最大个数是256个(0x00~0xFF),所以两个PCI Root Bridge下的总线应该是0x00和0x80,即将总线地址分成了两个PCI总线域。前面已经讲到PCI Root Bridge是PCI树的根节点,在它之下是BUS(0)。而在BUS(0)下面可以接两种类型的PCI设备,分别是PCI Bridge和PCI Agent。其中PCI Bridge用来扩展原来的PCI总线,在PCI Bridge之下可以延伸出新的总线,以此连接更多的设备。而PCI Agent就是真正的PCI设备(比如网卡)了,是PCI树的最末端。另外,PCI Bridge还分透明桥和非透明桥,PCI Agent还分主设备和从设备,在这里不多做介绍

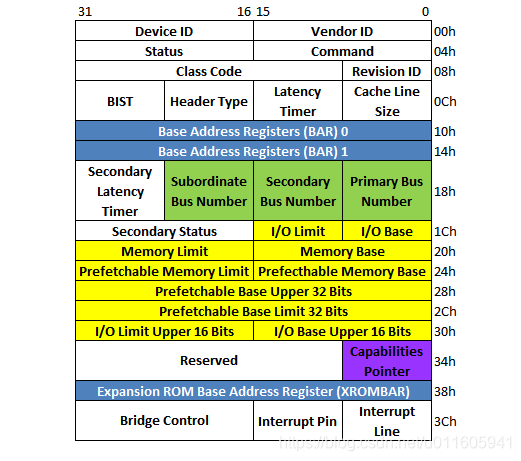

7、

8、 PCI-to-PCI bridge必须操作type1 header在配置空间中。PCIe configuration space header中,黄色标注的部分是PCI-to-PCI

bridge的第一接口(离CPU更近的接口)和第二接口(离CPu更远的接口)的memory和IO的配置空间。绿色部分是第一借口和第二接口的bus number。紫色部分是用来拓展PCIe空间的寄存器,对于每一个PCIe设备都是需要设置。

9、 如果Memory limit

register的值大于Memory Base register的值,那么PCI-to-PCI bridge将会向下游(downstream)传输数据。传输的地址范围落在这两个寄存器中的地址之间。Memory limit/Base和Prefetchable Memory Limit/Base两者有两个区别,其一是前者用来在读指令传输具有边效应(side effect on read transactions)的设备上使用,后者在不具有边效应的设备上使用;其二是prefetchable是64位的因此可以访问到大于4GB的地址空间。所有具有side effect的设备都需要将内存空间映射到4GB以内的空间之内。

10、

关于limit和Base还有一个问题就是,在upstream方向上,对于超出limit和base区间的数据该如何处理。这个问题之所以具有讨论的价值是因为目前平台支持DMA功能,而对于DMA功能的实现需要依赖于PCI-to-PCI bridge可以确保设备正常访问内存。如果bridge不能正常的给上行通道传输数据,那么DMA功能也就无法实现。

11、

有一类“负解码”(subtractive decode)的PCI-to-PCI bridge。当线路上没有device响应trascation时,可以自己响应。目前用的很少了。

12、

Root complex用来连接PCIe设备和memory、CPU。目前一般都集成到了CPU里面,但是root port不一定在CPU里面,也有可能在PCH上面。除此之外,一般PCIe tree还有PCIe switch和PCIe endpoint。

13、

14、

PCIe switch里面一般会有数个PCI-to-PCI

bridge从而实现port之间互相传输数据的。

15、

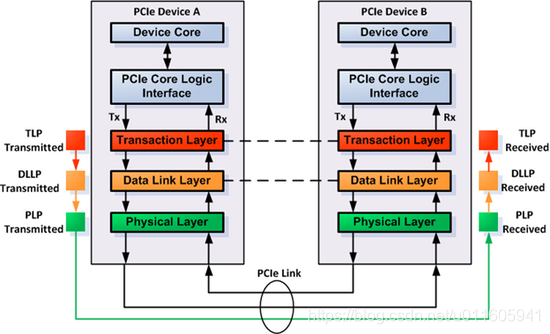

16、

PCIe 的协议类似于TCP/IP协议。在PCIe 协议中,一共有3种数据包,分别是Transaction layer packet (TLP)、Data link layer packet (DLLP)、Physical layer packet (PLP)。TLP包括CRC位和data,可以通过switch传达至PCIe tree的任意节点。DLLP包括另一个CRC,这个CRC只是确保接收端的device收到的数据是正确的。DLLP只能接受相邻的PCIe链路的包。PLP会对DLLP分成一个一个的数据帧然后发现送出去。

17、

PCIe有4个address space。(1)PCIe configuration space。最长4K,其中头256byte是为了兼容PCI的configuration space,它的映射是使用的IO space机制。而对于全部的4K的配置空间,则是通过memory space机制。(2)PCIe memory space。虽然(1)中有一部分内容存在memory space里面,但是这里的memory space指的是PCIe设备所产生的数据的存放空间;(3)PCIe IO space。为了向下兼容;(4)PCIe message space,是PCIe区别于PCI新引入的address space,目的是为了减少sideband signal的使用。

18、

PCIe保留PCIe configuration mechanism的原因有两点,其一是为了向下兼容PCI设备,其二是初始化的时候,由于4k的memory space不是硬编码的,因此需要为其配置空间重新分配起始的内存位置。PCIe

configuration mechanism可以在boot的早起阶段为PCIe设备分配没存空间。

19、

PCIe 配置空间寻址寄存器有64位,其中20到27位是PCIe bus

number(1到256);15到19 bits是device number(1到32);12到14 bits是function number(1到8)。28到63位是。

20、

PCIe和PCI不同的一点就是,PCIe必须在配置空间的头256bytes字节设置PCIe

capabilities register set。而PCI则是可选项。PCIe capabilities register set里的选项是用来配置device是否映射到memory space或者IO space。这对于某些情况是有必要的,因为对于一些VGA设备,其IO要求是固定的地址位置。

21、

22、

上图中一共有5中memory的传输路径,分别是a 普通的DRAM range逻辑,该路径是直接寻址的不需要做重映射;b remapping DRAM range logic,该路径需要将memory

transaction进行重映射; c compatibility memory range logic,该路径是将transcation覆盖至兼容内存范围上;d

PCIe3.0 graphic memory range logic,该路径试讲transaction外部PCIe显卡的BAR范围内;e PCIe

2.0/PCI内存范围逻辑,

23、

24、

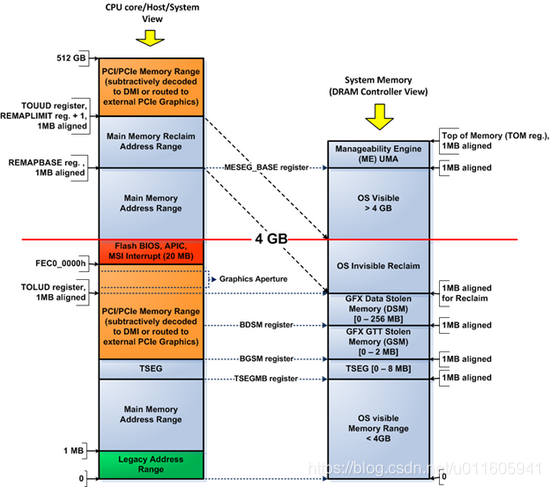

上图分别给出了系统内存的两种视角,分别是从CPU看过去,和从DRAM controller看过去,这两个的区别是,DRAM controller不会关注被PCIe设备消耗的内存范围,并且它也不需要关注这些东西。北桥会将DRAM中从TOLUD到4GB的内存空间映射到一个新的大于4G的内存范围之内,这个内存范围被称为“reclaim” memory range。Legacy address range是为了兼容DOS的范围;Main memory reclaim address range是不需要重映射即可访问DRAM的内存地址,OS可以对这一范围的地址可视;TSEG

range是top of main memory segment的简称,这一片段的内存保存着runtime数据和平台固件,只有SMM(system

management mode)可以访问到,OS无法看到这一片区域。

25、

对于haswell平台,PCIe enhanced configuration memory所需要的空间大小为:256

x 32 x 8 x 4KB,即最多支持256条总线,每个总线上32个设备,每个设备上有8个功能。即256MB