1.简述

一个完整的IC EDA环境也不能缺少了FPGA,FPGA原型验证是IC设计流程中重要的一环。一个芯片从设计到流片需要投入大量的人力、财力以及很长的研发周期,如果流片失败,对于公司来说是一笔很大的损失,同时对于研发的工程师来说这是一场重大的设计失误,重则内部会追究责任,所以验证尤为关键,能够发现很多设计的bug,而在FPGA验证是在真实的电路上验证,能够发现一些仿真器没有发现的bug,如果设计芯片是soc,那么还可以在FPGA上针对芯片功能进行嵌入式开发,不用等芯片流片回来再进行开发,缩短整个芯片的开发周期。FPGA原型验证是比较复杂的工作,我这里说的比较笼统,想了解的朋友建议某乎上搜一搜。

但是对于我们来说是业余开发,不太可能从前端到后端走完IC完整的开发流程,但是为了得到比较好学习效果,只好选择:设计=>前仿=>FPGA,可能后面加入DC综合与后仿,不会走后端的流程,所以搭建FPGA环境很重要,这个环境也换个说法:在linux下开发FPGA。

2.IC工程目录结构

目前暂定为以下目录结构,如图所示一个呼吸灯工程,但是以后会根据工程的具体情况有所变动,请以实际为准;

1)IC工程一级目录:

- FPGA:存放FPGA相关文件

- module:存放项目源码

- script :存放项目的脚本,目前还没有使用

- tb:存放测试用例

- verification :仿真验证目录

2)FPGA工程目录:

- constraint :放置FPGA约束文件

- libs:放置FPGA IP 核

- script:存放FPGA综合脚本

- work:FPGA综合所在目录

3.FPGA环境搭建

我目前使用的是Xilinx的K325T FPGA板卡,上一篇也已经说过EDA环境已经安装Vivado2019.1,Linux下安装很简单,所以这里不讲怎么安装Vivado,需要Vivado安装后台回复“vivado”可以获得。

1)添加vivado环境

在home目录下,打开.bashr,添加如下命令,路径根据自己的修改,保存退出后记得source一下让环境生效。然后在terminal输入 “vivado” 就会启动vivado的gui。

source /home/Xilinx/Vivado/2019.1/settings64.sh

2)FPGA Tcl脚本

下面是vivado综合的Tcl脚本,根据你自己的Xilinx FPGA板卡修改。

- 我的板卡是差分时钟,使用了clk_wizd的IP;

- 最后一行生成Flash烧写的mcs文件,需要根据自己板载的Flash型号调整;

- 根据你虚拟机分配的处理器数量,设置maxThreads,如果脚本设置超过实际的分配,会综合出错,这问题坑了我一天;

#################################################

# vivado FPGA environment configuration

#################################################

set PRJ_NAME Breath_led

set SCRIPT_DIR ../script

set CONST_DIR ../constraint

set DEVICE_NAME xc7k325tffg676-2

set XDC_FILE $CONST_DIR/pin.xdc

set CODE_FILE ../../module/breath_led.v

################################################

#Step1: Create project and overwrite old files

################################################

create_project -force $PRJ_NAME ./ -part $DEVICE_NAME

read_xdc $XDC_FILE

add_file $CODE_FILE

add_files ../libs/sysclk_wiz/sysclk_wiz.xci

set_property ip_repo_paths ../libs/sysclk_wiz [current_project]

set_property verilog_define {

FPGA_SYN=1} [get_filesets sources_1]

#set max threads

set_param general.maxThreads 8

# Launch Synthesis

launch_runs synth_1

wait_on_run synth_1

# Launch Implementation

launch_runs impl_1 -to_step write_bitstream

wait_on_run impl_1

write_cfgmem -format mcs -size 128 -interface BPIx16 -loadbit {

up 0x0 "Breath_led.runs/impl_1/breath_led.bit" } -checksum -force -disablebitswap -file Breath_led.runs/impl_1/Breath_led.mcs

3)Makefile

需要说一下“open”,这个可以自动化启动vivado gui并自动加载综合的工程。

clean:

rm -rf *.cache *.hw *.sim *.ip_user_files *.runs

rm -f *.jou *.log *.txt *.xpr

built:

vivado -mode batch -source ../script/create_prj.tcl &

open:

vivado -source open_project ./*.xpr &

4.vivado识别不到板卡

设置虚拟机的usb的兼容性,默认设置是兼容usb2.0,我的电脑是usb3.0,修改如下。

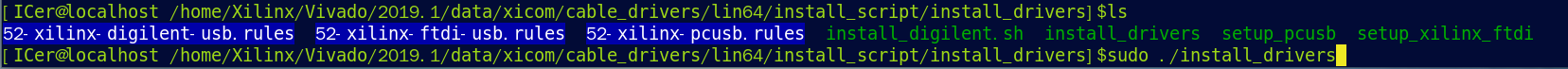

如果还是无法识别,安装下cabel的驱动,进入到驱动目录,进行root安装。然后重启一下vivado应该能识别到板卡。

cd /home/Xilinx/Vivado/2019.1/data/xicom/cable_drivers/lin64/install_script/install_drivers

sudo ./install_drivers

5.总结

到这里IC EDA环境已经比较完善了,后面还会补充新的内容,后面可能主要以项目为主了,目前正在研究蜂鸟E203,也会基于这个环境做分享。想获取Breath_led的工程后台回复“Breath_led”可获得下载连接。

整个流程的演示效果:

数字IC EDA环境(vcs2018+verdi2018) 数字IC工程师业余开发环境演示(支持linux 自动化高效开发FPGA)

传送门:数字IC EDA环境(vcs2018+verdi2018) 数字IC工程师业余开发环境演示(支持linux 自动化高效开发FPGA

6.公众号与微信交流区

刚新建了微信交流群,欢迎加入!!!