ザイリンクスのFPGAは、使用するIPコアデジタル信号処理、およびIPコアストレージクラスは、そのようなIPコア数学のクラスとしてプロジェクト全体のIPコアのために有用と非常に役立つをたくさん持っている、この記事では、BRAM IPコアを紹介しますそれは使用しています。

FPGA BRAMは、RAMの習慣である大規模なストレージスペース、および毎日のプロジェクトで頻繁に使用されています。BRAMは、FPGA、主記憶機能の様々な部分のFPGA実装で、真のデュアル読み出し/書き込みポート同期RAM内のアレイ状に配置されています。

フィルムは2017.1の物品Vivadoのバージョンに基づいて、他のバージョンも同様です。

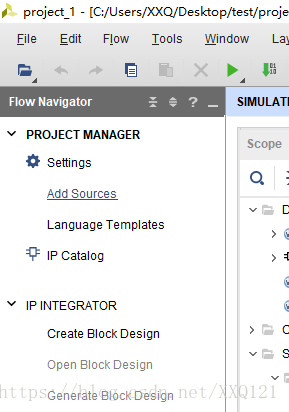

まず、インターフェイスVivado IPカタログオプションの右側を選択します。

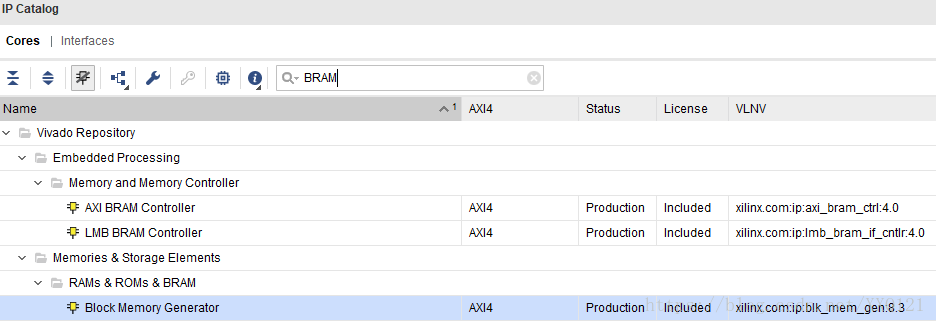

そして、あなたがIPカタログには、必要なIPコアを選択することができ、BRAMは、検索ボックスに入力され、ここで、BRAMは、我々が使用するIPコアを選択します。

ブロックメモリジェネレータすなわち、最下位、名前が示すように、ブロックRAM。

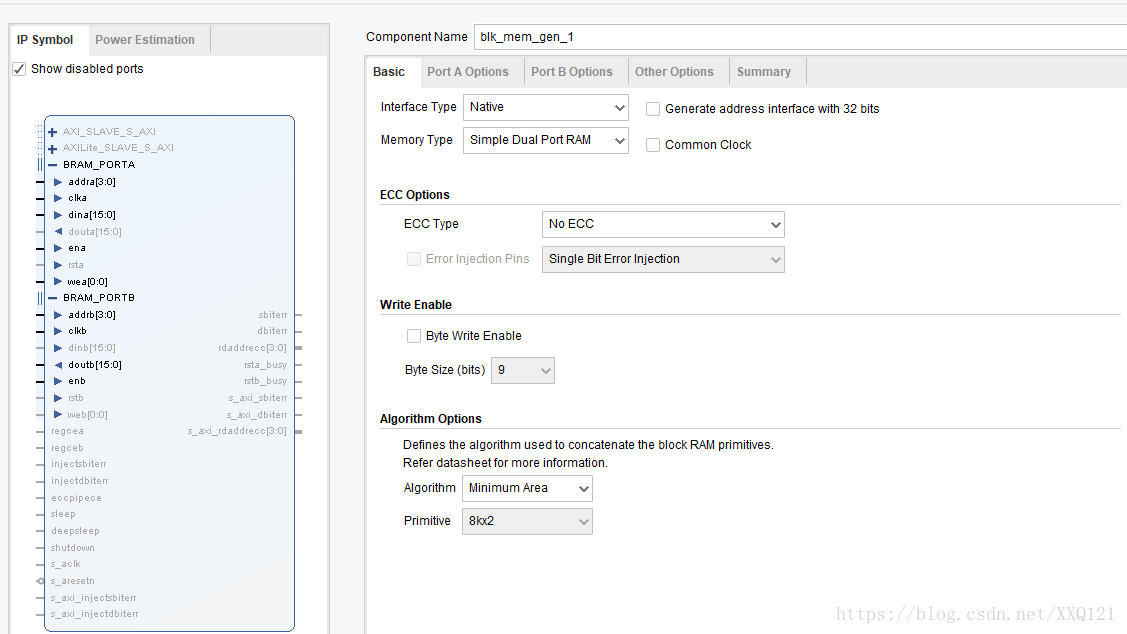

私たちは、シングルポートを書き、シングルポートBRAMを使用し、シングルポートをお読みください。メモリタイプは、シンプルデュアルポートRAMに構成することができます。下図のように:

あなたは彼らが必要とするモジュール名をカスタマイズすることができコンポーネント名。定義されたタイプ後、ポートモジュールの背後に見ることができ、ポートは、ディスプレイの左側に使用され、次いで手の込んだ。

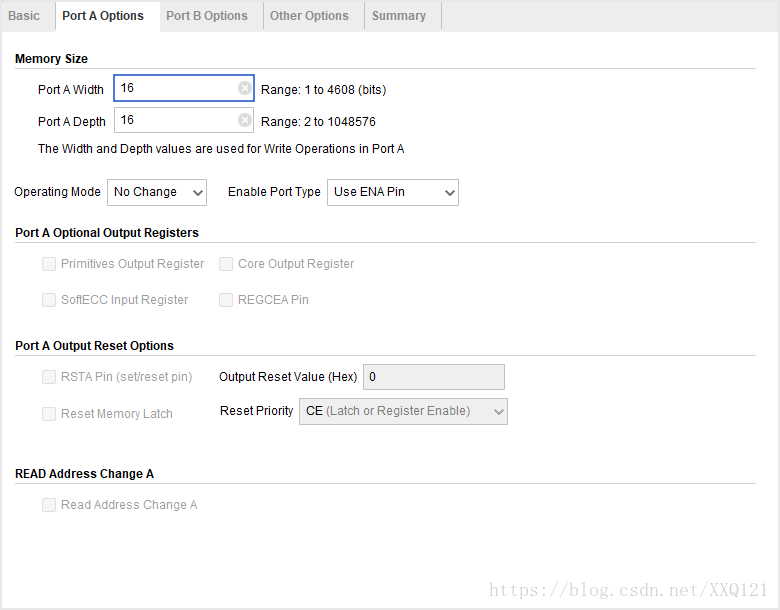

セットアップが完了した後、ポートAオプションオプションを選択し、ポートのビット幅と深さを開始するには、次のインターフェイスを見ることができます。

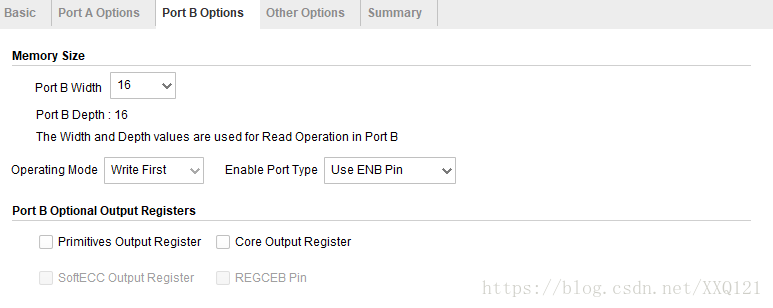

すなわち、ビット幅ポートA幅、それは、どのように多くのあなたの格納されたデータのれるポート深その深さ、それはあなたが保持したいどのくらいのデータです。ポートAが設定された後、さらにクリックする必要があり、ポートBのオプションを入力[完了]をクリックし、ポートBオプションオプションは、システムが自動的にBとAは同じでなければなりませんので、あなたが、幅といい、ポートBの深さを設定するのに役立ちます。

可以看到端口B也设置完成,同时在Port B Optional Output Registers有一个Primitives Output Registers选项。如果这个选项不勾上,那么正常的情况下,当第一个时钟时候,送来地址,那么数据会在第二个时钟取好送出RAM。但是当勾上这个选项后,那么数据就会延迟两个时钟,在第三个时钟送出。这是取数据情况下的时序。当存数据时候,那么只需要地址和数据在同一个时钟下即可。

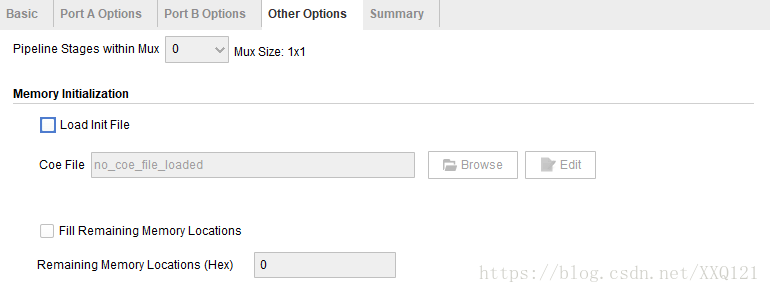

当我们在一般使用RAM时候,如果需要事先存到RAM里的数据量不大,我们可以在Testbench里面写一下即可。但是如果数据量较大时,那么我们可以使用.coe文件事先将数据导入到RAM 之中,如下图所示。

在Other Options选项中,有一个Load Init File选项,即加载初始化文件,在这里勾上后,即可加载已存储好数据的.coe文件。关于.coe文件的制作,网上有很多教程,在此不再赘述。然后点击下方OK,然后再点击弹出来的窗口的Generate即可生成BRAM 的IP核。

至此,常用情况下的BRAM的配置选项以及设置介绍完成。

Xilinx公司的FPGA中有着很多的有用且对整个工程很有益处的IP核,比如数学类的IP核,数字信号处理使用的IP核,以及存储类的IP核,本篇文章主要介绍BRAM IP核的使用。

BRAM是FPGA定制的RAM资源,有着较大的存储空间,且在日常的工程中使用较为频繁。BRAM以阵列的方式排布于FPGA的内部,是FPGA实现各种存储功能的主要部分,是真正的双读/写端口的同步的RAM。

本片文章是基于Vivado的 2017.1的版本,其他版本都大同小异。

首先在Vivado界面的右侧选择IP Catalog 选项。

然后就可以在IP 目录中,选择想要的IP核,此处在搜索框输入BRAM,选择我们要使用的BRAM IP核。

即最下方的Block Memory Generator,顾名思义,块状RAM。

我们常用的是单口BRAM,单口写,单口读。可配置Memory Type 为Simple Dual Port RAM。如下图所示:

其中Component Name 可以自定义自己所需要的模块名称。类型定义完成后,可以看到左侧显示的模块端口,端口的使用后面再细说。

设置完成后,开始设置端口的位宽以及深度,选择Port A Options选项,可以看到下面的界面。

Port A Width即位宽,也就是你存储数据的有多少位,Port A Depth即深度,也就是你要存多少个数据。端口A设置好后,还需要点击Port B Options,点击完进入Port B Options选项后,系统会帮你自动设置好端口B的宽度和深度,因为B肯定是和A一样的。

可以看到端口B也设置完成,同时在Port B Optional Output Registers有一个Primitives Output Registers选项。如果这个选项不勾上,那么正常的情况下,当第一个时钟时候,送来地址,那么数据会在第二个时钟取好送出RAM。但是当勾上这个选项后,那么数据就会延迟两个时钟,在第三个时钟送出。这是取数据情况下的时序。当存数据时候,那么只需要地址和数据在同一个时钟下即可。

当我们在一般使用RAM时候,如果需要事先存到RAM里的数据量不大,我们可以在Testbench里面写一下即可。但是如果数据量较大时,那么我们可以使用.coe文件事先将数据导入到RAM 之中,如下图所示。

在Other Options选项中,有一个Load Init File选项,即加载初始化文件,在这里勾上后,即可加载已存储好数据的.coe文件。关于.coe文件的制作,网上有很多教程,在此不再赘述。然后点击下方OK,然后再点击弹出来的窗口的Generate即可生成BRAM 的IP核。

至此,常用情况下的BRAM的配置选项以及设置介绍完成。