IP構成

- 構成

- チャンネル数とFFT長を設定する

- クロック周波数とデータスループットレート

- FFT の構造の選択

- データを効率化できるストリーミング

- Radix-4 (4 に基づく反復アルゴリズム) は、パイプライン構造よりも多くのリソースを使用しますが、変換時間が長くなります。

- Radix-2 と Radix-2 lite はどちらも基数 2 の反復アルゴリズムで、Radix-2 lite の方が使用するリソースは少なくなりますが、変換時間も長くなります。

- 実行時設定の変換長

構成情報は動的に変更できます。

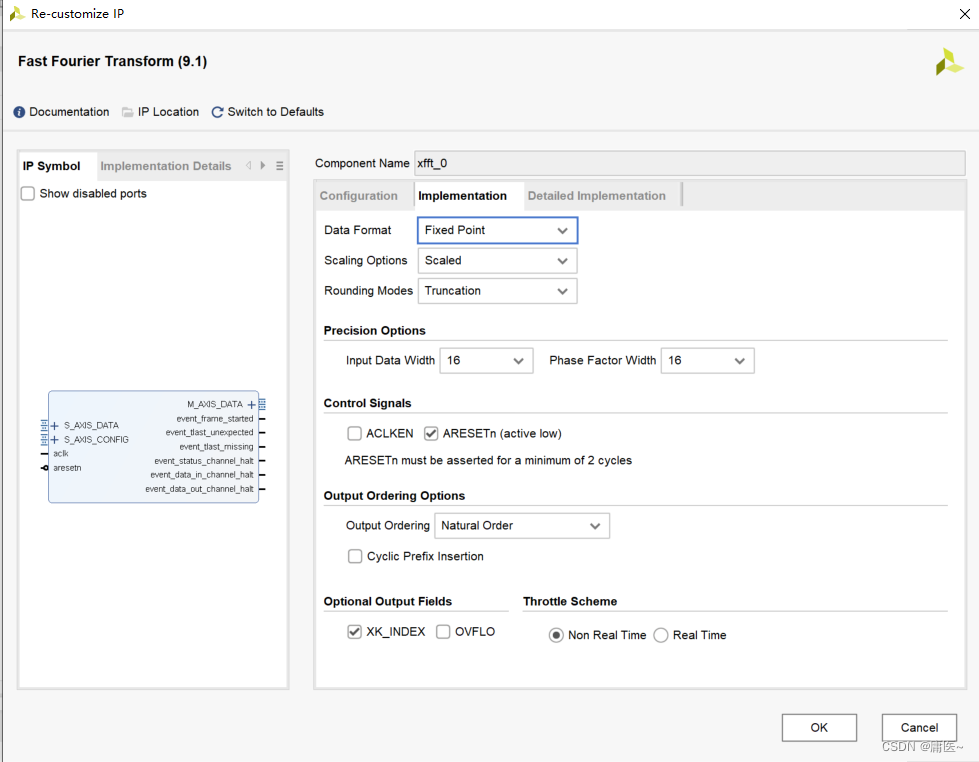

- 実装

- データ形式

- 固定小数点または浮動小数点

- 拡大縮小オプション

- スケールなし: すべての整数ビットのデータ出力。これにより、より多くの FPGA リソースを使用できるようになります。

- スケーリング: インターセプトされたデータ フィールドの入力データ ビット幅は同じです

- ブロック浮動小数点: このメソッドは、利用可能なダイナミック レンジを完全に活用するためにどの程度のスケーリングが必要かを決定し、スケーリング係数をブロック インデックスとして報告します。

- 丸めモード

- トランケーション方法: トランケーション、収束トランケーション。収束丸めでは、数値が奇数の場合は切り上げられ、数値が偶数の場合は切り捨てられます。

- Precision(精度)

- データ入力ビット幅

- 位相係数ビット幅: ビット幅が大きいほど出力ノイズは小さくなりますが、より多くのリソースが占有されます。

- 制御信号

- クロックイネーブル信号

- リセット信号

- 出力の順序付け

- 出力データの選択は、ビット/桁の逆順または自然順です。Radix-2 ベースのアーキテクチャ (Pipeline I/O、Radix-2 Burst I/O、および Radix-2 Lite Burst I/O) はビット反転ソートを提供し、Radix-4 ベースのアーキテクチャ (Radix-4 Burst I/O) はビット反転ソートを提供します。 I/O /O) は、数値的に逆のソートを提供します。パイプライン I/O アーキテクチャの場合、自然順序の出力順序を選択すると、カーネルが使用するメモリが増加します。バースト I/O アーキテクチャの場合、自然順序出力を選択すると全体の変換時間が長くなります

- オプションの出力フィールド

- XK_INDEX 出力データのチャンネル番号、つまりXKの添字、

- OVFLO はデータ出力チャネルとステータス チャネルを識別します。

- スロットルスキーム

- リアルタイム モードでは通常、より小型で高速なデザインが提供されますが、データをいつ提供および消費する必要があるかについては厳しい制約があります。非リアルタイム モードにはそのような制限はありませんが、デザインが大きくなり、速度が遅くなる可能性があります。詳細については、「FFT コアの制御」を参照してください。

- データ形式

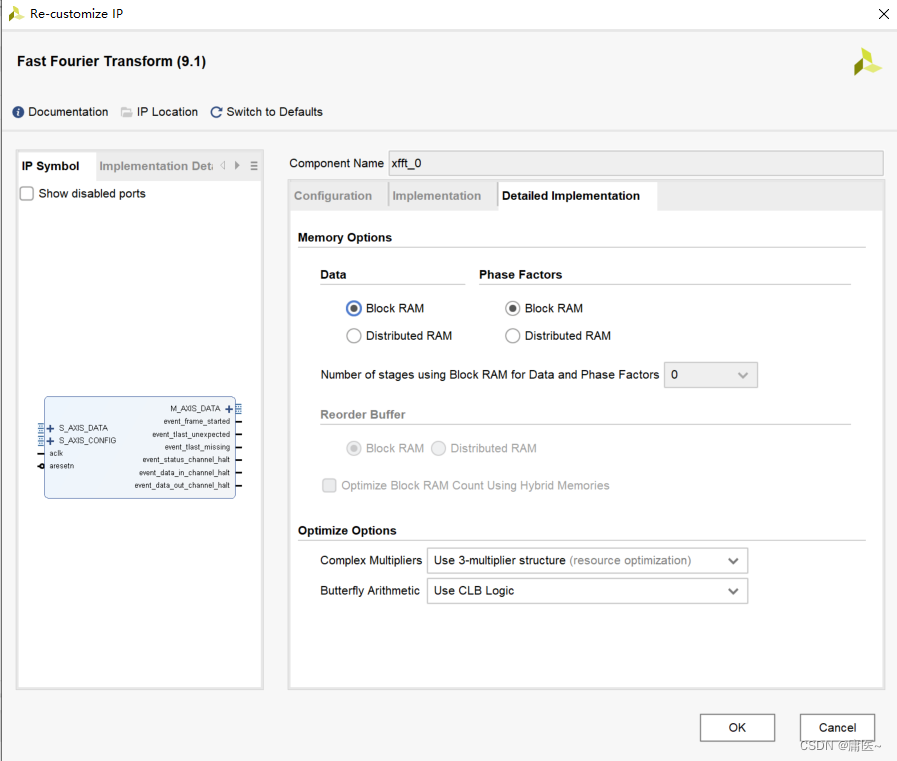

- 詳細な実装

- メモリオプション

- データストレージ用のメモリタイプを選択してください

- オプションの最適化

- 複素乗算器

- CLB ロジックを使用する: すべての複素乗算器はスライス ロジックを使用して構築されます。これは、パフォーマンス要件が低いターゲット アプリケーション、または DSP スライスの少ないターゲット デバイスに適しています。

- 3 つの乗算器構造を使用する: すべての複素乗算器は 3 つの実数乗算と 5 つの加減算構造を使用し、乗算器は DSP チップを使用します。これにより、DSP スライス数が減りますが、いくつかのスライス ロジックが使用されます。この構造は、DSP チップ前置加算器を利用して、追加のチップ ロジックの必要性を削減または排除し、パフォーマンスを向上させることができます。

- 4 乗算器構造を使用する : すべての複素乗算器は 4 つの実数乗算、2 つの加算および減算構造を使用し、DSP スライスを使用します。この構造は、より多くの専用乗算器を犠牲にして最高のクロック パフォーマンスを実現します。DSP スライスを備えたデバイスでは、加算/減算操作が DSP スライスに実装されます。

- 複素乗算器

- メモリオプション

s_axis_config_tdata (構成情報)

- 先送り/INV

- FFT を実行するには 0、逆 FFT を実行するには 1

- NFFT

- FFTのポイント数、例えばNFFT=3の場合、NFFTの値はlog2(ポイントサイズ)となります。8ポイントFFTを実行する

- CP_LEN

- 巡回プレフィックスの長さ: 変換全体が出力される前に、変換の終わりから巡回プレフィックスとして最初に出力されるサンプルの数。CP_LEN には、ポイント サイズより小さい 0 から 1 までの任意の数値を指定できます。このフィールドは、サイクリック プレフィックスが挿入される場合にのみ存在します。

- スケール_SCH

- FFT コアが浮動小数点データを処理するように構成されている場合、スケーリング スキームは必要ありません (SCALE_SCH は無視されます)。浮動小数点データの正規化とスケーリングは内部で処理されます。

- バースト I/O アーキテクチャの場合、スケーリング スケジュールは各フェーズに 2 ビットを指定し、最初のフェーズのスケーリングは 2 つの lsb によって与えられます。スケールは、シフトするビット数を表す 3、2、1、または 0 として指定できます。N = 1024、基数 4 バースト I/O の拡張スケジューリングの例は [1 02 3 2] (最後のレベルから最初のレベルにソート) です。N = 128、Radix-2 バースト I/O または Radix-2 Lite バースト I/O の場合、考えられる拡張プランは [1 1 1 1 1 0 12] (最後のレベルから最初のレベルにソート) です。

- パイプライン I/O アーキテクチャの場合、スケーリング スケジューラは、基数 2 ステージの各ペアに 2 つの lsb から始まる 2 ビットを割り当てます。たとえば、N = 256 のスケーリング スケジュールは [2 2 2 3] になります。N が 4 の累乗でない場合、最終段階での最大ビット増加は 1 ビットです。たとえば、N = 512 の場合、[0 2 2 2] または [1 2 2 2 2] は有効なスケーリング スケジュールですが、[2 2 2 2 2] は有効ではありません。この変換長の場合、SCALE_SCH の 2 つの msbs は 00 または 01 のみになります。このフィールドは、スケーリング演算 (スケーリングなし、ブロック浮動小数点、または単精度浮動小数点) の場合にのみ使用できます。

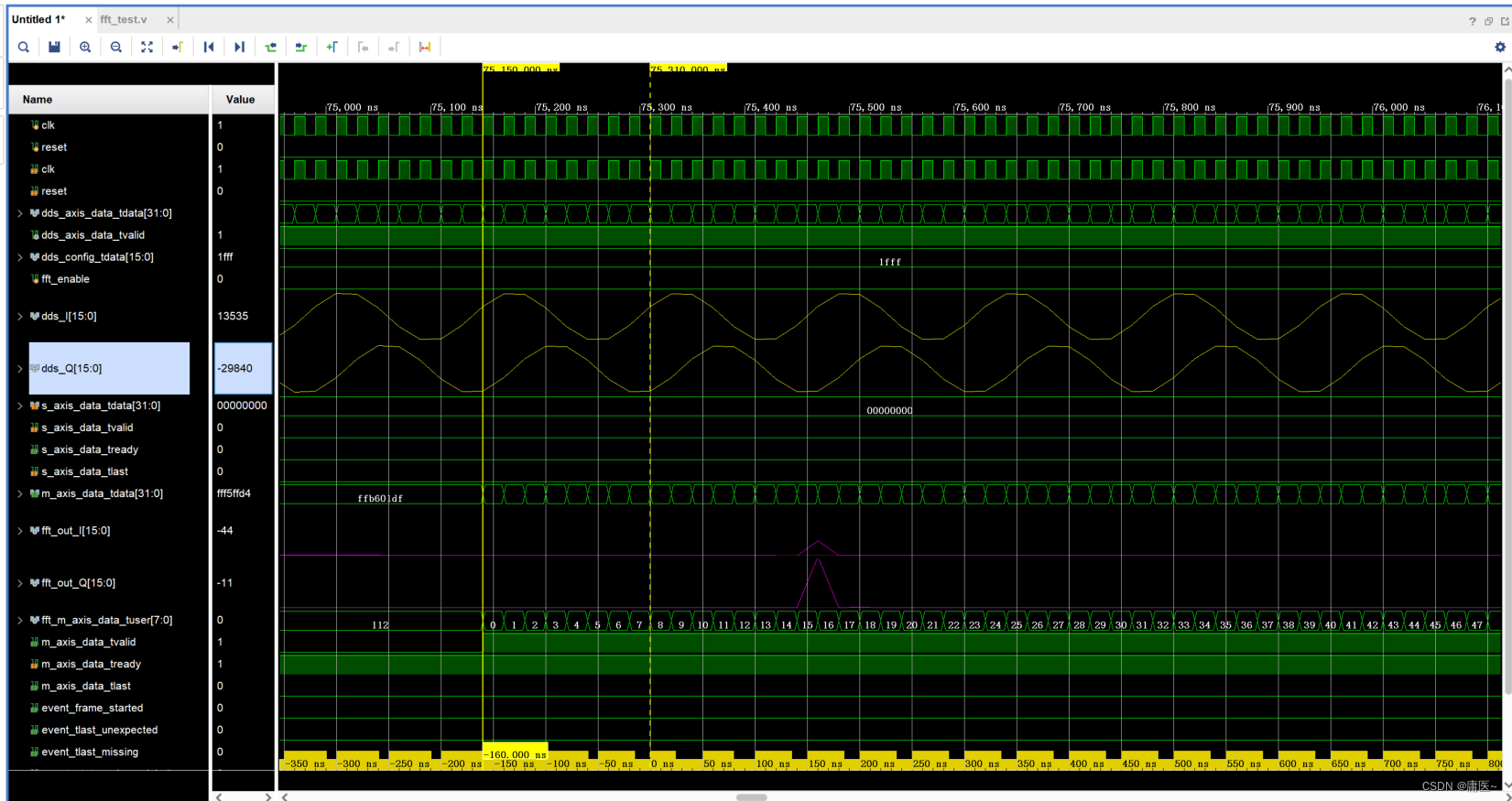

シミュレーション結果

信号入力と出力:

| 信号 |

方向 |

意味 |

| s_axis_config_tdata |

の |

構成パラメータ |

| s_axis_config_tvalid |

の |

|

| s_axis_config_tready |

外 |

|

| s_axis_data_tdata |

の |

入力データ(複数) |

| s_axis_data_tvalid |

の |

データ有効信号 |

| s_axis_data_tready |

外 |

|

| s_axis_data_tlast |

の |

各フレームの最後のデータを識別します |

| m_axis_data_tdata |

外 |

データ出力 (複数) |

| m_axis_data_tuser |

外 |

出力データのインデックス |

| m_axis_data_tvalid |

外 |

データは有効です |

| m_axis_data_tready |

の |

|

| m_axis_data_tlast |

外 |

最後のデータを識別します |

| イベントフレーム_開始済み |

外 |

このイベント信号は、新しいフレームの処理が開始されると、単一クロック サイクルの間アサートされます。この信号により、フレームをカウントし、必要に応じてコアの設定を特定のフレームに同期させることができます。 |

| イベント_tlast_unexpected |

外 |

フレームの最後のデータが受信されず、s_axis_data_tlast が High になると、入力データの長さが IP コアによって事前設定されたデータと一致せず、入力データの長さが事前設定された長さよりも短いことを示します。 |

| イベント_tlast_missing |

外 |

フレームの最後のデータが受信され、s_axis_data_tlast が High にプルされない場合、入力データの長さが IP コアによって事前設定されたデータと一致せず、入力データの長さが事前設定された長さよりも大きいことを示します。 |

| イベントステータスチャンネル停止 |

外 |

このイベントは、コアがデータ出力チャネルにデータを書き込む必要があるが、チャネル内のバッファーがいっぱいであるためにデータを書き込むことができない場合にアサートされます。これが発生すると、コア処理が停止され、チャネル バッファーにスペースができるまですべてのアクティビティが停止します。フレームにダメージはありません。 イベント ピンは、非リアルタイム モードでのみ使用できます。 |

| チャンネル停止中のイベントデータ |

外 |

このイベントは、IP コアがデータ入力チャネルからのデータを必要とするが、利用可能なデータがない場合に、サイクルごとにアサートされます。 |

| イベントデータアウトチャンネル停止 |

外 |

このイベントは、コアがステータス チャネルにデータを書き込む必要があるが、チャネル上のバッファがいっぱいであるためにデータを書き込むことができない場合にアサートされます。これが発生すると、コア処理が停止され、チャネル バッファーにスペースができるまですべてのアクティビティが停止します。フレームにダメージはありません。イベント ピンは、非リアルタイム モードでのみ使用できます。 |

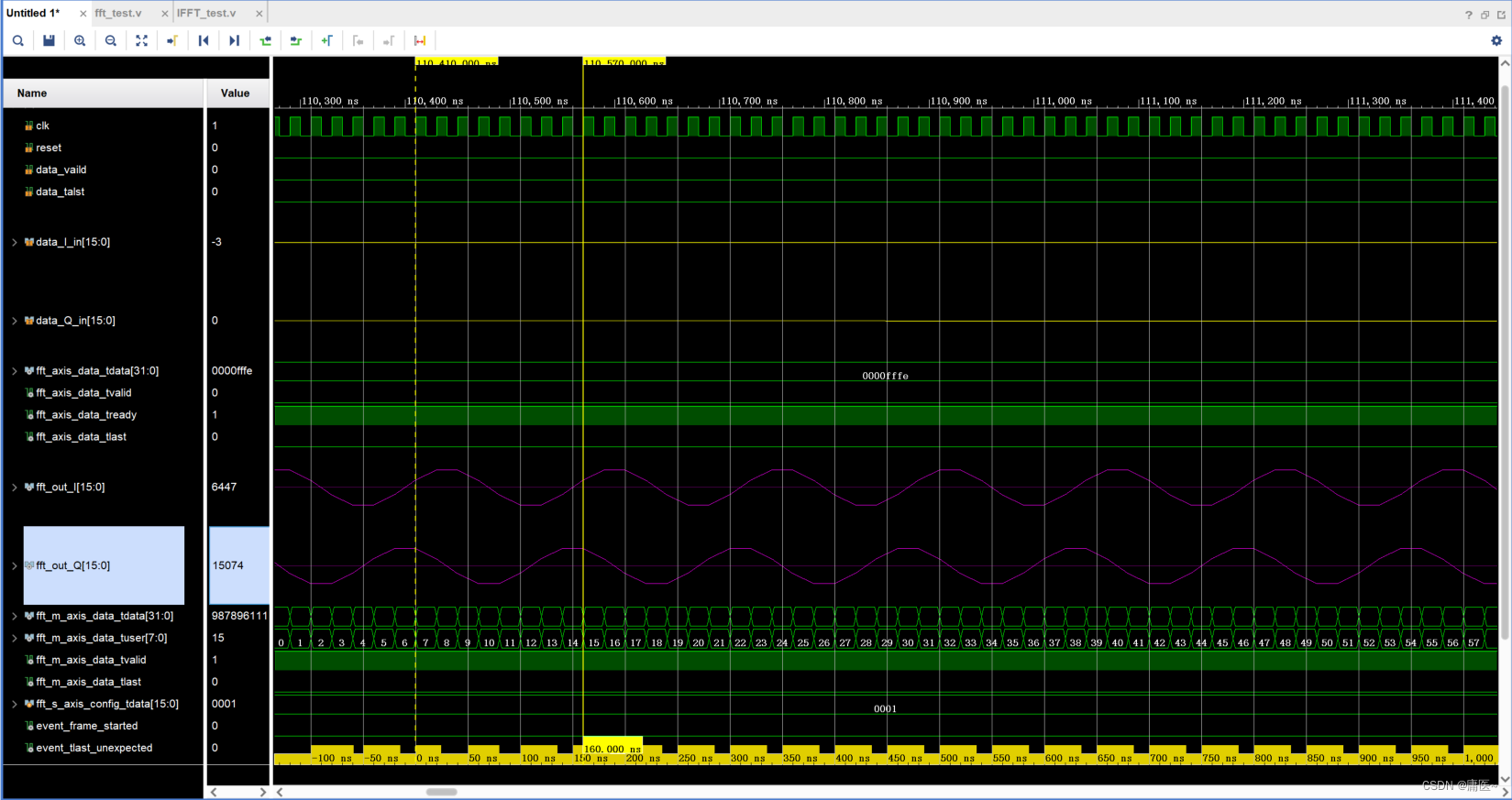

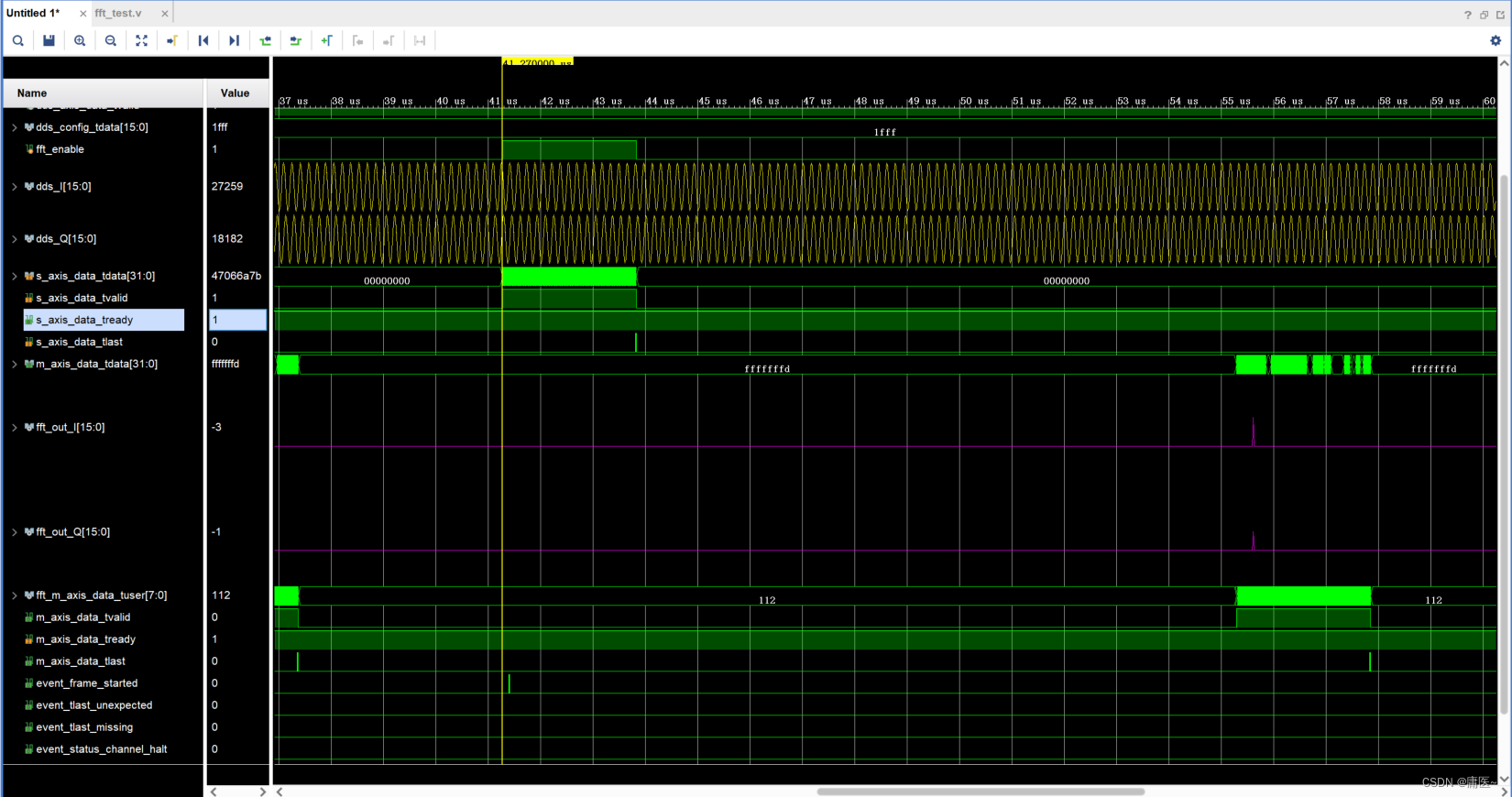

FFTシミュレーション結果

クロック周波数は 160M、正弦波周波数は 160M/8=20M、FFT (128 ポイント) 後、最大値は 16 番目のスペクトル ラインに達し、周波数は 160M/128*16=20M になります。

負の周波数を入力した場合、代表周波数は160M/128*(128-112)=-20Mとなります。

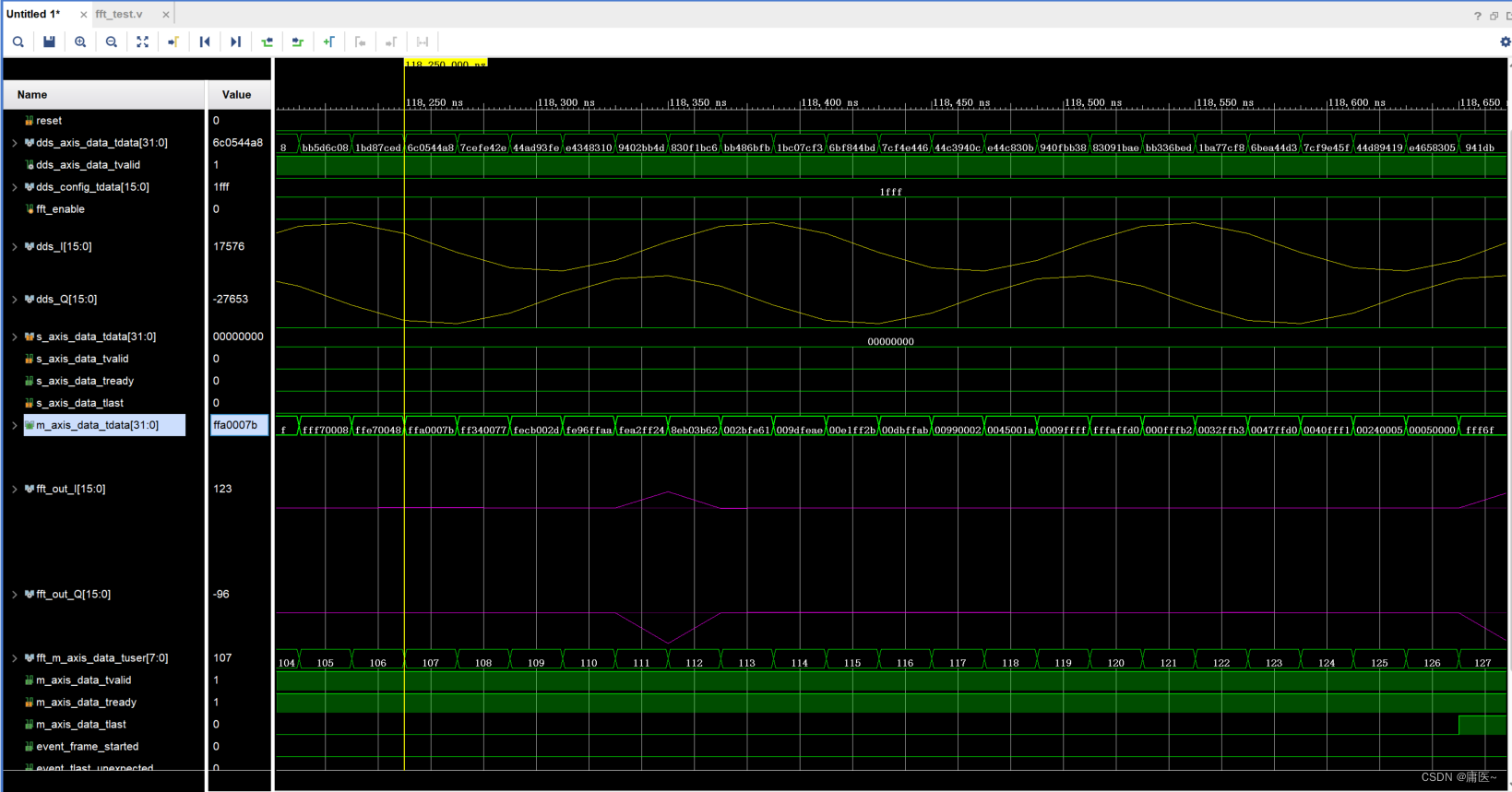

IFFTシミュレーション結果

IFFT 演算になるようにパラメータ FWD/INV を 1 に設定し、IP コアを IFFT モードに設定し、前の出力をシミュレーション用の IFFT の入力として使用します。

出力正弦波信号の周期は 8 160M クロックを占め、正弦波信号の周波数が 160M/8=20M であることを示し、これは FFT によって入力された信号と同じであり、IFFT 演算結果が正しいことを示します。