概要

組み込みシステムでは、多くの場合、集積回路間の通信が必要になります。一例として、デジタル温度センサーは部屋の周囲温度をメイン制御チップに報告します。通常、このデータはシリアル インターフェイスを介して送信されます。

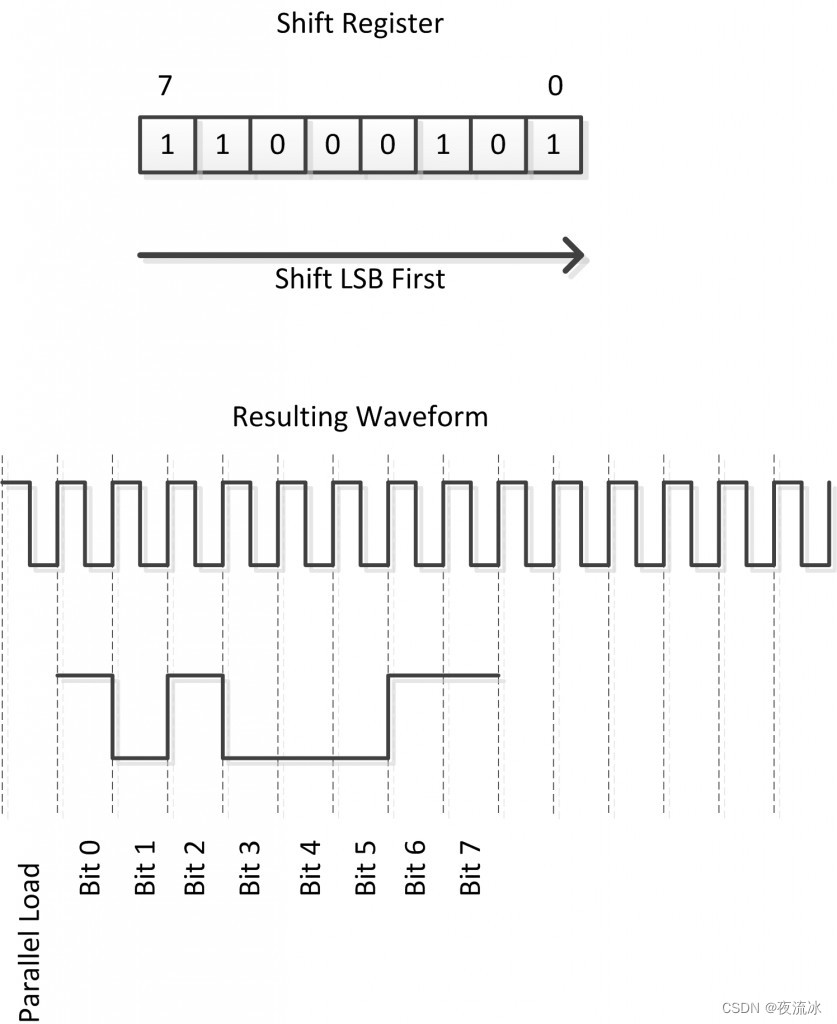

では、シリアルインターフェースとは何でしょうか? 最も基本的なシリアル インターフェイスは、一度に 1 ビットずつデータをシフトインおよびシフトアウトするシフト レジスタです。以下の図は、シフト レジスタのデータがメモリ コピーなどの並列手段によって最初にロードされることを示しています。並列ロードが完了すると、データは最下位ビットから始めてビットごとにシフトアウトされます。

では、なぜパラレル インターフェイスではなくシリアル インターフェイスを使用するのでしょうか? パラレル インターフェイスを使用して 32 ビット値を転送したい場合は、マイクロプロセッサに少なくとも 32 個のピンが必要です。パラレル バスは非常に高速ですが、多くの外部ピンを必要とし、この単一のインターフェイスに使用されるピンのみが必要になります。デバイスにピンを追加すると、部品表とマイクロプロセッサの物理サイズが増加します。

シリアル インターフェイスを使用する動機は、シリアル インターフェイスが少数のピンだけで構成されているためです。少数のピンを使用して、あらゆるサイズのデータを転送できます。必要なデータが 8 ビットではなく 32 ビットである場合にのみ、クロック周期を増やす必要があります。ピンの数を減らすと、デバイス間で配線する必要があるピンの数がはるかに少なくなるため、PCB (プリント基板) の開発も容易になります。

ここで扱うシリアル インターフェイスは UART と呼ばれます。UART という用語は、Universal Asynchronous Receiver/Transmitter (Universal Asynchronous Receiver/Transmitter) を指します。UART は通常、グラフィックス表示機能を持たないデバイスとのインターフェースに使用されます。UART はターミナル プログラムに入出力機能を提供できるため、ユーザーはステータスを監視し、入力機能を提供できます。

UARTの基本構造(インフラストラクチャ)

-

必要なピン(ピン)

UART インターフェイスは、Rx ピンと Tx ピンの 2 つのピンで構成されます。Rx ピンはデータの受信に使用されます。Tx ピンはデータの送信に使用されます。UART を使用して 2 つのデバイスが接続されている場合、1 つのデバイスの Rx ピンは 2 つ目のデバイスの Tx ピンに接続されます。

-

共通レジスタ

Rx ピンと Tx ピンは通常、別個のシフト レジスタ (1 つはデータのシフトアウト用、もう 1 つはデータのシフトイン用) に接続されます。2 つの独立したシフト レジスタにより、UART は同時にデータを送信および受信できます。

シフト レジスタに加えて、1 つ以上のステータス レジスタがあります。ソフトウェアはステータス レジスタをチェックして、送信シフト レジスタがいつ空になるかを判断します。送信レジスタが空の場合、データの次のバイトを送信シフト レジスタにロードできます。ステータス レジスタには、新しいデータ バイトがいつ受信されたかを示すステータス ビットもあります。一方、ソフトウェアは受信レジスタを読み取って削除操作をトリガーし、データの次のバイトをシフトインできるようにすることができます。

UART には、ソフトウェアで UART の動作を設定できるようにする追加のレジスタを持つことができます。データの送受信速度と送信データのフォーマットはソフトウェアで設定できます。たとえば、データの各バイトにパリティ ビットが含まれるかどうか、伝送速度のボー レートを設定します。

パケット構造

UART の重要な特徴の 1 つは、名前に含まれる「A」です。A" は非同期の略です。デバイス間に共有クロックがないため、UART は本質的に非同期です。代わりに、2 つのデバイスは、送信されるデータの構造とデータの送信速度について合意する必要があります。このプロトコルUART を許可します。インターフェイスはデータ ラインをオーバーサンプリングし、生データをパケットに再構築します。UART パケットを構成する 3 つのプロパティを調べます。

-

データレート

2 つの UART 間でデータを適切に送信するには、両方の UART が同じデータ レートでデータを送受信するように設定されている必要があります。これは、UART のボーレートと呼ばれることがよくあります。同じボー レートを設定することにより、UART の内部ステート マシンはシフト レジスタが動作するための適切なレートを設定できます。一般的なデータ レートには 9600 ボーや 115200 ボーなどがありますが、一部の UART は最大数 Mbit/s までのより高いデータ レートをサポートします。たとえば、CC2564c Bluetooth チップを使用すると、その上の UART はハードウェア フロー制御を備え、設定されたボー レートは 3Mbit/s に達します。

-

パリティ

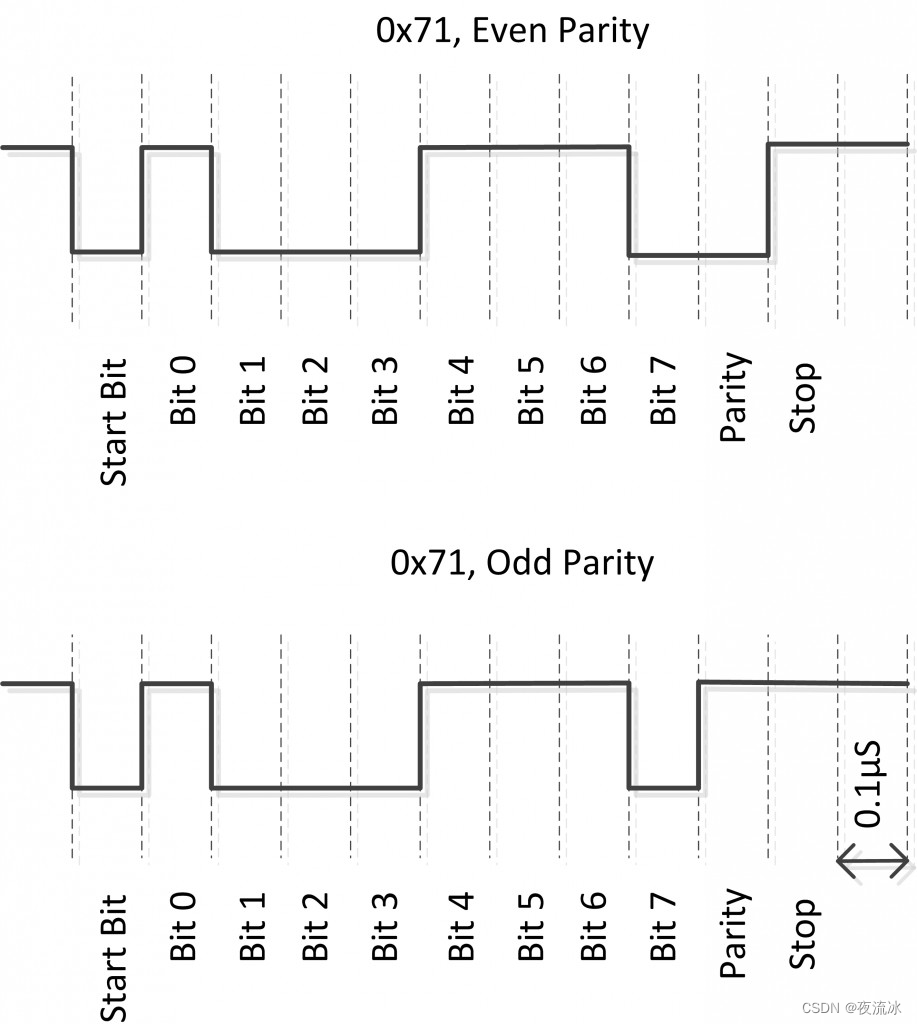

場合によっては、パケットにパリティ ビットが含まれることがあります。パリティ ビットは、送信中にデータ破損が発生したかどうかを判断するために受信デバイスによって使用されます。パケットが偶数パリティで構成されている場合、パリティ ビットを含む 1 の合計数は偶数である必要があります。パケットが奇数パリティで構成されている場合、パリティ ビットを含む 1 の合計数は奇数である必要があります。

-

データフレーミング¶

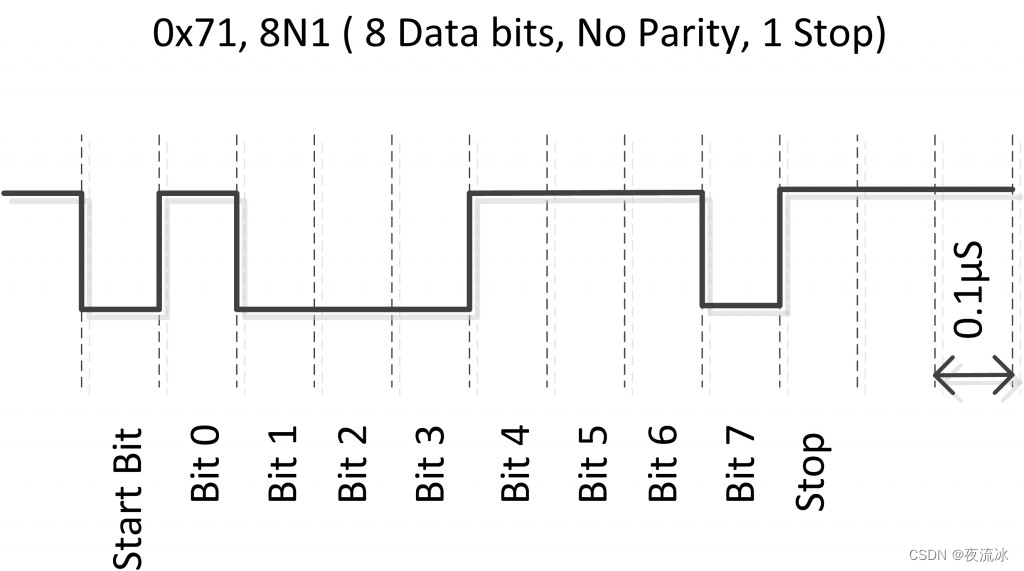

マイクロプロセッサがデータが送信されていることを検出するには、データが送信されていないときの Rx/Tx ラインの動作を定義する必要があります。ほとんどの場合、データが送信されていないときは、両方の Rx/Tx ラインが High に駆動されます。デバイスがデータを送信するとき、送信プロセスはスタート ビットから始まります。UART は Tx ラインを Low レベルになるようにプルダウンし、その期間は 1 クロック サイクルです。クロック サイクルはデータ転送速度に依存し、データ転送が開始されることを示します。

スタート ビットの後、データはすべてのデータ送信が完了するまで、定義されたデータ送信レートに従ってビットごとにシフトアウトされます。UART はデータの最下位ビットを最初に送信します。すべてのデータが転送されると、パリティ ビットが送信され (両方のデバイスの設定が同じである限り、このビットはオプションです)、その後にストップ ビットが送信されます。UART は、Tx ラインを High にプルし、1 サイクルの間 High を維持することによってストップ ビットを生成します。このサイクルはデータ送信レートに応じて異なります。多くの UART は、1 つまたは 2 つのストップ ビットを生成するように構成できます。

以下の図は、偶数パリティと奇数パリティを使用して値 0x71 がどのように送信されるかを示しています。

フレーミング エラーは、データがスタート ビットまたはストップ ビットなしで送信されると発生します。UART はこのデータを単純に破棄するか、ステータス レジスタにステータス ビットを設定することでエラー状態を通知する可能性が高くなります。ほとんどの場合、フレーミング エラーは、転送中のデータを無効にする大量の電磁干渉があるときに発生します。

8N1

UART の最も一般的な構成の 1 つは 8N1 と呼ばれます。これは、8 データ ビット、パリティ ビットなし、および 1 ストップ ビットを表します。8N1 は、10 ビット送信ごとに 8 ビットのデータを送信します。パリティ ビットと追加のストップ ビットを追加すると、パケットあたりのオーバーヘッドが増加し、実際のデータの全体的なスループットが低下します。

参考:

1,UARTの基礎