1 UART の概要

UART は、デバイス間の通信を可能にするキャラクター指向のユニバーサル データ リンクです。非同期送信とは、送信データに時計情報を付加する必要がないことを意味します。また、通信を成功させるためには、送信側と受信側のレート、ストップ ビット、パリティ ビットなどが同じである必要があります。

1.1 UART通信プロトコル

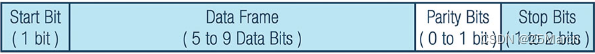

一般的な UART フレームはスタート ビットで始まり、有効なデータ、パリティ ビット (オプション)、最後にストップ ビットが続きます。

パケットフォーマットは以下の通りです

スタートビット

UART データ伝送ラインは、通常、データを送信していないときは高電圧レベルに保持されます。データの送信を開始するには、送信 UART が 1 クロック サイクルの間、送信ラインを High から Low にプルします。受信側 UART が High から Low への遷移を検出すると、ボー レートでデータ フレーム内のビットの読み取りを開始します。

データフレーム

データ フレームには、送信される実際のデータが含まれます。パリティ ビットが使用される場合、その長さは 5 ビットから 8 ビットになります。パリティ ビットを使用しない場合、データ フレームの長さは 9 ビットになります。

パリティビット

パリティは、数値がどの程度偶数であるか奇数であるかを表します。パリティ ビットは、受信側 UART が送信中にデータが変更されたかどうかを判断する方法です。電磁放射、ボーレートの不一致、または長時間のデータ送信によりビットが変化する可能性があります。

ストップビット

パケットの終わりを知らせるために、送信側 UART は 1 ~ 2 ビットの期間、データ ラインを Low から High に駆動します。

以下はボーレート:115200、データビット:8、パリティ:なし、ストップビット:1の波形です。

![[外部リンク画像の転送に失敗しました。ソース サイトにはリーチ防止メカニズムがある可能性があります。画像を保存して直接アップロードすることをお勧めします (img-guzeCjUf-1678431851237)(res/uart Waveform.png)]](https://img-blog.csdnimg.cn/dd076cf3caa9434fab37a75b2b988afb.png)

2 フロー制御

ストリーミングは主に、送信側と受信側の間の速度の不一致の問題を解決するために使用されます。受信側が受信したデータを処理できなくなった場合、送信側に受信を停止する信号を送信し、送信側はこの信号を受信後、送信を継続できる信号を受信するまで送信を停止します。フロー制御によりデータ送信の進行を制御できるため、データ損失を防ぐことができます。

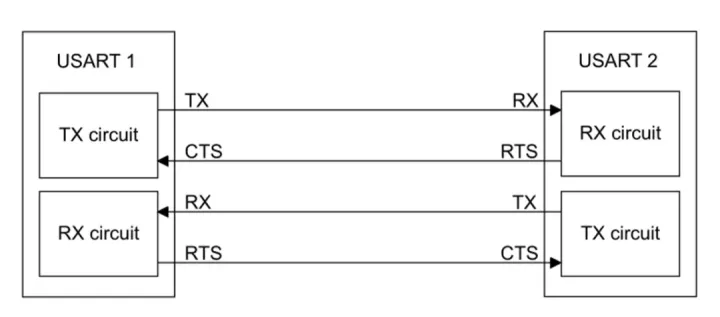

2.1 ハードウェアフロー制御

ハードウェア フロー制御には、RX と TX の他に 2 つの追加の制御ラインが必要です。1 つは CTS (Clear To Send) と呼ばれる入力信号であり、もう 1 つは RTS (Require To Send) と呼ばれる出力信号です。これら 2 つの回線のうち 1 つは制御を受信し、もう 1 つは制御を送信します。低レベルはデータを送信できることを示し、高レベルは送信側が待機する必要があることを示します。

2.2 ソフトウェアフロー制御

ソフトウェアフロー制御は、送信データに特殊文字 XON(0x11) および XOFF(0x13) を挿入して送信を制御します。XOFF を挿入してトランスミッタにデータ送信を強制的に停止させ、XON を挿入してトランスミッタにデータを送信させます。

2.3 相違点

| ハードウェアフロー制御 | ソフトウェアフロー制御 |

|---|---|

| ハードウェアには 2 本のワイヤを追加する必要があります | ハードウェアを変更する必要はありません |

| 転送をすぐに停止できる | 前のデータ送信が完了するまで待つ必要があるため、遅延が発生します |

| 悪用禁止 | 誤認識の可能性があります(受信データが制御文字と同じです) |

一般に、オーバーフローが発生する可能性がある環境では、ハードウェア フロー制御が推奨されます。

2.4 UART と TTL、RS232 の関係

UART は、ボー レート、フレーム フォーマット、ボー レート エラーなどのエンコード フォーマットを指定する規格にさらに注意を払います。これは指定されたプロトコルに似ています。RS232、TTL、RS485 などのシリアル通信インターフェイスは、インターフェイスのさまざまな電気的特性を定義します。たとえば、RS-232 はシングルエンド入出力であり、RS-485 は差動入出力ハードウェアです。

| TTL | RS232 | RS485 | |

|---|---|---|---|

| レベル信号 | レベル信号は5Vまたは3.3Vです | インターフェイスの信号レベルは比較的高く、プラスまたはマイナス 6 ~ 15 V が許容されます。 | ハイレベルとローレベルは最小差動電圧によって決まります |

| 転送方法 | 全二重 | 全二重 | 半二重 |

| 伝送距離 | 理論上は 10 フィート (5 m)、ノイズ耐性が低い | 最大 50 フィート (15 m) の通信距離 | 差動信号、理論上の通信距離は最大 1200 メートル |

チップの UART は通常 TTL レベルです。

2.5 USB to TTL シリアル チップ

実際の使用では、コンピュータの USB を使用して ESP32 の UART 周辺機器にアクセスします。その中間に、USB-to-TTL シリアル ポート チップが必要です。現在一般的なタイプは次のとおりです。表は、それらのさまざまな特性を比較しています:

| CP2102/2103 | CH340シリーズ | FT232R | PL2303HX | |

|---|---|---|---|---|

| メーカー | ケイ素 | 南京チンヘン | FDTI | 多産 |

| 最大レート | 1メートル | 2メートル | 3M | 12M |

| 少し | 5、6、7、8 | 5、6、7、8 | 7、8 | 5、6、7、8 |

| チェックデジット | 奇数/偶数/1/0/なし | 奇数/偶数/1/0/なし | 奇数/偶数/1/0/なし | 奇数/偶数/1/0/なし |

| ストップビット | 1、1.5、2 | 1、2 | 1、2 | 1、1.5、2 |

| ハードウェアフロー制御 | もつ | もつ | もつ | もつ |

| 安定 | 良い | 良い | 多くの | 違い |

| 価格 | 真ん中 | 低い | 高い | 低い |

現在の ESP32 シリーズ開発ボードのほとんどは CP2102 を統合しています。

3 ESP32 UART ハードウェア

現在の ESP32 シリーズ チップはすべて、複数の UART ペリフェラルを統合し、非同期通信 (RS232 および RS485) と IrDA をサポートしています。

異なるチップ間の UART の違いは次のとおりです。

| ESP32 | ESP32-S2 | ESP32-S3 | ESP32-C3 | ESP32-C2 | |

|---|---|---|---|---|---|

| UARTの数 | 3 | 2 | 3 | 2 | 2 |

| 最大通信速度 | 5Mbps | 5Mbps | 5Mbps | 5Mbps | 2.5Mbps |

| DMAをサポートするかどうか | はい | はい | はい | はい | いいえ |

AT 側のテストによると、Dupont ケーブルを使用すると実際の UART 通信速度の最大値は 2 Mbps に達します。それを超えるとデータがおかしくなります。より高い通信速度が必要な場合は、ケーブルを PCB から配線するのが最適です。 。

3.1 共通割り込み

| 割り込み名 | 序章 |

|---|---|

| UART_TX_DONE_INT | この割り込みは、トランスミッターが FIFO 内のすべてのデータを送信したときにトリガーされます。 |

| UART_RXFIFO_TOUT_INT | この割り込みは、レシーバーが UART_RX_TOUT_THRHD より長いバイトを受信したときにトリガーされます。 |

| UART_RXFIFO_OVF_INT | この割り込みは、レシーバーが FIFO に保存できる量を超えるデータを受信したときにトリガーされます。 |

| UART_FRM_ERR_INT | この割り込みは、受信機がデータ フレーム エラーを検出したときにトリガーされます。 |

| UART_PARITY_ERR_INT | この割り込みは、受信機がパリティ エラーを検出したときにトリガーされます。 |

| UART_TXFIFO_EMPTY_INT | この割り込みは、送信 FIFO 内のデータ量が UART_TXFIFO_EMPTY_THRHD で指定された値より少ない場合にトリガーされます。 |

| UART_RXFIFO_FULL_INT | この割り込みは、レシーバーが UART_RXFIFO_FULL_THRHD で指定されたデータを超えるデータを受信したときにトリガーされます。 |

| UART_WAKEUP_INT | この割り込みは、UART がウェイクアップされるときに生成されます。 |

| UART_BRK_DET_INT | この割り込みは、受信機がストップビットの後に NULL を検出するとトリガーされます。 |

ESP チップの UART RF FIFO と TX FIFO は RAM スペースの一部を共有します。IDF の実装では、RX FIFO と TX FIFO は互いに独立しており、長さは 128 バイトです。OVF のオーバーフロー割り込みは、受信が FIFO の最大値を超えた後にトリガーされます。

3.2 ESP-IDFの実装

現在、ESP-IDF は内部での読み取りと書き込みに UART RF FIFO を使用し、UART DMA は使用しません。ただし、UART ドライバーでは、TX FIFO と RX FIFO はそれぞれ対応するリングバッファーに接続されます。

- RX FIFO がデータを受信すると、データを RX リングバッファにスローし、UART_DATA イベントをトリガーします。

- TX のリングバッファは、アプリケーション層データを受信した後、TX FIFO へのデータの送信を開始します。

この期間中、現在の状態は UART イベント、および UART イベントと割り込みの対応によって識別されます。

| イベント | 割り込み | コメント |

|---|---|---|

| UART_DATA | 1. UART_RXFIFO_TOUT_INT 2. UART_RXFIFO_FULL_INT |

1. タイムアウト: 10 バイトの送信時間 2. フルしきい値: 120 バイト |

| UART_FIFO_OVF | UART_RXFIFO_OVF_INT | FIFO オーバーフローしきい値は 128 バイトです |

| UART_BUFFER_FULL | / | UART の初期 RX リングバッファ値がいっぱいです |

| UART_PATTERN_DET | UART_INTR_CMD_CHAR_DEF | AT の「+++」など、指定された数の特殊文字を受信します。 |

| UART_BREAK | UART_INTR_BRK_DEF | 受信しましたBREAK |

| UART_FRAME_ERR | UART_FRM_ERR_INT | |

| UART_PARITY_ERR | UART_PARITY_ERR_INT | |

| UART_DATA_BREAK | / | uart_write_bytes_with_breakデータ送信後にBREAKを送信する |

| UART_WAKEUP | UART_WAKEUP_INT |

注: BREAK 信号は、一定期間 (1 UART フレームより長い期間) 続くロー レベルです。

3.3 一般的な問題の分析

-

uart_read_bytesインターフェイスの呼び出しによって読み取られるデータの長さは、実際に送信されるデータよりも短い- ESP32 シリーズ チップは、FIFO を使用して UART データの読み取りおよび書き込みを行います。デフォルトでは、ブロック状態

uart_read_bytesを解除する送信長が 122 バイトを超える場合は、UART_READ インターフェイスを複数回呼び出す必要がある場合があります。読む

- ESP32 シリーズ チップは、FIFO を使用して UART データの読み取りおよび書き込みを行います。デフォルトでは、ブロック状態

-

UART の初期化中に設定された rx_buffer_size は明らかに非常に大きいですが、データ損失が発生します

- データ損失は、FIFO がいっぱいであることが原因で発生しますが、この時点では、データは時間内に rx バッファに転送されません。通常、UART_FIFO_OVF がトリガーされますが、このとき、フロー制御を追加するか、FULL_THRESH しきい値を下げることをお勧めします。

-

ESP32 がスリープ インターフェイスを呼び出した後、UART 通信が異常になります

- ESP32 UART は、80 MHz APB_CLK とリファレンス クロック REF_TICK の 2 つのクロック ソースをサポートします。APB_CLK はデフォルトで使用されており、このクロック ソースはスリープ中に動作を停止します。したがって、スリープをサポートする必要がある場合は、UART の初期化時に REF_TICK を設定する必要があります。このクロック ソースはボー レートでのみ実行できることに注意してください。 115200の。