目次

I.はじめに

DMA (Direct Memory Aaccess) ダイレクト メモリ アクセスとは、CPU の介入なしに 1 つのアドレス空間から別のアドレス空間にデータを直接コピーすることを意味し、周辺機器とメモリ間、またはメモリとメモリ間の高速データ転送を提供します。その役割は、大量のデータ転送のために CPU リソースが過剰に消費されるという問題を解決することです。DMA は多くの CPU リソースを節約し、CPU がより実際的な操作に集中できるようにします。

二、DMA送信対象

DAM の本質は、データの直接転送を実現することです。つまり、メモリのあるアドレス空間 (ソース) がメモリの別のアドレス空間 (宛先) に転送されます。サブジェクト間のデータ転送には、次の 4 つのタイプがあります。

- デスティネーション アドレス空間とソース アドレス空間の両方がシステム バス上にあります (メモリからメモリへ)。

- ソース アドレス空間はシステム バスであり、デスティネーション アドレス空間はペリフェラル バス (メモリからペリフェラル) です。

- ソース アドレス空間はペリフェラル バスであり、デスティネーション アドレス空間はシステム バス (ペリフェラルからメモリ) です。

- ソース アドレス空間はペリフェラル バスであり、デスティネーション アドレス空間はペリフェラル バス (ペリフェラルからペリフェラル) です。

3. S3c2440 の DMA

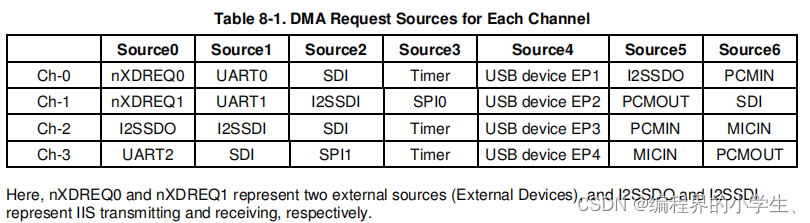

3.1 DMA 要求元

s3c2440 には 2 種類の DMA ソースがあり、1 つはソフトウェア トリガー (S/W - ソフトウェア) で、もう 1 つはハードウェア トリガー (H/W - ハードウェア) です。ハードウェア トリガーの場合、S3c2440 の 4 つの DMA チャネルでサポートされるリクエスト ソースは次のとおりです

。

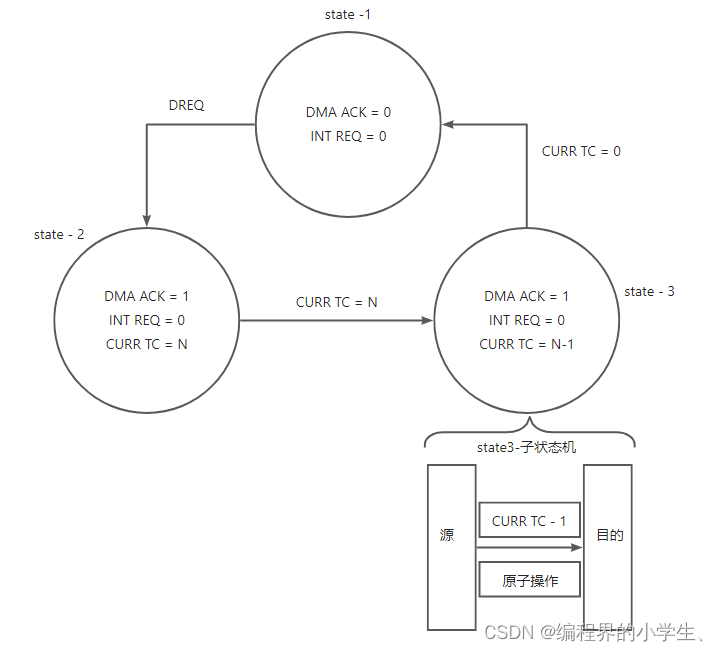

3.2 DMA ステートマシン

State-1: DMA は DMA 要求を待ちます。このとき、DMA ACK と INT REQ (DMA 割り込み) は 0 です。DMA が DMA 要求を受信すると、状態 2 に移行します。

ステート 2: DMA は DMA ACK を 1 に設定し、同時に CURR_TC を設定して DCON[19:0] レジスタからデータを読み出し、完了後にステート 3 にジャンプします。

状態 3: サブステート マシンを起動してアトミック操作を処理します。つまり、ソースからデータを読み取ってから宛先に書き込む操作を完了します。現時点では、シングル サービス モードとフル サービス モードについて議論する必要があります。シングル サービス モードでは、サブ有限ステート マシンがアトミック操作 CURR_TC - 1 を完了した後、メイン ステート マシンは DMA ACK を 0 に設定し、ステート 1 に戻り、次の DMA 要求を待ちます。フル サービス モードでは、サブステート マシンは CURR_TC が 0 になるまで実行され、次に INT REQ を 1 に、DMA ACK を 0 に設定し、状態 1 に戻って次の DMA 要求を待ちます。

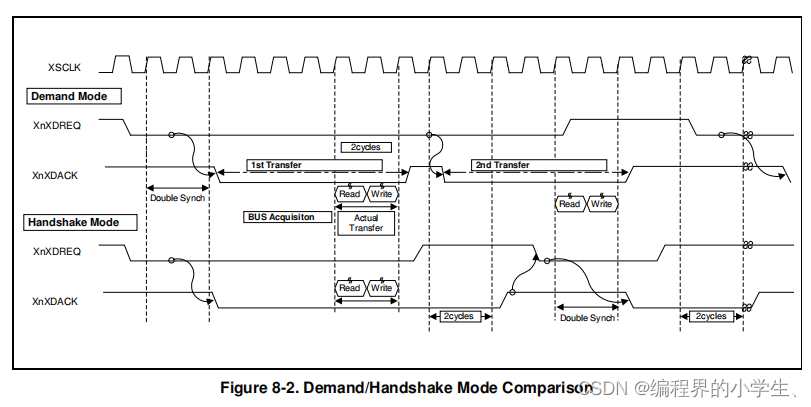

3.3 DMA リクエストモード

DCON レジスタによって設定されます。DMD_HS -> DCON[31]。

- デマンドモード

XnXDREQ が有効な場合、XnXDREQ が送信停止に失敗するまで直ちにデータ送信を継続し、次の XnXDREQ が有効になるのを待ちます。

- 握手モード

XnXDREQ が有効な場合、データ送信を実行します.この送信が完了した後、XnXDREQ の 2 サイクルの失敗を待つ必要があります.XnXDREQ に 2 サイクルの失敗がなければ、永遠に待機します.XnXDREQ が再度有効になった後のみ次のデータ転送を開始する前に、2 サイクルの障害が発生します。

3.4 DMA サービスモード

DCON レジスタによって設定されます。SERVMODE -> DCON[27]。

- サービス全体

フル サービス モードでは、サブステート マシンは CURR_TC が 0 になるまで実行され、次に INT REQ を 1 に、DMA ACK を 0 に設定し、状態 1 に戻って次の DMA 要求を待ちます。

- シングルサービス

シングル サービス モードでは、サブ有限ステート マシンがアトミック操作 CURR_TC - 1 を完了した後、メイン ステート マシンは DMA ACK を 0 に設定し、ステート 1 に戻り、次の DMA 要求を待ちます。

3.5 DMA 転送モード

DCON レジスタによって設定されます。TSZ -> DCON[28]。

- 独身

DMA 転送 (ステート 3 のサブステート マシン) は、1 回の読み取り/書き込み操作のみを実行します。

- 胸

1 回の DMA 転送 (ステート 3 のサブステート マシン) で 4 回の読み取り/書き込み動作が実行されます。

3.6 DMA 読み書きデータサイズ

DCON レジスタによって設定されます。DSZ -> DCON[21:20]。

1 回の読み取り / 書き込み操作で読み取られる / 書き込まれるバイト数。

00 = バイト 01 = ハーフワード

10 = ワード 11 = 予約済み

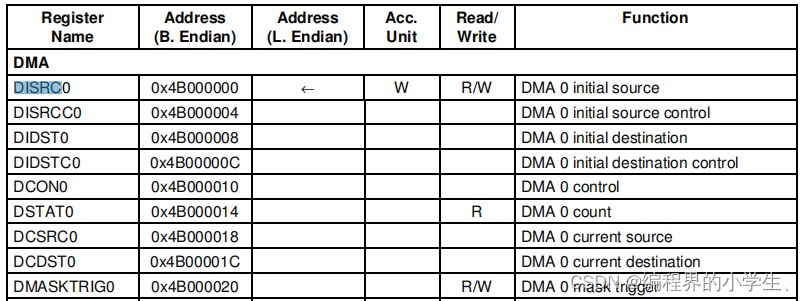

3.7 DMA レジスタ

3.7.1 DCON レジスタのその他の重要なビット

| DCONn | 少し | 説明 |

|---|---|---|

| 同期 | [30] | 0: DREQ と DACK のクロック同期ソースは PCLK (APB クロック) です。1: DREQ と DACK のクロック同期ソースは HCLK (AHB クロック) です。 |

| INT | [29] | DMA 割り込みを有効にする |

| HWSRCSEL | [26:24] | ハードウェア トリガー DMA ソース |

| SWHW_SEL | [23] | ソフトウェアトリガーまたはハードウェアトリガーを選択 |

| リロード | [22] | CURR_TC が 0 の場合に自動的にリロードするかどうかを構成する |

4. DMA の使用

4.1 ソフトウェアトリガ DMA

#include <linux/module.h>

#include <linux/kernel.h>

#include <linux/fs.h>

#include <linux/init.h>

#include <linux/delay.h>

#include <linux/irq.h>

#include <asm/uaccess.h>

#include <asm/irq.h>

#include <asm/io.h>

#include <asm/arch/regs-gpio.h>

#include <asm/hardware.h>

#include <linux/poll.h>

#include <linux/dma-mapping.h>

#define MEM_CPY_NO_DMA 0

#define MEM_CPY_DMA 1

#define BUF_SIZE (512*1024)

#define DMA0_BASE_ADDR 0x4B000000

#define DMA1_BASE_ADDR 0x4B000040

#define DMA2_BASE_ADDR 0x4B000080

#define DMA3_BASE_ADDR 0x4B0000C0

struct s3c_dma_regs {

unsigned long disrc;

unsigned long disrcc;

unsigned long didst;

unsigned long didstc;

unsigned long dcon;

unsigned long dstat;

unsigned long dcsrc;

unsigned long dcdst;

unsigned long dmasktrig;

};

static int major = 0;

static char *src;

static u32 src_phys;

static char *dst;

static u32 dst_phys;

static struct class *cls;

static volatile struct s3c_dma_regs *dma_regs;

static DECLARE_WAIT_QUEUE_HEAD(dma_waitq);

/* 中断事件标志, 中断服务程序将它置1,ioctl将它清0 */

static volatile int ev_dma = 0;

static int s3c_dma_ioctl(struct inode *inode, struct file *file, unsigned int cmd, unsigned long arg)

{

int i;

memset(src, 0xAA, BUF_SIZE);

memset(dst, 0x55, BUF_SIZE);

switch (cmd)

{

case MEM_CPY_NO_DMA :

{

for (i = 0; i < BUF_SIZE; i++)

dst[i] = src[i];

if (memcmp(src, dst, BUF_SIZE) == 0)

{

printk("MEM_CPY_NO_DMA OK\n");

}

else

{

printk("MEM_CPY_DMA ERROR\n");

}

break;

}

case MEM_CPY_DMA :

{

ev_dma = 0;

/* 把源,目的,长度告诉DMA */

dma_regs->disrc = src_phys; /* 源的物理地址 */

dma_regs->disrcc = (0<<1) | (0<<0); /* 源位于AHB总线, 源地址递增 */

dma_regs->didst = dst_phys; /* 目的的物理地址 */

dma_regs->didstc = (0<<2) | (0<<1) | (0<<0); /* 目的位于AHB总线, 目的地址递增 */

dma_regs->dcon = (1<<30)|(1<<29)|(0<<28)|(1<<27)|(0<<23)|(0<<20)|(BUF_SIZE<<0); /* 使能中断,单个传输,软件触发, */

/* 启动DMA */

dma_regs->dmasktrig = (1<<1) | (1<<0);

/* 如何知道DMA什么时候完成? */

/* 休眠 */

wait_event_interruptible(dma_waitq, ev_dma);

if (memcmp(src, dst, BUF_SIZE) == 0)

{

printk("MEM_CPY_DMA OK\n");

}

else

{

printk("MEM_CPY_DMA ERROR\n");

}

break;

}

}

return 0;

}

static struct file_operations dma_fops = {

.owner = THIS_MODULE,

.ioctl = s3c_dma_ioctl,

};

static irqreturn_t s3c_dma_irq(int irq, void *devid)

{

/* 唤醒 */

ev_dma = 1;

wake_up_interruptible(&dma_waitq); /* 唤醒休眠的进程 */

return IRQ_HANDLED;

}

static int s3c_dma_init(void)

{

if (request_irq(IRQ_DMA3, s3c_dma_irq, 0, "s3c_dma", 1))

{

printk("can't request_irq for DMA\n");

return -EBUSY;

}

/* 分配SRC, DST对应的缓冲区 */

src = dma_alloc_writecombine(NULL, BUF_SIZE, &src_phys, GFP_KERNEL);

if (NULL == src)

{

printk("can't alloc buffer for src\n");

free_irq(IRQ_DMA3, 1);

return -ENOMEM;

}

dst = dma_alloc_writecombine(NULL, BUF_SIZE, &dst_phys, GFP_KERNEL);

if (NULL == dst)

{

free_irq(IRQ_DMA3, 1);

dma_free_writecombine(NULL, BUF_SIZE, src, src_phys);

printk("can't alloc buffer for dst\n");

return -ENOMEM;

}

major = register_chrdev(0, "s3c_dma", &dma_fops);

/* 为了自动创建设备节点 */

cls = class_create(THIS_MODULE, "s3c_dma");

class_device_create(cls, NULL, MKDEV(major, 0), NULL, "dma"); /* /dev/dma */

dma_regs = ioremap(DMA3_BASE_ADDR, sizeof(struct s3c_dma_regs));

return 0;

}

static void s3c_dma_exit(void)

{

iounmap(dma_regs);

class_device_destroy(cls, MKDEV(major, 0));

class_destroy(cls);

unregister_chrdev(major, "s3c_dma");

dma_free_writecombine(NULL, BUF_SIZE, src, src_phys);

dma_free_writecombine(NULL, BUF_SIZE, dst, dst_phys);

free_irq(IRQ_DMA3, 1);

}

module_init(s3c_dma_init);

module_exit(s3c_dma_exit);

MODULE_LICENSE("GPL");

4.2 ハードウェア ソースが DMA をトリガーする

関連項目: 「Linux ドライバー: Audio Device Driver Framework-OSS を使用してオーディオ デバイス ドライバーをビルドする」