1. Introducción a los antecedentes

Los conjuntos de instrucciones se pueden dividir en dos tipos en esencia: conjunto de instrucciones complejas (computadora de conjunto de instrucciones complejas, CISC ) y conjunto de instrucciones reducido (computadora de conjunto de instrucciones reducido, RISC ). Los conjuntos de instrucciones complejos se caracterizan por la capacidad de lograr muchas cosas dentro de una sola instrucción.

La arquitectura del conjunto de instrucciones (abreviada como ISA) es la interfaz entre el software y el hardware. Los diferentes requisitos de la aplicación tendrán diferentes arquitecturas de instrucciones.

Lo inusual de RISC-V es que, a diferencia de casi todos los ISA anteriores, es modular. En su corazón hay un ISA base llamado RV32I que ejecuta una pila de software completa. RV32I es fijo y nunca cambiará. Esto proporciona un objetivo estable para los escritores de compiladores, desarrolladores de sistemas operativos y programadores de lenguaje ensamblador. La modularidad proviene de extensiones estándar opcionales que pueden o no estar incluidas en el hardware, según las necesidades de la aplicación. Esta modularidad hace que el RISC-V sea compacto y de bajo consumo energético.

2. Formato de instrucción RISC-V

Los conjuntos de instrucciones comunes de RISC-V se muestran en la siguiente tabla:

| conjunto de instrucciones básicas | significado |

| RV32I | Conjunto de instrucciones de enteros de 32 bits |

| RV32E | Subconjunto de RV32I para pequeños escenarios integrados |

| RV64I | Conjunto de instrucciones de enteros de 64 bits, compatible con RV32I |

| RV128I | Conjunto de instrucciones de enteros de 128 bits, compatible con RV64I y RV32I |

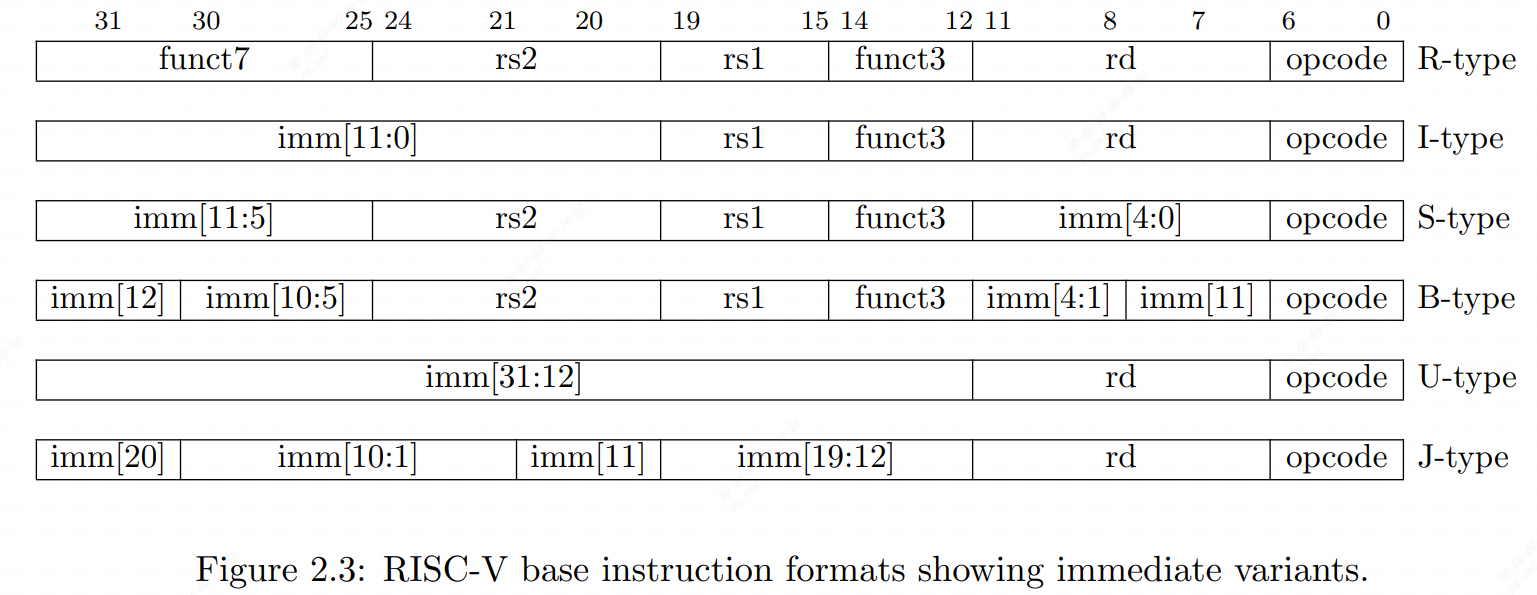

RISC-V tiene seis formatos básicos de instrucciones :

- Tipo R: para operaciones registro-registro

- Tipo I: utilizado para datos inmediatos breves y operaciones de carga de búsqueda

- Tipo S: utilizado para obtener operaciones de la tienda

- Tipo B: utilizado para operaciones de salto condicional

- Tipo U: para inmediatos largos

- Tipo J: para saltos incondicionales

Solo hay 6 formatos de instrucciones, y todas las instrucciones tienen una longitud de 32 bits, y los 7 bits inferiores de la instrucción se fijan como código de operación, lo que simplifica la decodificación de instrucciones. En RISC-V, para todas las instrucciones, el identificador del registro a leer y escribir siempre está en la misma posición, lo que significa que se puede acceder al registro antes de que se decodifique la instrucción.El campo inmediato de estos formatos siempre es signo extendido , y el bit de signo Siempre es el bit más alto en la instrucción, y la composición de varios tipos de instrucciones se muestra en la siguiente figura:

Significado del campo:

- opcode (código de operación): La operación básica de la instrucción, esta abreviatura es su nombre convencional.

- rd : registro de operación de destino, utilizado para almacenar los resultados de la operación.

- funct3 : un campo de código de operación adicional.

- rs1 : El primer registro de operando fuente.

- rs2 : Registro de operando de segunda fuente.

- funct7 : un campo de código de operación adicional.

- imm : valor inmediato

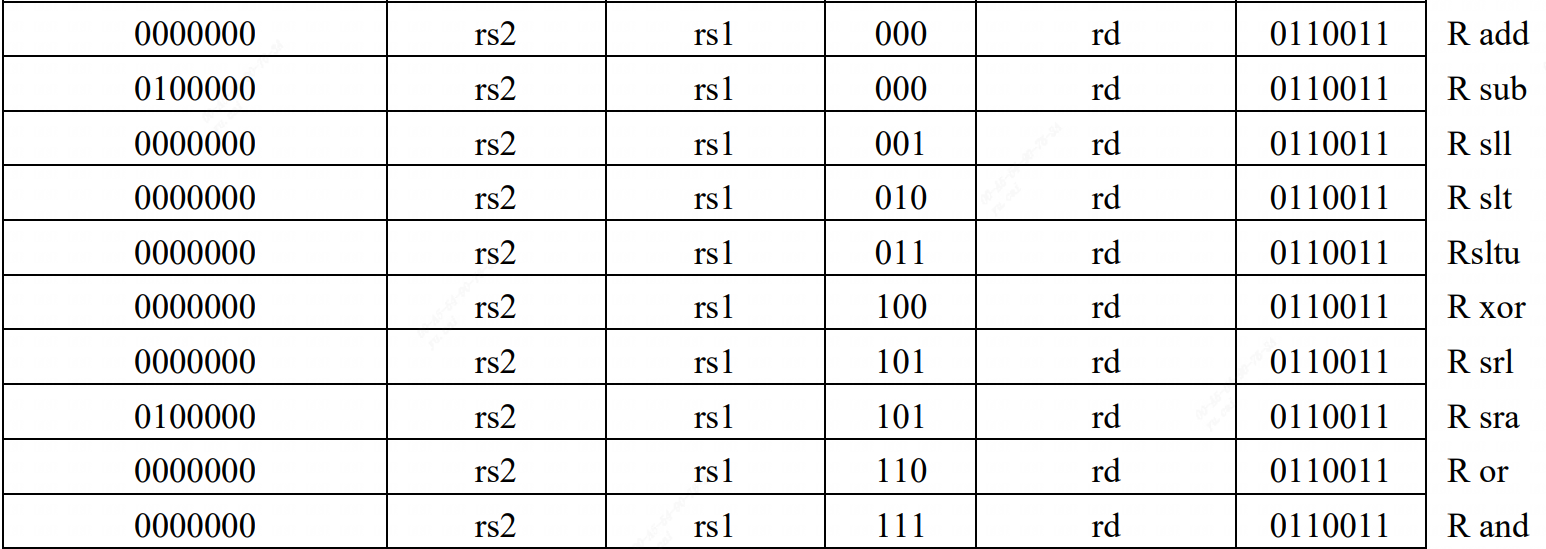

2.1 Comando tipo R

Las instrucciones de tipo R de 32 bits incluyen 6 partes:

- opcode es el código de operación, el ancho de bits es de 7 bits, en el 0-6 bits de la instrucción;

- rd (Registro de destino) es el registro de destino, con un ancho de bit de 5 bits, en los 7-11 bits de la instrucción;

- funct3+funct7 son dos campos de operación. funct3 ocupa 3 bits, funct7 ocupa 7 bits;

- rs1 (Source Register 1) es el primer registro de operando fuente, con un ancho de bit de 5 bits, en los 15-19 bits de la instrucción;

- rs2 (Registro fuente 2) es el segundo registro de operando fuente, con un ancho de bit de 5 bits, en los 25-31 bits de la instrucción.

El comando de tipo R se compone de la siguiente manera:

Todas las instrucciones para el tipo R (RV32I)

Las instrucciones de tipo R incluyen sumas, restas, operaciones lógicas y operaciones de cambio.

示例:

add a0, a1, a2 //a0 = a1 + a2

sub a0, a1, a2 //a0 = a1 - a2

sll a0, a1, a2 //a0 = a1 << a2(低位补0)

srl a0, a1, a2 //a0 = a1 >> a2(高位补0)

sra a0, a1, a2 //a0 = a1 >> a2 (算术右移,高位补原来的符号位)

slt a0, a1, a2 //a1 < a2 ? a0 = 1 : a0 = 0

xor a0, a1, a2 //a0 = a1 ^ a2

or a0, a1, a2 //a0 = a1 | a2

and a0, a1, a2 //a0 = a1 & a22.2 Instrucciones tipo I

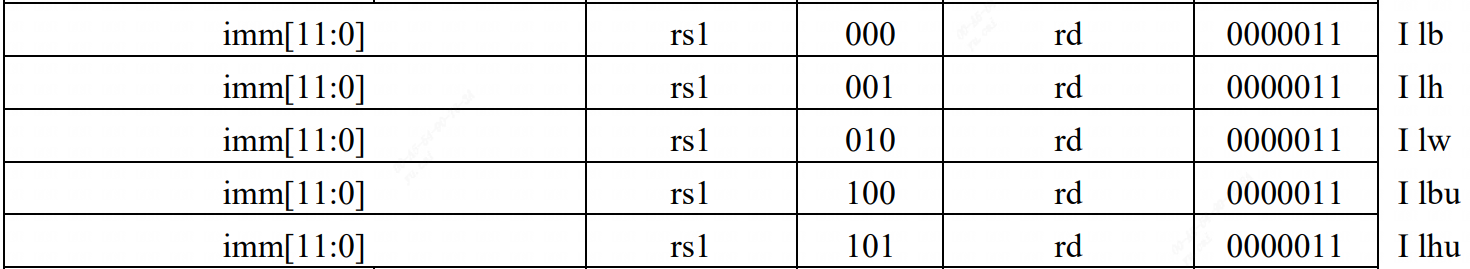

Las directivas de tipo I constan de 5 partes:

- opcode es el código de operación, el ancho de bits es de 7 bits, en el 0-6 bits de la instrucción;

- rd (Registro de destino) es el registro de destino, con un ancho de bit de 5 bits, en los 7-11 bits de la instrucción;

- funct3 es el campo de operación. funct3 ocupa 3 bits, en los 12-14 bits de la instrucción;

- rs1 (Source Register 1) es el primer registro de operando fuente, que ocupa 5 bits, en los 15-19 bits de la instrucción;

- Almacene el valor inmediato de 12 bits - imm[11:0], en los 20-31 bits de la instrucción.

Las instrucciones de tipo I se estructuran de la siguiente manera:

Todas las instrucciones para Tipo I (RV32I)

Las instrucciones de tipo I incluyen operaciones inmediatas e instrucciones de carga.

示例:

addi a0, a1, 0x5 //a0 = a1 + 0x5

subi a0, a1, 0x05 //a0 = a1 - 0x05

slli a0, a1, 0x05 //a0 = a1 << 0x05(低位补0)

srli a0, a1, 0x05 //a0 = a1 >> 0x05(高位补0)

srai a0, a1, 0x05 //a0 = a1 >> 0x05 (算术右移,高位补原来的符号位)

slti a0, a1, 0x05 //a1 < 0x05 ? a0 = 1 : a0 = 0

xori a0, a1, 0x05 //a0 = a1 ^ 0x05

ori a0, a1, 0x05 //a0 = a1 | 0x05

andi a0, a1, 0x05 //a0 = a1 & 0x05

示例:

lb x10, 0(x1) //将x1的值加上0,将这个值作为地址, 取出这个地址所对应的内存中的值, 将这个值赋值给x10(取出的是8位数值)

lh x10, 0(x1) //从内存中取出16位数值

lw x10, 0(x1) //从内存中取出32位数值

lbu x10, 0(x1) //从内存中取出8位无符号数值

lhu x10, 0(x1) //从内存中取出16位无符号数值

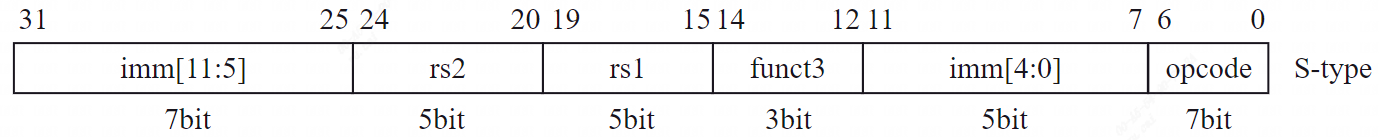

2.3 Comando tipo S

El comando Type S consta de 6 partes:

- opcode es el código de operación, el ancho de bits es de 7 bits, en el 0-6 bits de la instrucción;

- inm[4:0]+inm[11:5];

- funct3 es el campo de operación. funct3 ocupa 3 bits, en los 12-14 bits de la instrucción;

- rs1 (Source Register 1) es el primer registro de operando fuente, que ocupa 5 bits, en los 15-19 bits de la instrucción;

- rs2 (Source Register 2) es el segundo registro de operando fuente, que ocupa 5 bits, en los 25-31 bits de la instrucción.

El comando tipo S se compone de la siguiente manera:

Todos los comandos para tipo S (RV32I)

Las instrucciones de tipo S incluyen instrucciones de la tienda.

示例:

sb x10, 0(x1) //x1的值加上0,将这个值作为地址, 将x10的值存储到上述地址所对应的内存中去 (只会将x10的值的低8位写入)

sh x10, 0(x1) //只会将x10的值的低16位写入

sw x10, 0(x1) //只会将x10的值的低32位写入2.4 Comandos tipo B

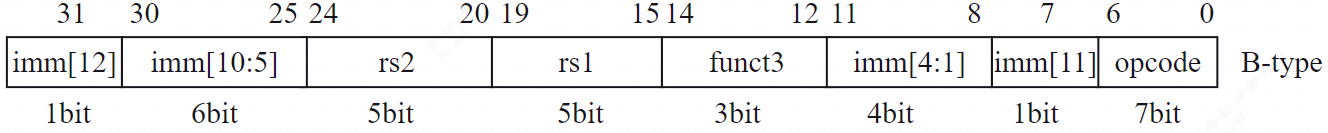

Las instrucciones de tipo B constan de 6 partes:

- opcode es el código de operación, el ancho de bits es de 7 bits, en el 0-6 bits de la instrucción;

- imm[4:1]+imm[11]+imm[10:5]+imm[12]; (Nota: imm[0] se descarta porque siempre es cero)

- funct3 es el campo de operación. funct3 ocupa 3 bits, en los 12-14 bits de la instrucción;

- rs1 (Source Register 1) es el primer registro de operando fuente, que ocupa 5 bits, en los 15-19 bits de la instrucción;

- rs2 (Source Register 2) es el segundo registro de operando fuente, que ocupa 5 bits, en los 25-31 bits de la instrucción.

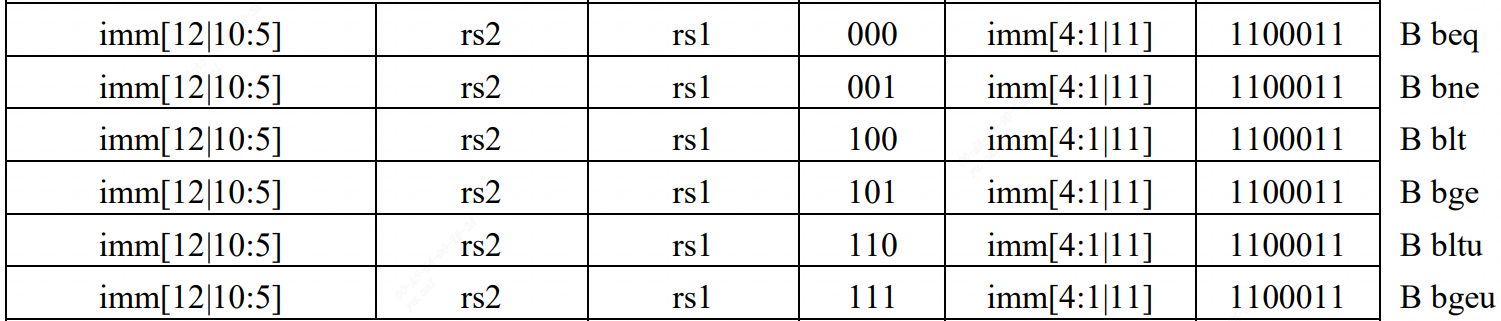

Los comandos de tipo B están estructurados de la siguiente manera:

Todas las instrucciones para el tipo B (RV32I)

Las instrucciones de tipo B incluyen instrucciones de salto condicional.

示例:

beq a1,a2,Label //if(a1==a2){goto Label;}

bne a1,a2,Label //if(a1!=a2){goto Label;}

blt a1,a2,Label //if(a1< a2){goto Label;}

bgt a1,a2,Label //if(a1> a2){goto Label;}

bge a1,a2,Label //if(a1<=a2){goto Label;}

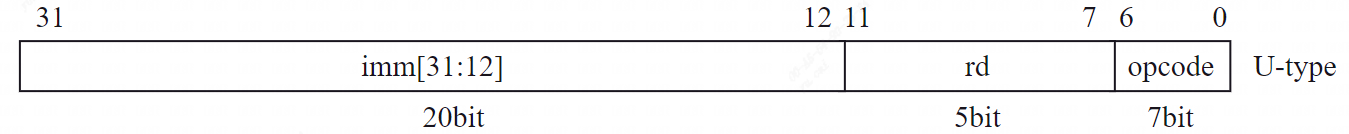

ble a1,a2,Label //if(a1>=a2){goto Label;}2.5 Comando en forma de U

La instrucción U consta de 3 partes:

- opcode es el código de operación, el ancho de bits es de 7 bits, en el 0-6 bits de la instrucción;

- rd (Registro de Destino) es el registro de destino, ocupando 5 bits, en los 7-11 bits de la instrucción;

- imm[31:12]: almacena el valor inmediato de los 20 bits superiores—imm[31:12], en los 12-31 bits de la instrucción.

La instrucción en forma de U se compone de la siguiente manera:

Comando completo de tipo U (RV32I)

示例:

lui x10, 0x65432 //得到立即数的高20位,低位补0,立即数范围为:0x00~0xFFFFF2.6 Comando tipo J

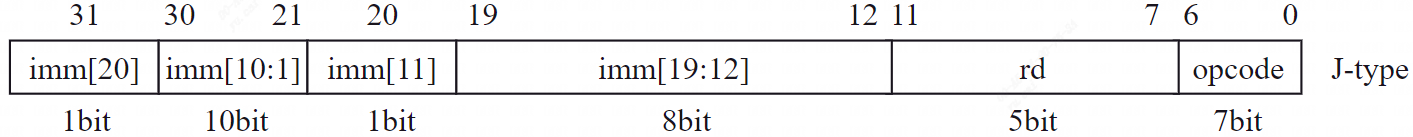

La instrucción tipo J consta de 3 partes:

- opcode es el código de operación, el ancho de bits es de 7 bits, en el 0-6 bits de la instrucción;

- rd (Registro de Destino) es el registro de destino, ocupando 5 bits, en los 7-11 bits de la instrucción;

- División inmediata: imm[19:12]+imm[11]+imm[10:1]+imm[20]:

El comando tipo J se compone de la siguiente manera:

Todas las instrucciones para el tipo J (RV32I)

示例:

jal ra, symbol // 跳转到Symbol中去, 并把ra设置成返回地址 Symbol 可以是自定义的Label ,也可以是某个函数名

jal ra, 100 // 跳转到pc + 100 * 2的地方中去, 并把ra设置成返回地址 pc相对寻址,对应的是位置无关代码(PIC)

jalr ra, 40(x10) // 跳转到x10+40 的地方中去, 并把ra设置成返回地址x10+40必须是绝对地址,指向内存中某个确定的地方(往往是函数的开头),非PIC3. Registros de propósito general

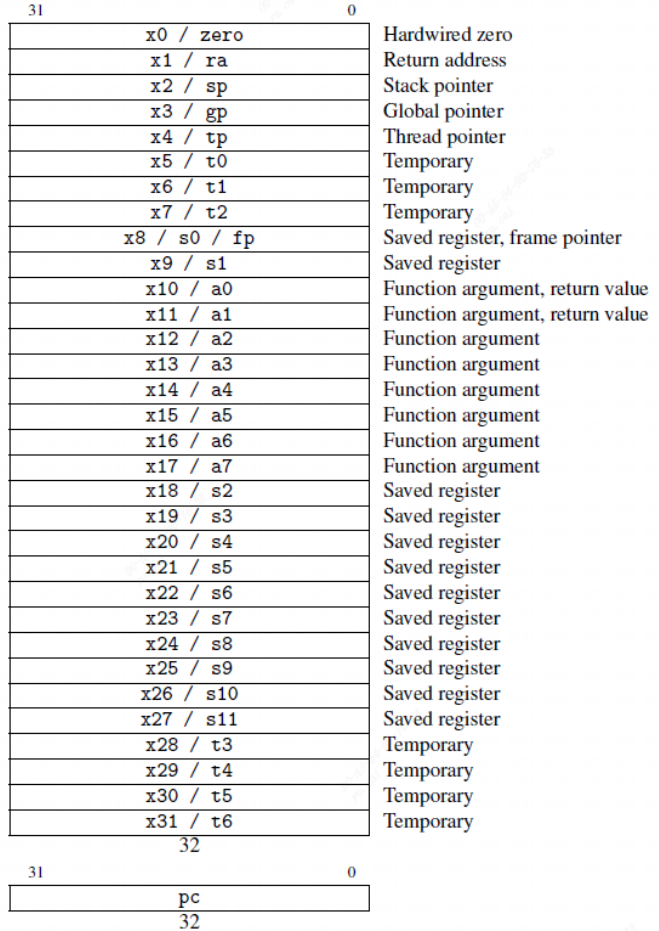

RV32I tiene 32 registros de uso general y un registro de PC. Hay un registro x0 cuyo valor se establece en 0 por hardware

Nota: Los 32 registros x0~x31 de RISC-V están representados por los números 0~31.

Documentos de referencia, blogs:

Documento oficial RISC-V

Los conceptos básicos del conjunto de instrucciones riscv - blog de konghhhhh - blog de CSDN

RISC-V instrucción set_riscv instrucción set_Lighting master~'s blog-CSDN blog