el pensamiento de diseño

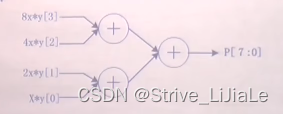

"Agregar después del turno", la operación de suma toma la forma de un árbol sumador.

Proceso de operación de multiplicación: multiplique cada bit del multiplicando y el multiplicador, porque debe cambiarse, multiplíquelo por el peso correspondiente para lograr, por ejemplo, multiplicar el número binario por la primera potencia de 2 puede realizar el cambio total de uno bit (use en el código Extender 0, haga un cambio). Finalmente, los resultados obtenidos se suman para obtener el resultado final de la multiplicación.

Diseño HDL de Verilong

module mul_addtree(mul_a,mul_b,mul_out);

input [3:0] mul_a,mul_b; //IO declaration,a:乘数 b:被乘数

output [7:0] mul_out;

wire [7:0] mul_out; //Wire declaration

wire [7:0] stored0,stored1,stored2,stored3;

wire [7:0] add01,add23;

assign

stored3 = mul_b[3]?{1'b0,mul_a,3'b0}:8'b0;

assign

stored2 = mul_b[2]?{2'b0,mul_a,2'b0}:8'b0;

assign

stored1 = mul_b[1]?{3'b0,mul_a,1'b0}:8'b0;

assign

stored0 = mul_b[0]?{4'b0,mul_a}:8'b0;

assign

add01 = stored1 + stored0;

assign

add23 = stored3 + stored2;

assign

mul_out = add01 + add23;

endmodule

//----------testbench----------

module mult_addtree_tb;

reg [3:0]mult_a;

reg [3:0]mult_b;

wire [7:0]mult_out;

mul_addtree U1(.mul_a(mult_a),.mul_b(mult_b),.mul_out(mult_out)); //moudule instance

initial //Stimull signal

begin

mult_a = 0 ; mult_b = 0;

repeat(9)

begin

#20 mult_a = mult_a + 1;

mult_b = mult_b + 1;

end

end

endmoduleEstructura de tubería

En la figura se muestra la estructura de árbol sumador de canalización de dos etapas del multiplicador de 4 bits. Al insertar grupos de flip-flop D entre los sumadores de primera y segunda etapa, segunda y tercera etapa, se obtiene un sumador de dos etapas. el diseño de la tubería se puede realizar.

module mul_addtree_2_stage(clk,clr,mul_a,mul_b,mul_out);

input clk,clr;

input [3:0] mul_a,mul_b; //IO declaration,a:乘数 b:被乘数

output [7:0] mul_out;

reg [7:0] add_tmp_1,add_tmp_2,mul_out; //Wire declaration

wire [7:0] stored0,stored1,stored2,stored3;

assign

stored3 = mul_b[3]?{1'b0,mul_a,3'b0}:8'b0;

assign

stored2 = mul_b[2]?{2'b0,mul_a,2'b0}:8'b0;

assign

stored1 = mul_b[1]?{3'b0,mul_a,1'b0}:8'b0;

assign

stored0 = mul_b[0]?{4'b0,mul_a}:8'b0;

always@(posedge clk or negedge clk) //Timing control

begin

if(!clr) begin

add_tmp_1 <= 8'b0000_0000;

add_tmp_2 <= 8'b0000_0000;

mul_out <= 8'b0000_0000;

end

else begin

add_tmp_1 <= stored3 + stored2;

add_tmp_2 <= stored1 + stored0;

mul_out <= add_tmp_1 + add_tmp_2;

end

end

endmodule

//----------testbench----------

module mult_addtree_2_stag_tb;

reg clk,clr;

reg [3:0]mult_a;

reg [3:0]mult_b;

wire [7:0]mult_out;

mul_addtree_2_stage U1(.mul_a(mult_a),.mul_b(mult_b),.mul_out(mult_out),.clk(clk),.clr(clr));

initial //Stimull signal

begin

clk = 0,clr = 0, mult_a = 0 ; mult_b = 0;

# 5 clr = 1;

end

always #10 clk = ~clk;

initial

begin

repeat(5)

begin

#20 mult_a = mult_a + 1; mult_b = mult_b + 1;

end

end

endmodule