19. Diseño de amplificador de potencia clase F de banda estrecha del registro de uso de ADS

Basado en CGH40010F

Hablando antes:

el blogger también es nuevo en RF PA y tiene muchas preguntas al escribir este amplificador de potencia de clase F. Aparte de la clase F continua, la clase F continua extendida, la clase F continua extendida de alto orden y la clase F continua extendida híbrida de alto orden, muchas personas diseñan (consulte los documentos) no lo que imaginé para los amplificadores de potencia de clase F de banda estrecha ordinarios: P1. En algunos documentos, los amplificadores de potencia de clase F de frecuencia de un solo punto extraen múltiples armónicos. ¿No está ya determinada la condición de impedancia de la clase F (refiriéndose a circuito abierto y cortocircuito)

?

P2 En algunos documentos, la red de control de armónicos no considera los efectos de empaquetado y parásitos, y la forma de onda de voltaje no es cuadrada en absoluto, es decir, la condición de impedancia no cumple con la Clase F convencional, aunque la eficiencia puede no ser baja.

Así que siento que siempre que se controlen los armónicos, se puede considerar como una categoría F generalizada. No sé si este entendimiento es correcto. Cualquiera que entienda puede responder en el área de comentarios.

0. Descarga del archivo fuente

https://download.csdn.net/download/weixin_44584198/85550957

1. Indicadores de diseño y resultados reales

Frecuencia central: 2,4 Ghz

Potencia de salida: 10 W (40 dbm)

Pérdida de retorno: menos de -15 db

Eficiencia de drenaje: más del 75 %

TOI/IP3: -45 dbm

2. Análisis del cuadernillo de datos

He comenzado a hacer ultra banda ancha, ¿qué libro de datos debo leer?

Extra 1: Parámetros importantes de los transistores amplificadores de potencia de RF

3. Análisis DC + selección del punto de trabajo estático

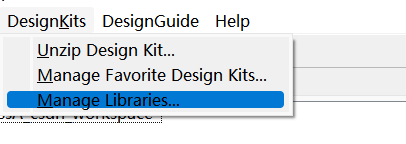

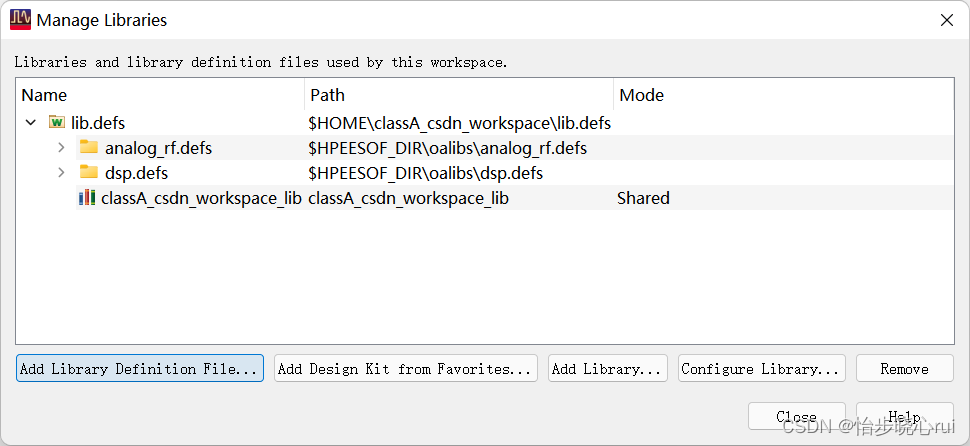

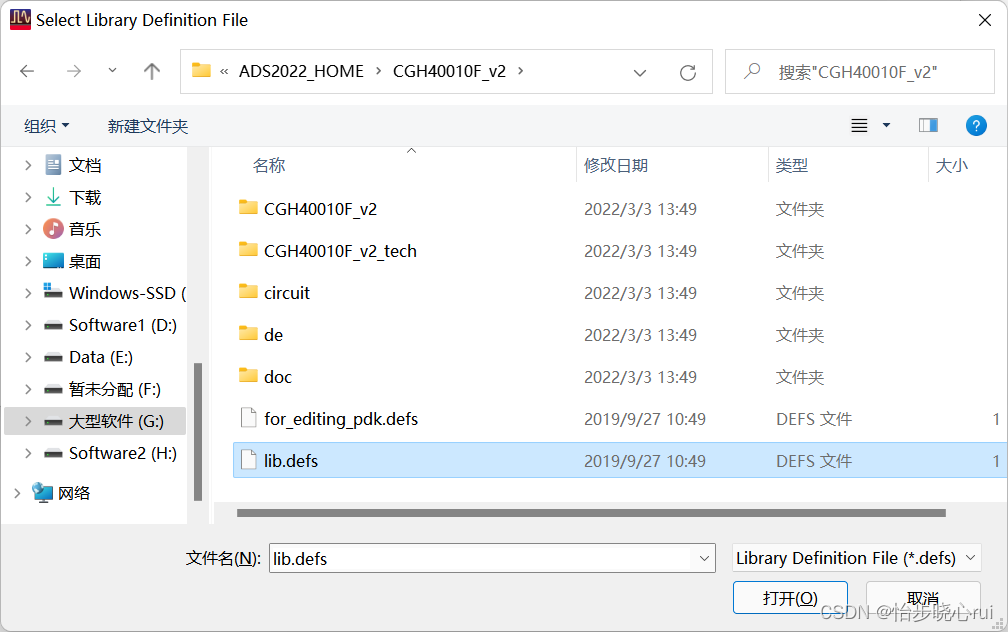

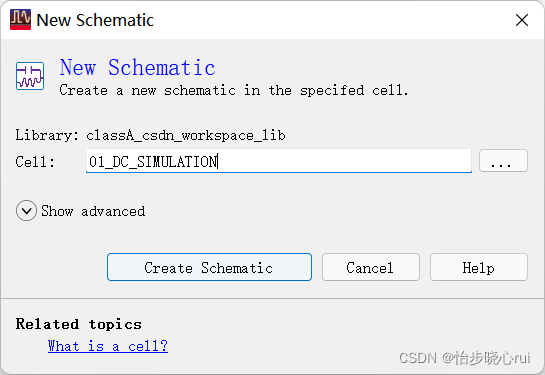

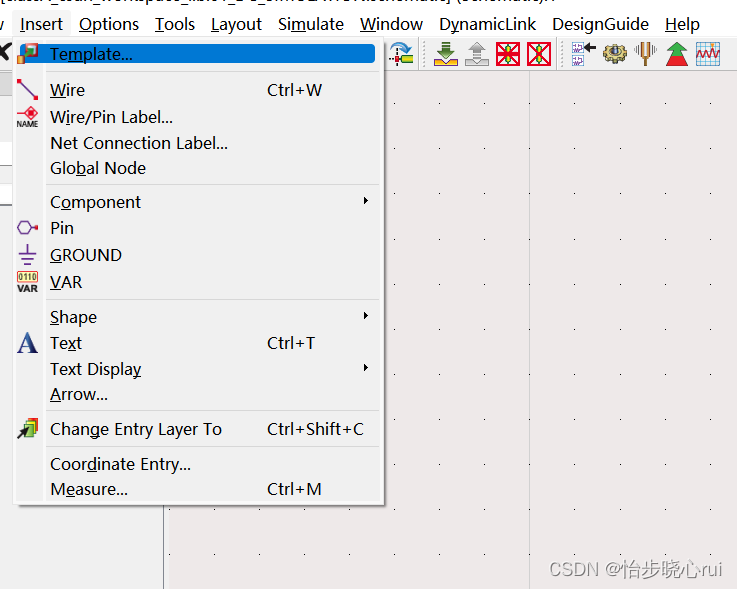

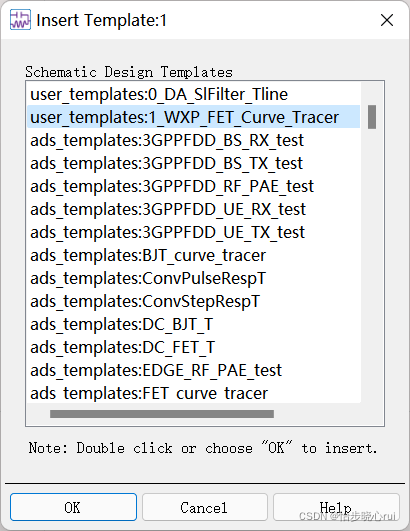

Importe el archivo modelo CGH40010F, elija descomprimir el kit de diseño por primera vez, si no es la primera vez, puede optar por administrar el archivo de la biblioteca, no soy la primera vez que use aquí: Elija agregar el archivo de definición de la biblioteca: Buscar el archivo DEFS en el directorio raíz del modelo de descompresión, haga clic para abrir la biblioteca de importación: el nuevo esquemático se menciona 01_DC_simulación (este schematic es utilizar la barra) para que use la barra) para que use la barra de la barra de importación) e

inserte

la

plantilla

:

Insertado aquí está mi plantilla personalizada:

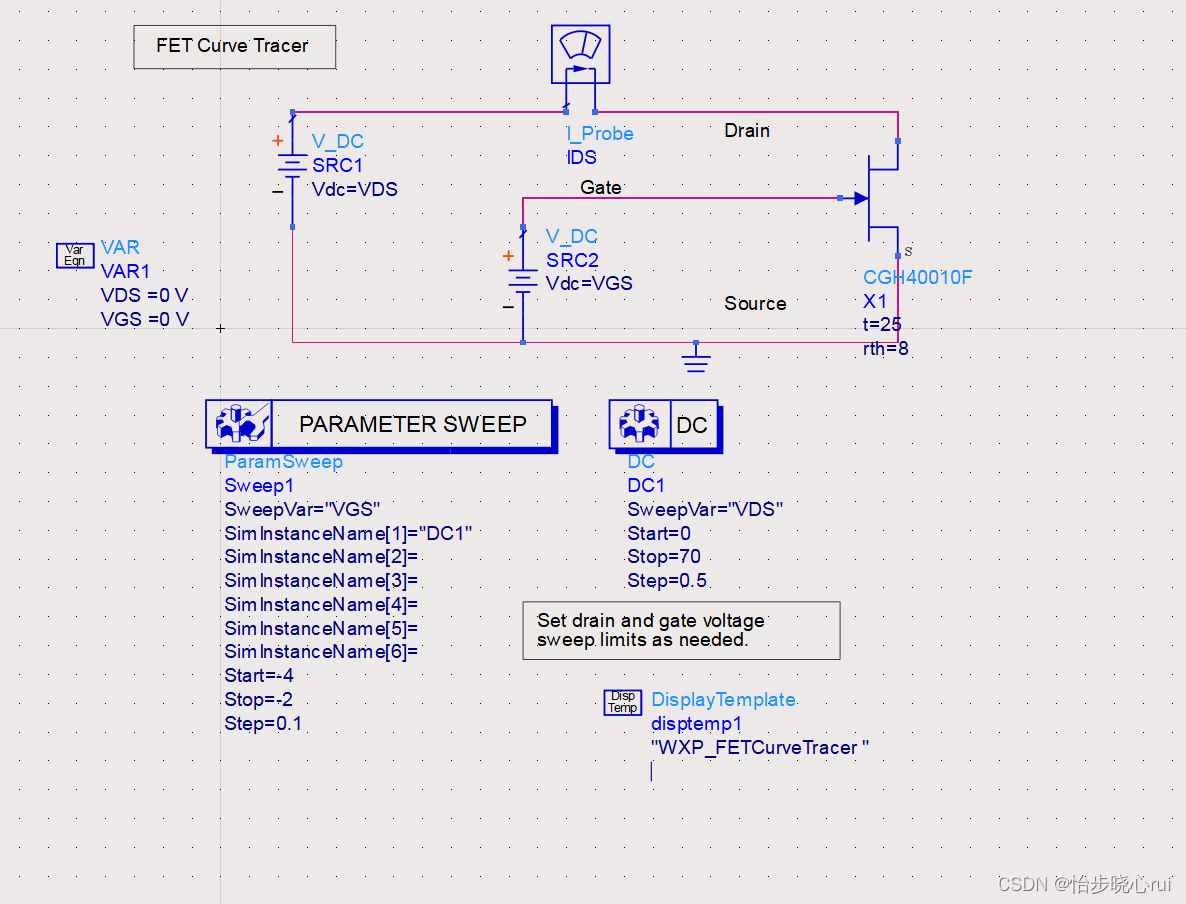

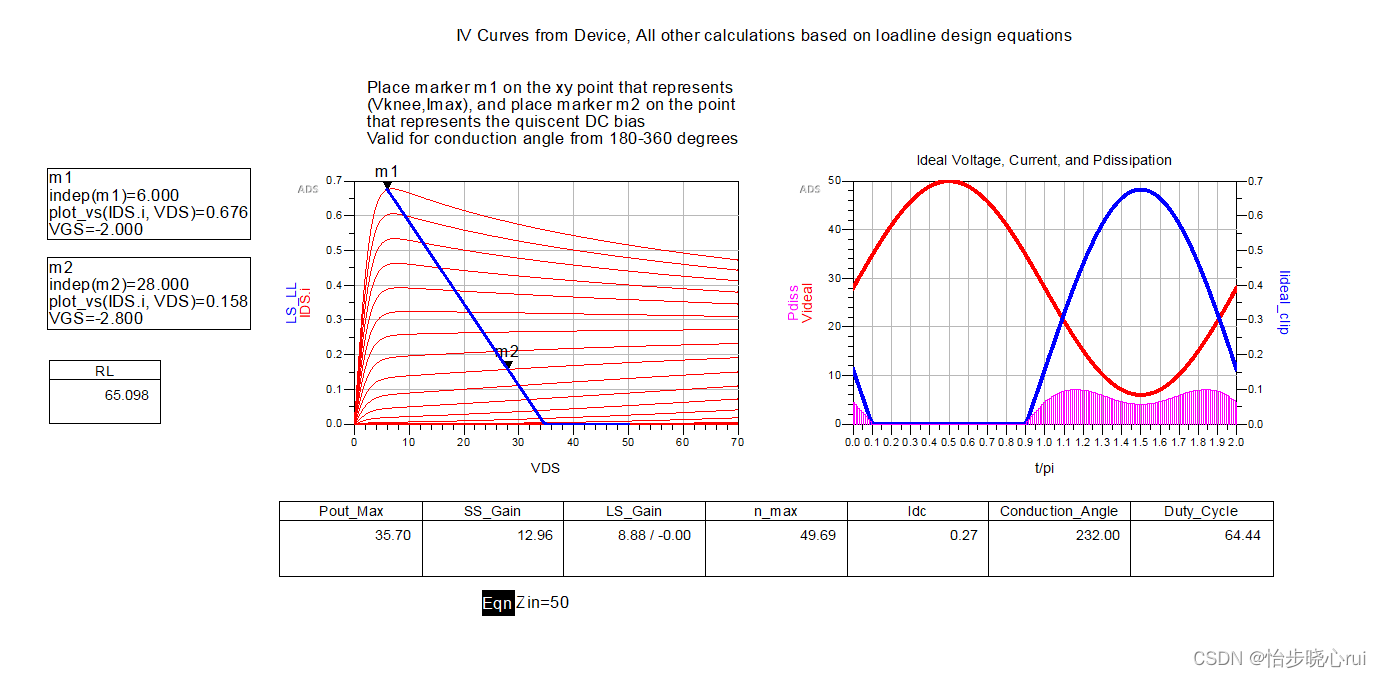

Después de la inserción, es como sigue (generalmente, el voltaje correspondiente debe configurarse de acuerdo con la hoja de datos al insertar una plantilla, y la plantilla insertada aquí ya se ha configurado, por ejemplo, los parámetros de barrido de frecuencia aquí): haga clic directamente en el resultado de la observación de la simulación: mueva la marca relevante en esta interfaz de selección de datos para cambiar el estado de funcionamiento del circuito, aquí seleccione el voltaje de drenaje 28V, voltaje de puerta

-2.8V

. Se puede ver claramente en la figura que el ángulo de conducción en este momento es de 232 grados, y la máxima eficiencia de trabajo puede alcanzar casi el 50 % según el diseño del modo de clase AB.

4. Análisis de estabilidad

Cree un nuevo esquema, asígnele el nombre 02_STABILITY_SIMULATION e inserte el control de análisis de estabilidad:

Se simula el diagrama esquemático y se obtienen los resultados, se puede observar que el sistema de circuito estable se puede estabilizar en la banda de frecuencia:

5. Diseño de red de control de armónicos

Sabemos que la característica más obvia del amplificador de potencia de clase F es su control de armónicos. En términos generales, el amplificador de potencia de clase F necesita abrir el circuito para armónicos impares y cortocircuitar para armónicos pares. Por lo tanto, necesitamos diseñar esta red de control de armónicos antes de tirar de la carga.

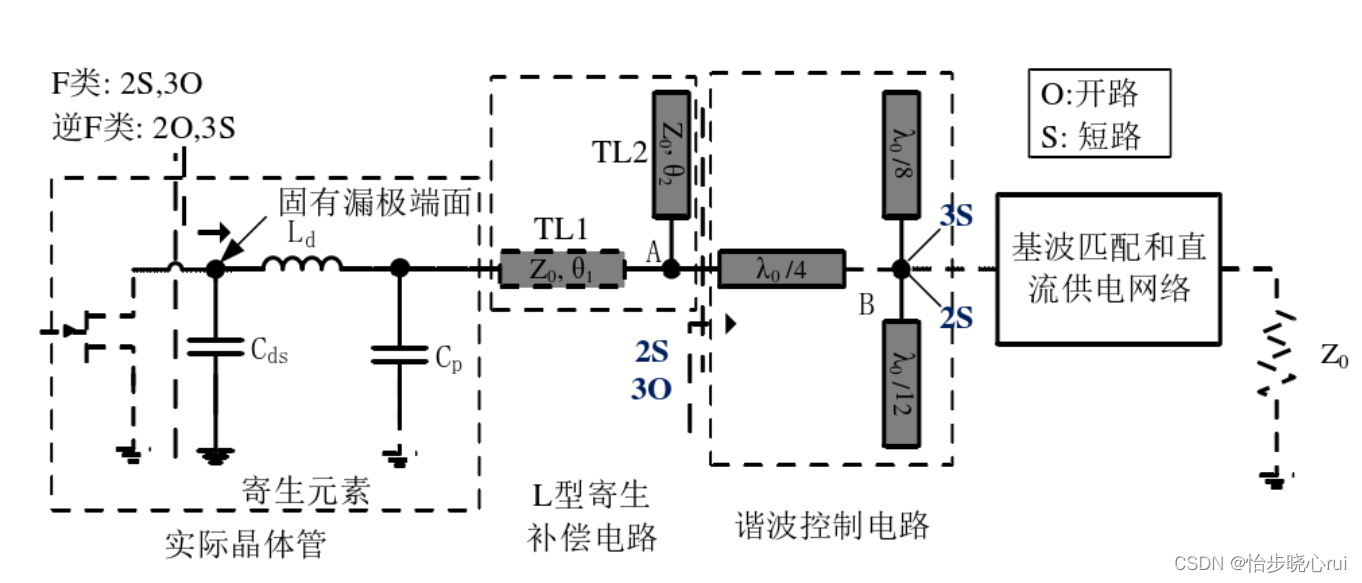

La red de control de armónicos adopta la siguiente forma estructural:

Analice el circuito anterior:

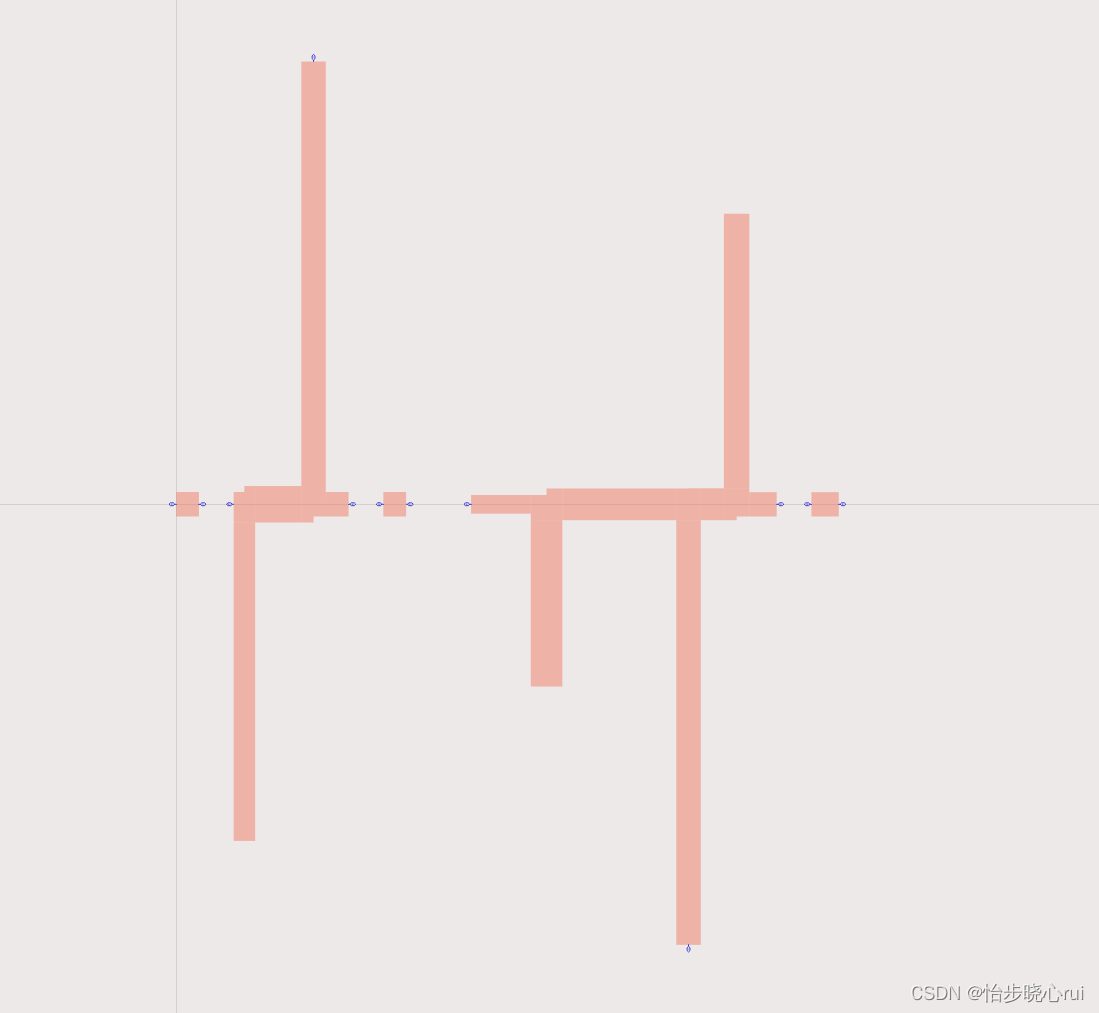

construya el diagrama de circuito anterior en ADS, use componentes de línea microstrip ideales:

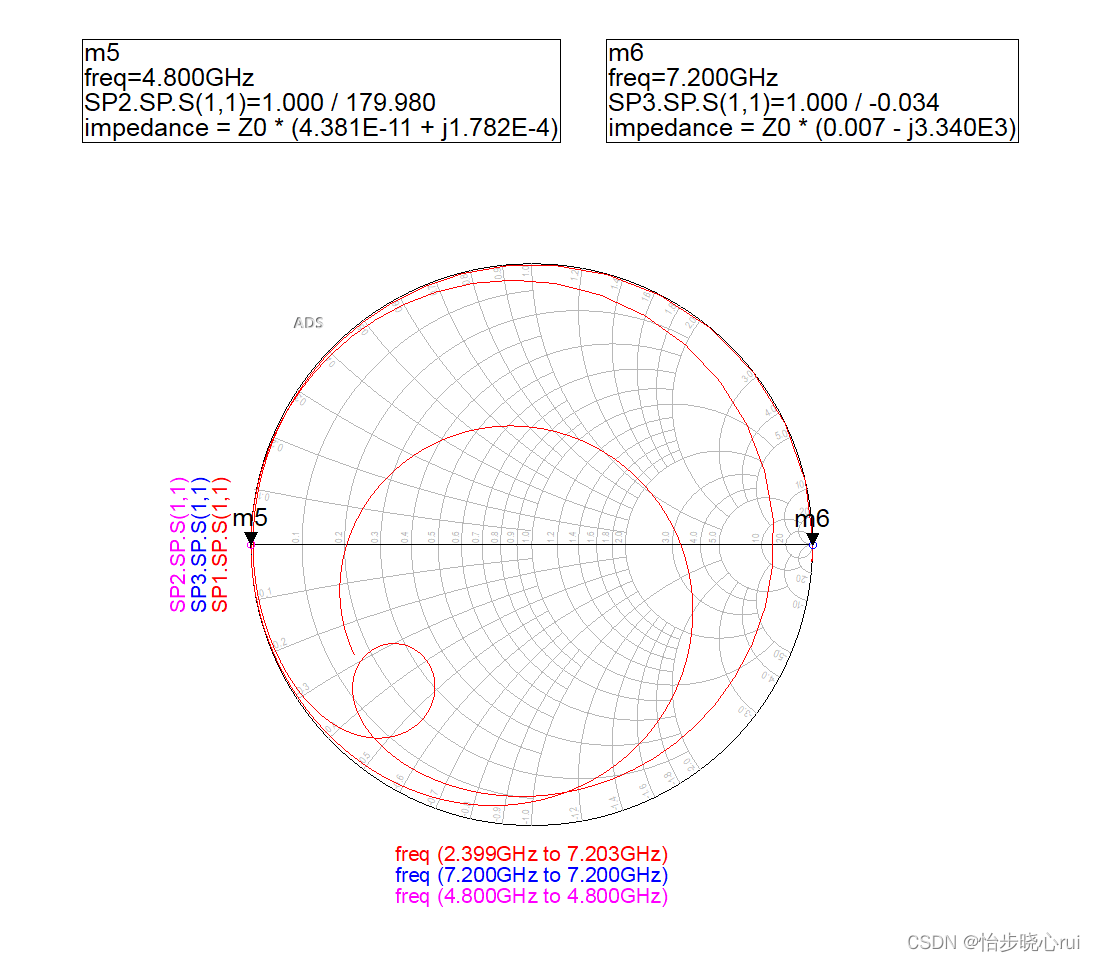

simule el diagrama esquemático, observe los resultados y descubra que está en cortocircuito para armónicos pares y en circuito abierto para armónicos impares, que cumple con las condiciones de impedancia (tenga en cuenta que aquí solo se controla el tercer armónico):

6. (Expansión) Red de control de armónicos considerando efectos parásitos

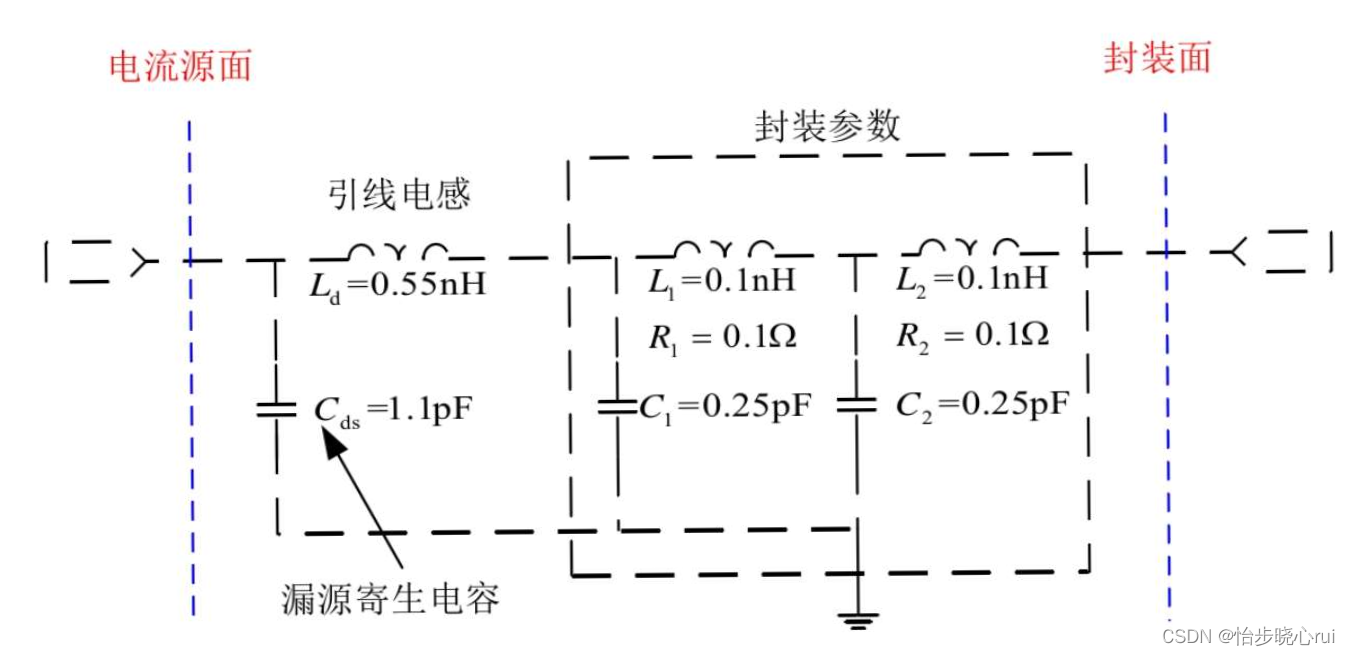

上述所设计的谐波控制电路没有考虑到封装效应和寄生效应,针对此次使用的管子,网上有一套现成的封装模型,添加后如下所示(一堆电感电容就是其封装模型):

此处给出更加清晰明了的解释:

此处使用高效率GaN HEMT F类/逆F类功率放大器研究和设计(知网)文章中的简化模型(与完备的寄生和封装等效模型相比少了一个T型结构,谐波控制电路略有不同但是原理相似):

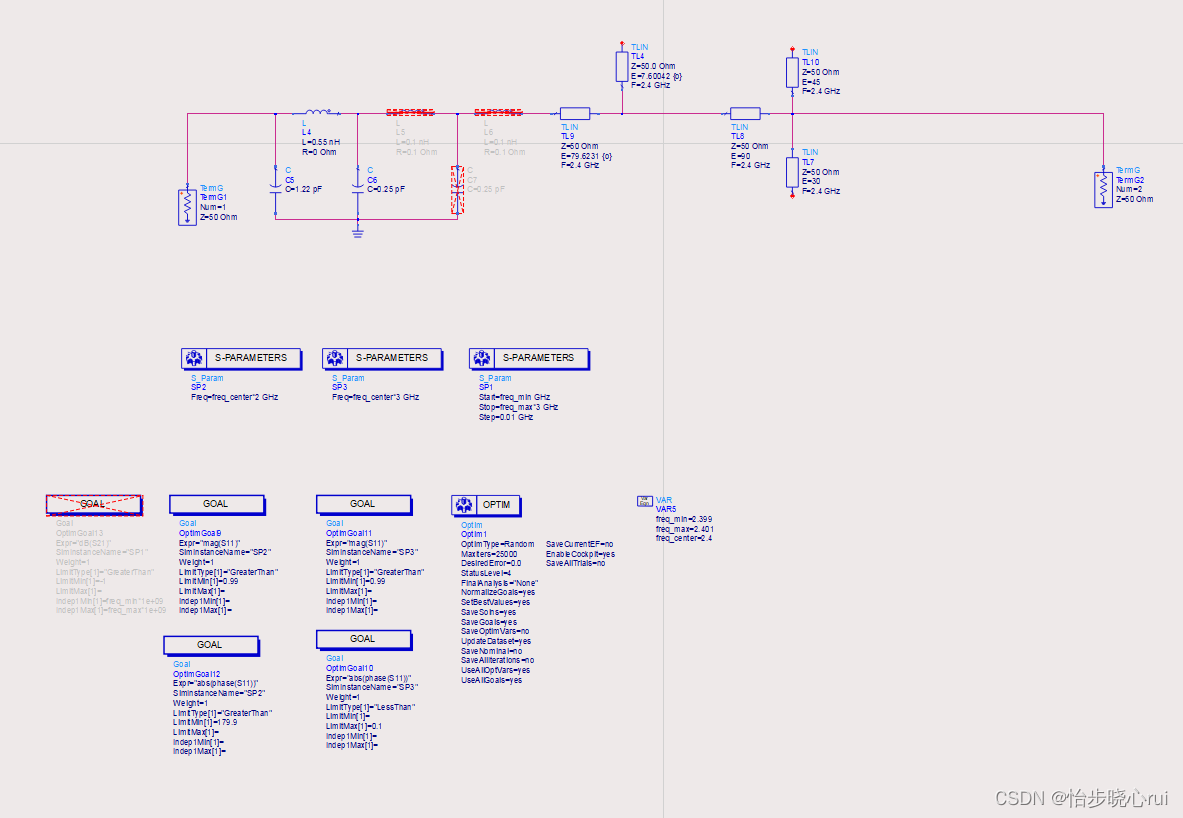

按照文章中的模型进行建模,设置参数自动调制OPTIM控件,运行参数得到最佳的数值:

观察最后的结果,最终结果如下所示(可以看到设计在考虑寄生参数的情况下依旧能满足开路短路条件):

6. Tirón de carga y tirón de fuente

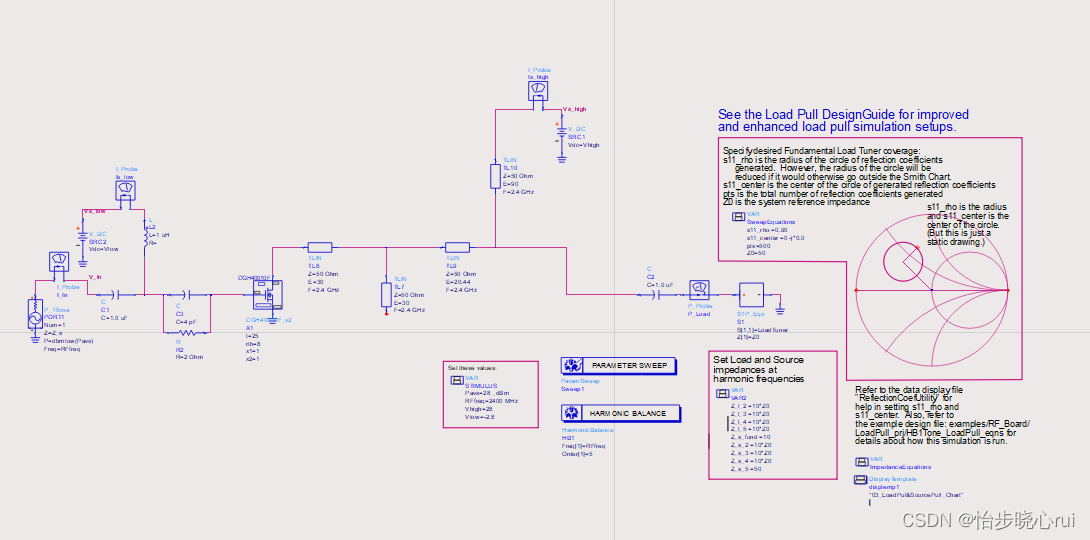

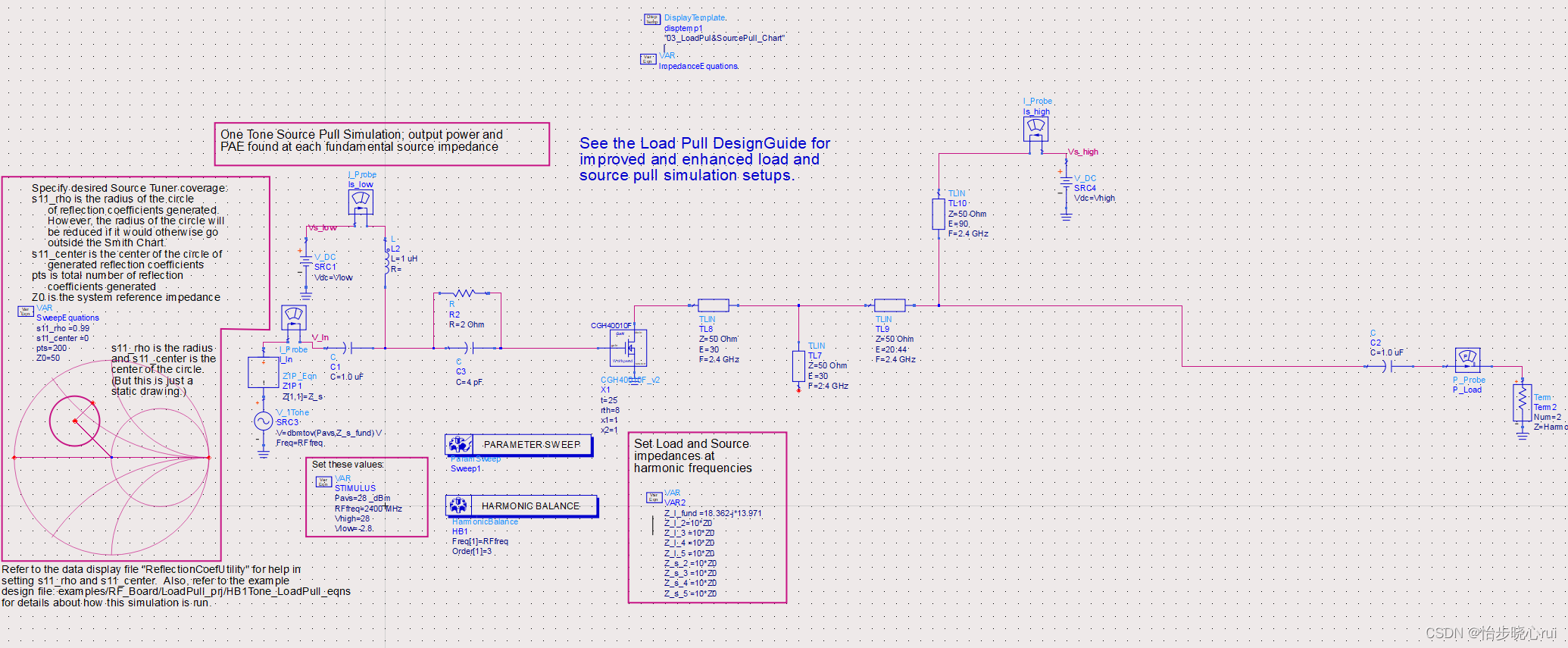

Para el amplificador de potencia de control armónico de clase F, la extracción de carga a menudo solo necesita extraer la onda fundamental, porque ya sabemos cómo configurar la impedancia armónica. Abra la plantilla de tracción de carga e inserte el circuito de control de armónicos y el circuito de estabilidad diseñados anteriormente en el diagrama esquemático, como se muestra a continuación después de la inserción:

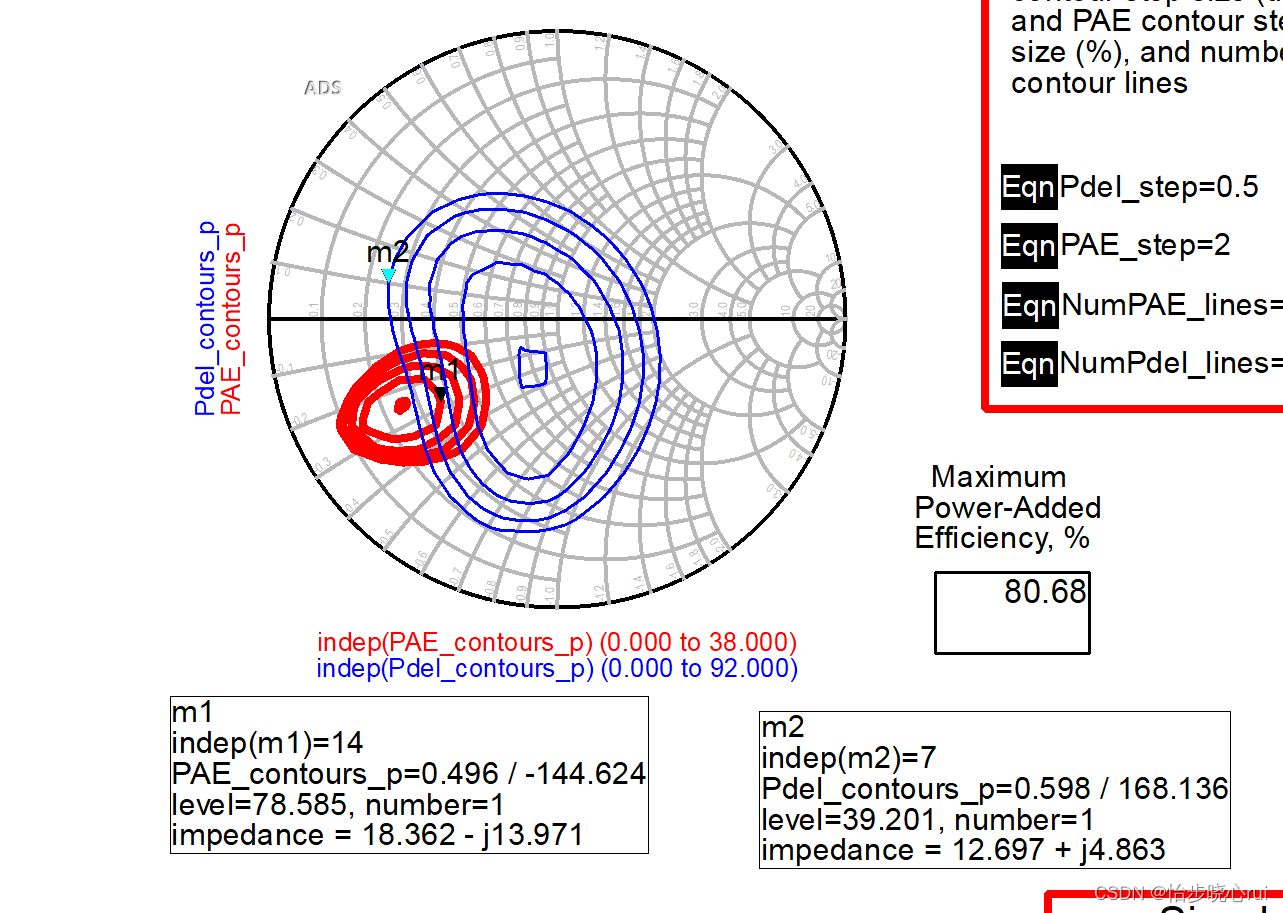

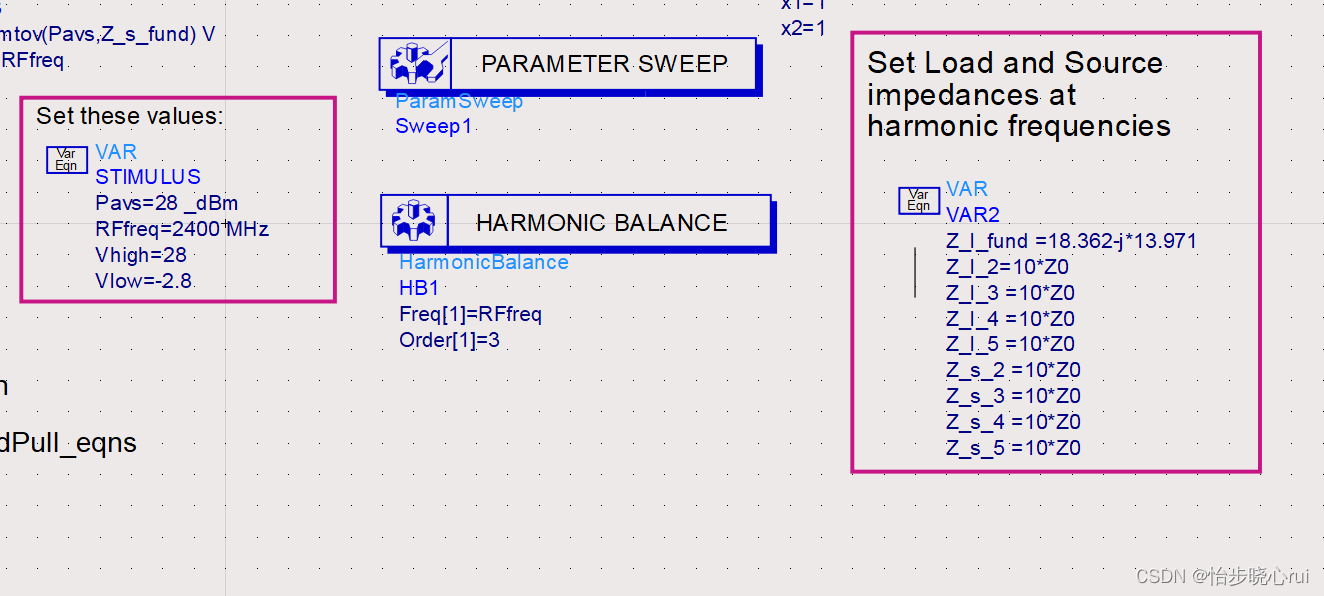

Establezca los parámetros relevantes en el cuadro rojo razonablemente:

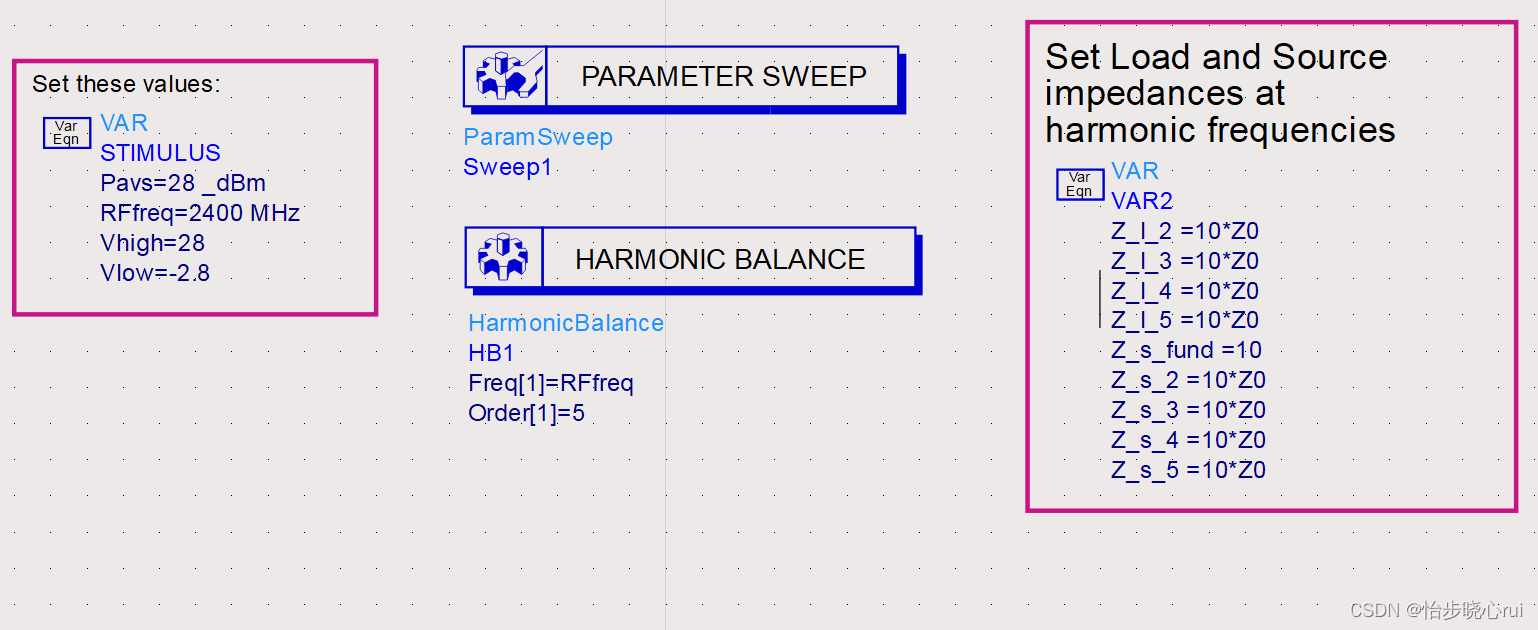

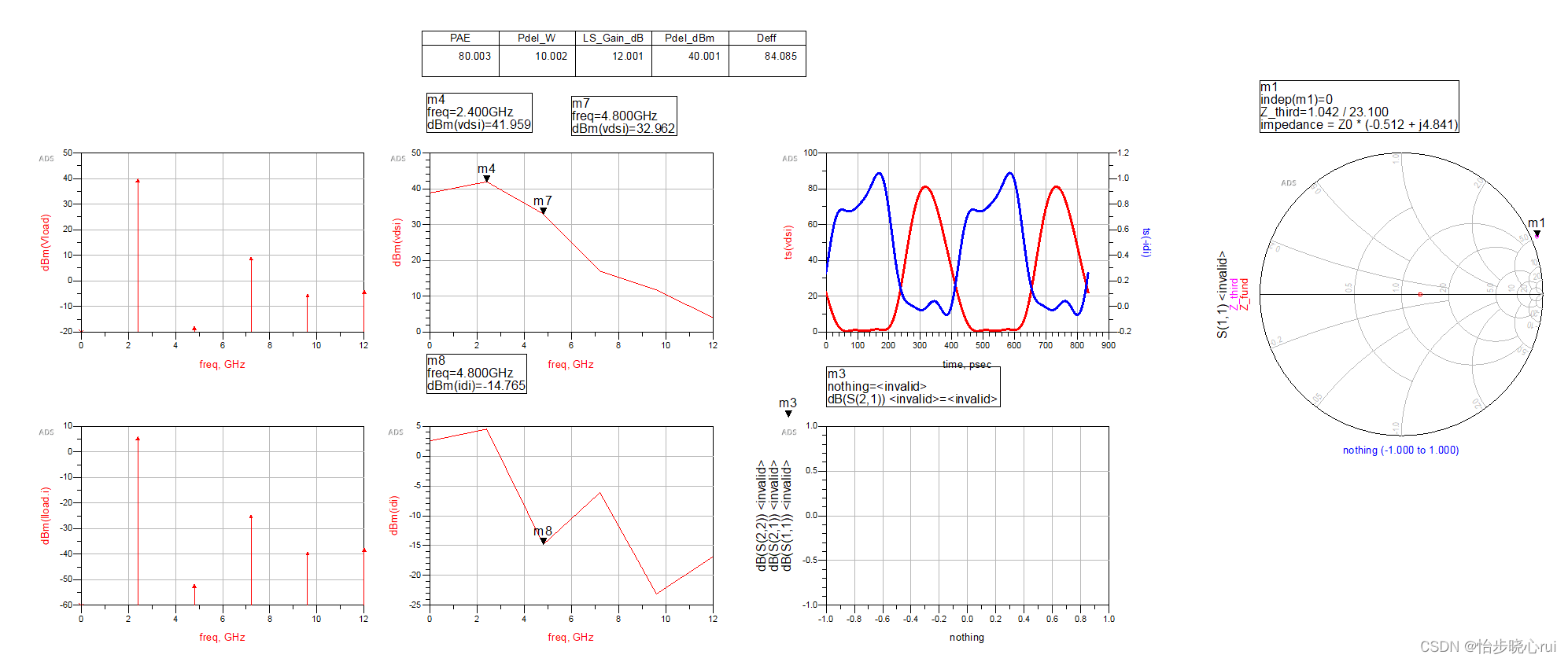

Ejecute el diagrama esquemático para obtener la posición del punto de impedancia M1, y la impedancia de tracción de carga es 18,362-j13,971 ohmios. Aquí se consideran la ganancia y la eficiencia, y se espera obtener una eficiencia de potencia agregada de alrededor del 78,5 % y una ganancia de 10 db:

A continuación, realice la extracción de la fuente, inserte la plantilla de extracción de la fuente y configure el circuito de control de armónicos y el circuito de estabilización:

Configure los parámetros en el cuadro rojo:

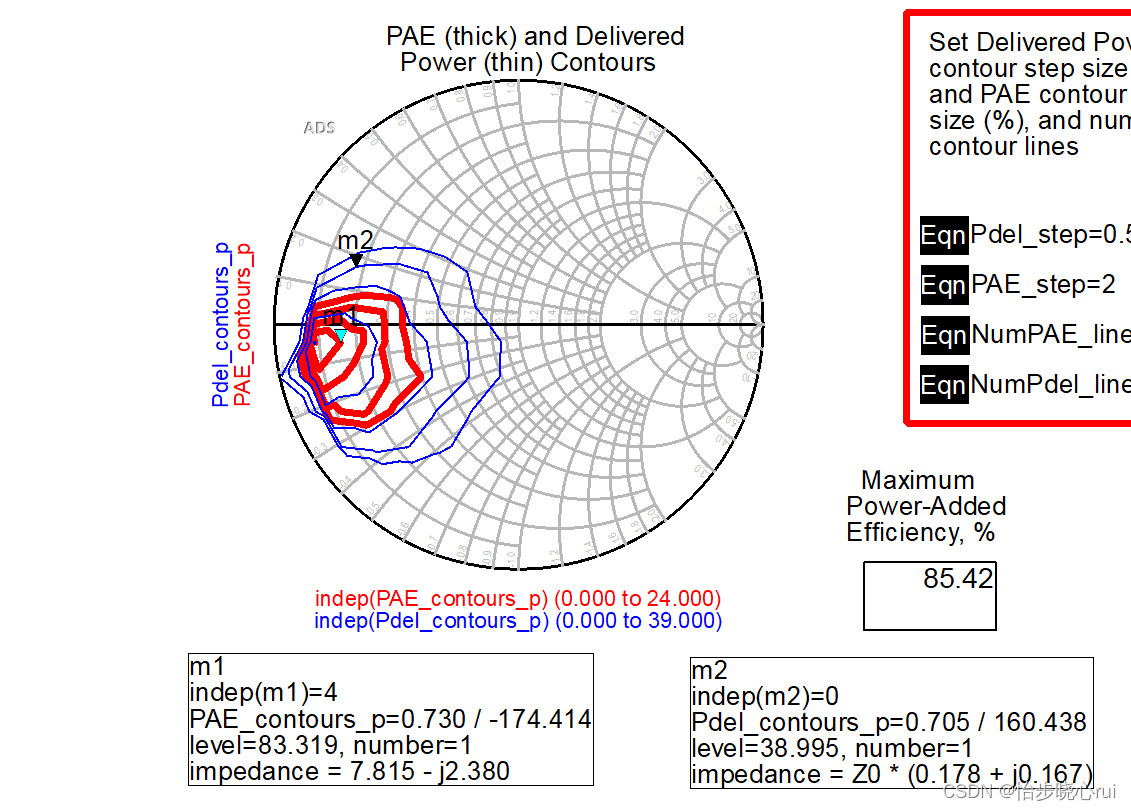

Haga clic para ejecutar la simulación y el área de impedancia de alta eficiencia se obtiene de la siguiente manera. Se puede ver que la impedancia de la fuente alcanza la máxima eficiencia en 7.815-j*2.380:

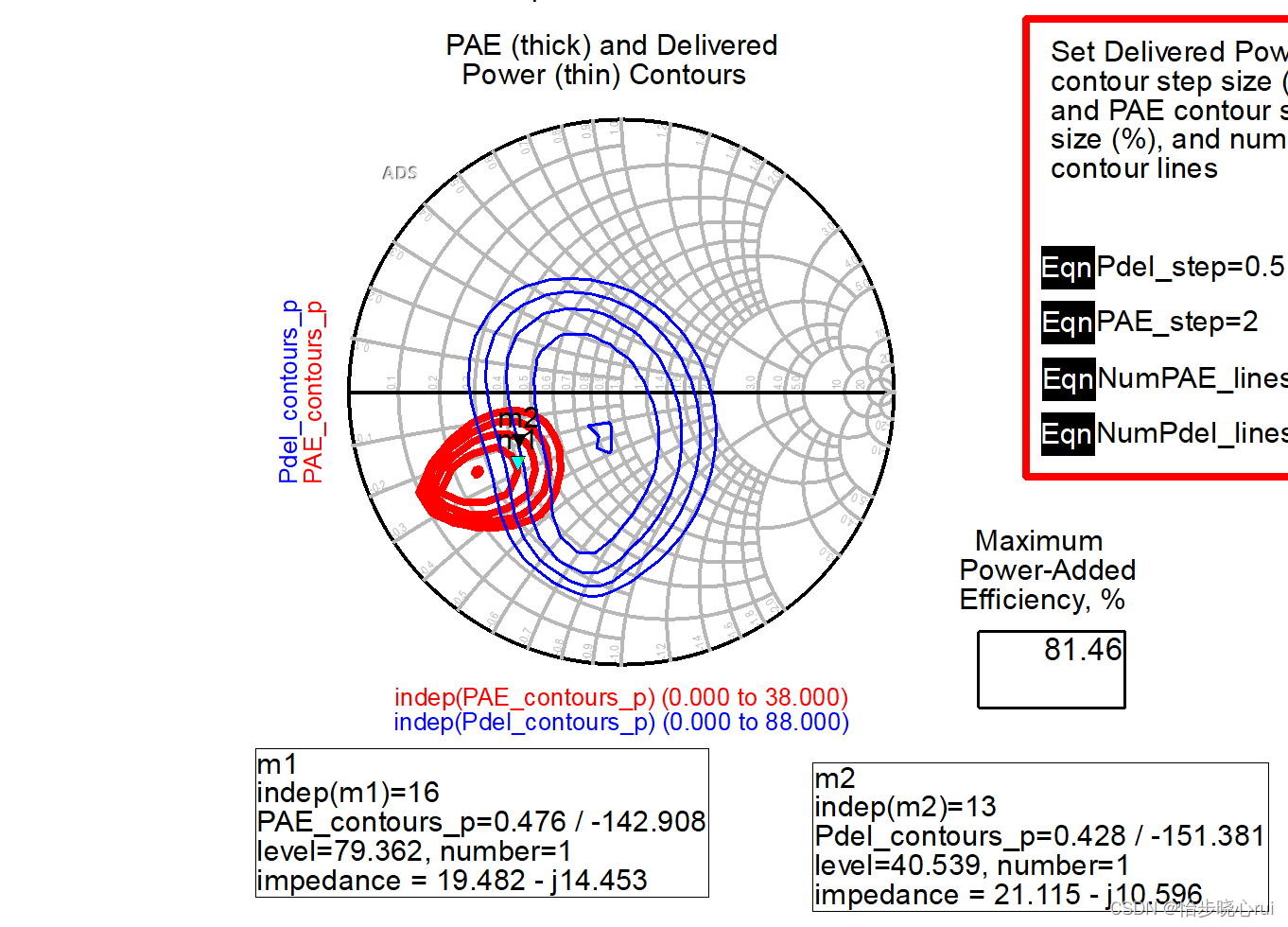

Regrese al diagrama esquemático de extracción de carga, complete la impedancia de la fuente obtenida de la extracción anterior y realice la simulación nuevamente para obtener el resultado final como se muestra a continuación. Use el valor del segundo tirón de carga como el valor usado para el diseño (19.484-j*14.453):

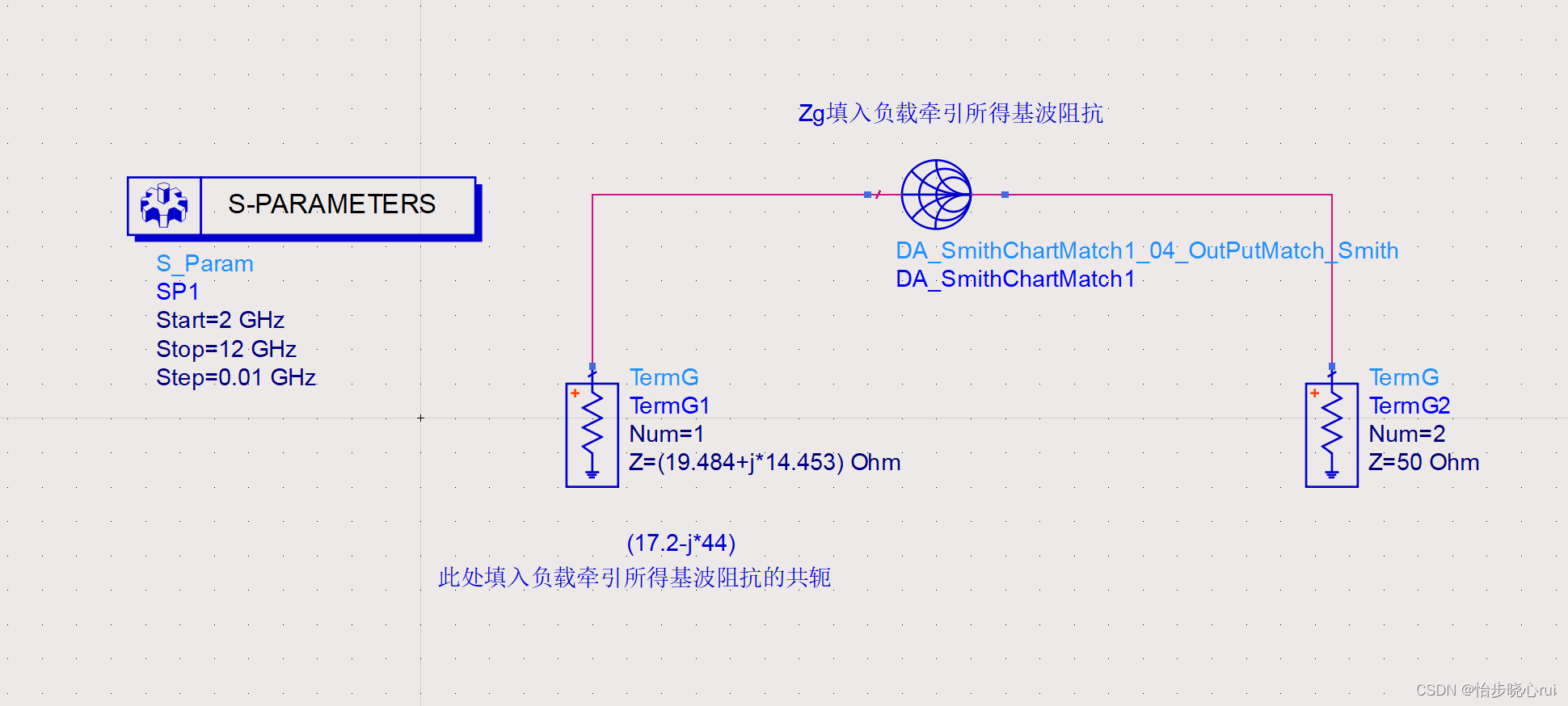

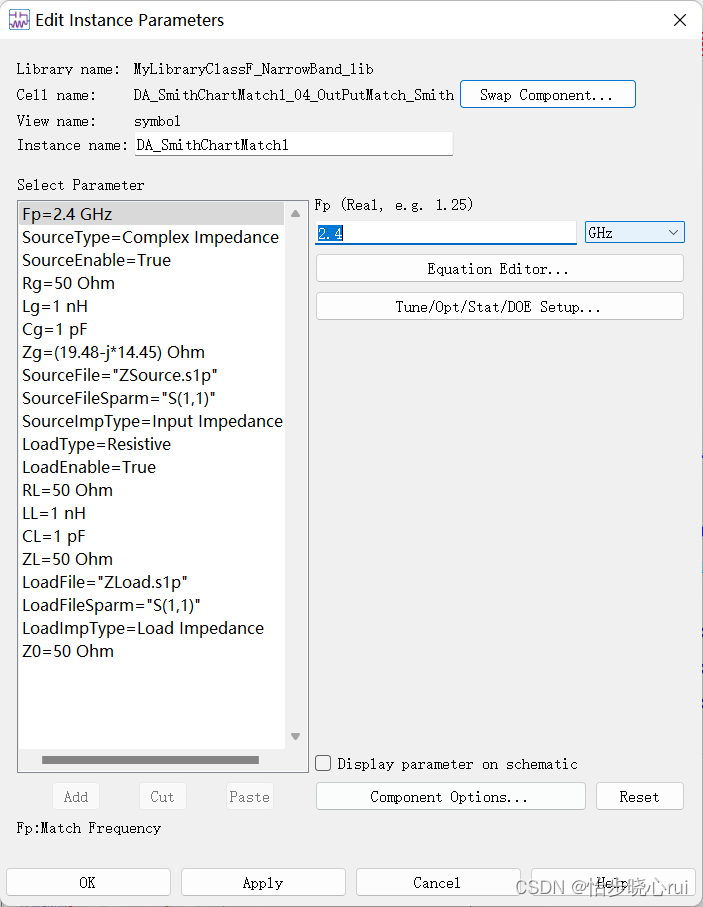

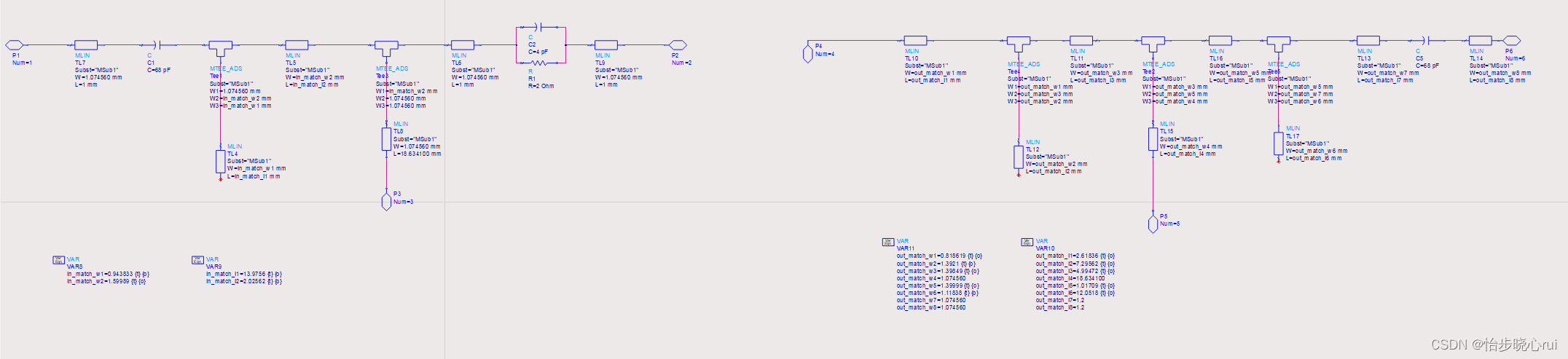

7. Circuito de adaptación de salida

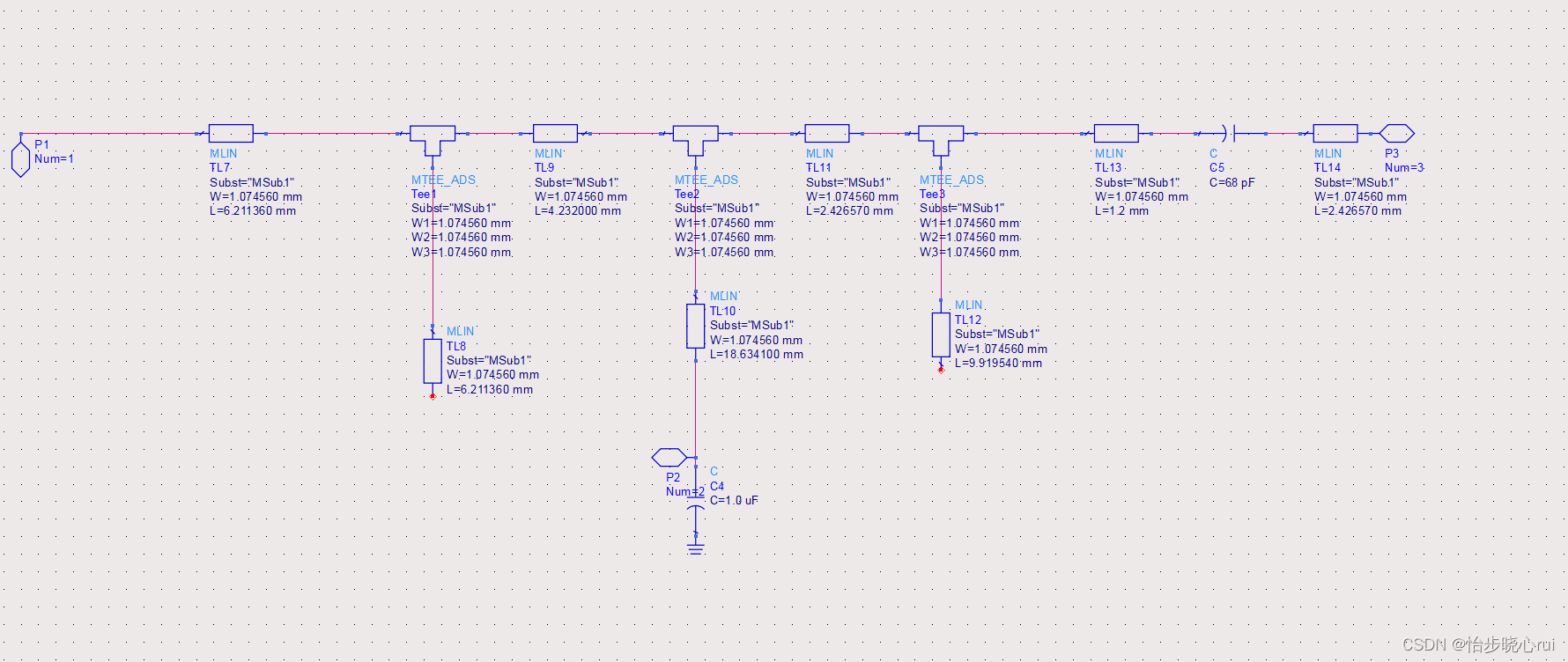

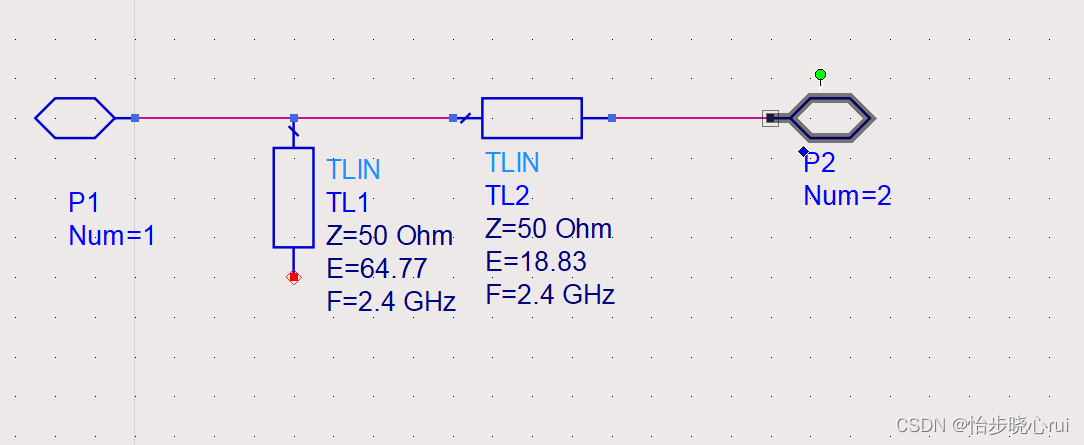

El circuito de coincidencia de salida se diseña primero, y la coincidencia de salida adopta el método de coincidencia de tipo L, y se construye el siguiente diagrama de circuito:

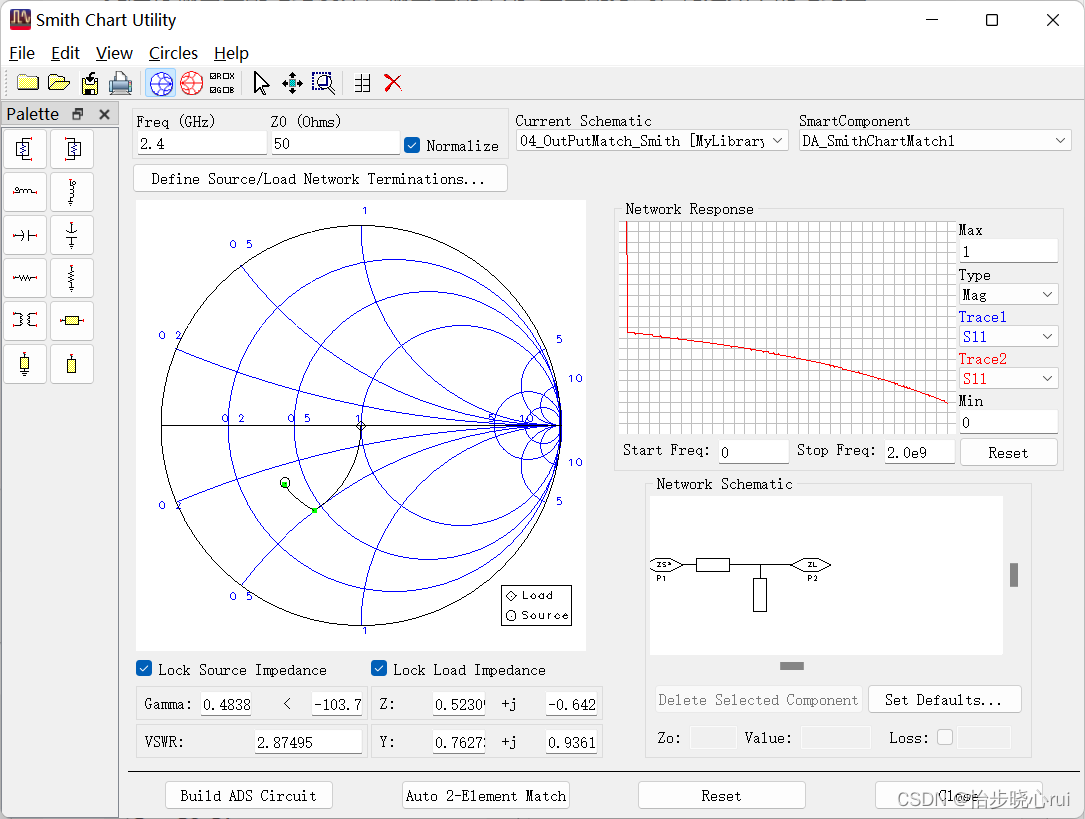

Abra la interfaz de dibujo de Smith y use el método de coincidencia L para hacer coincidir:

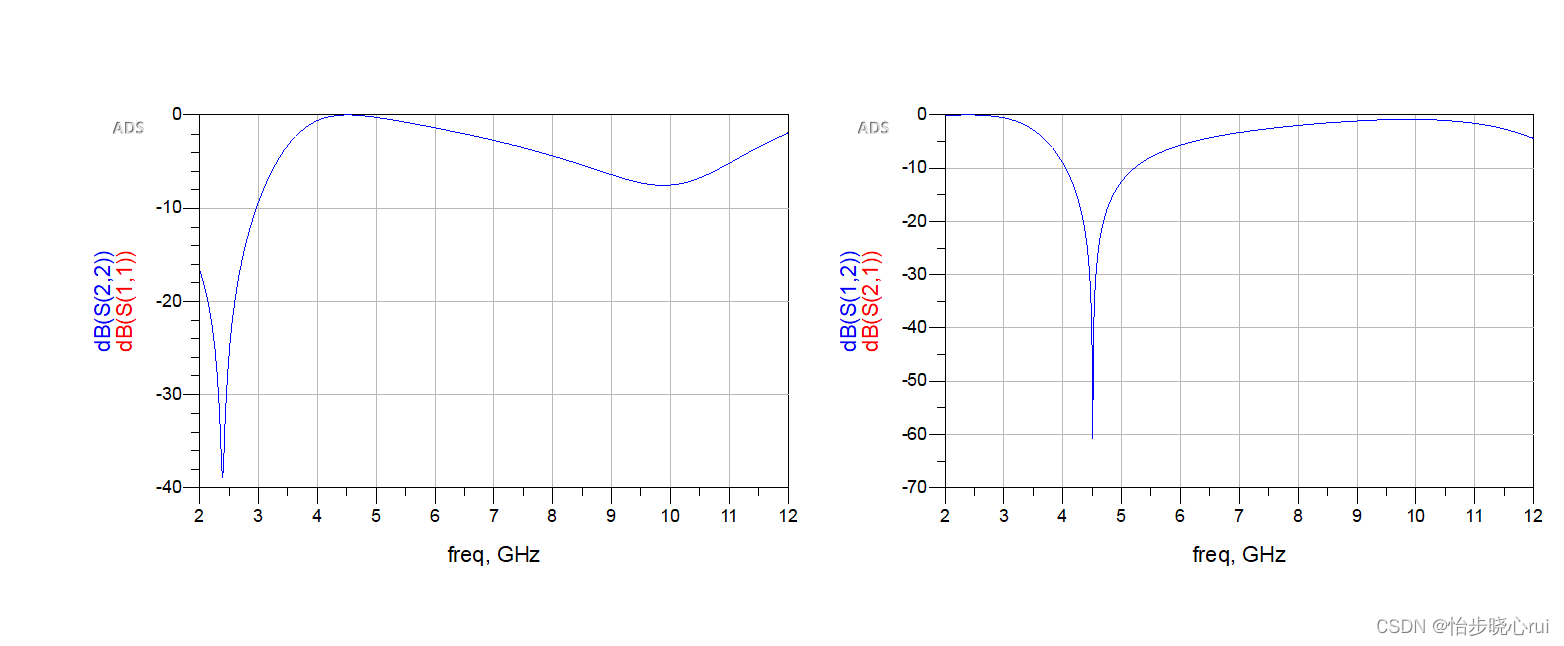

Haga clic en Generar circuito y ejecute la simulación, y descubra que la coincidencia funciona bien:

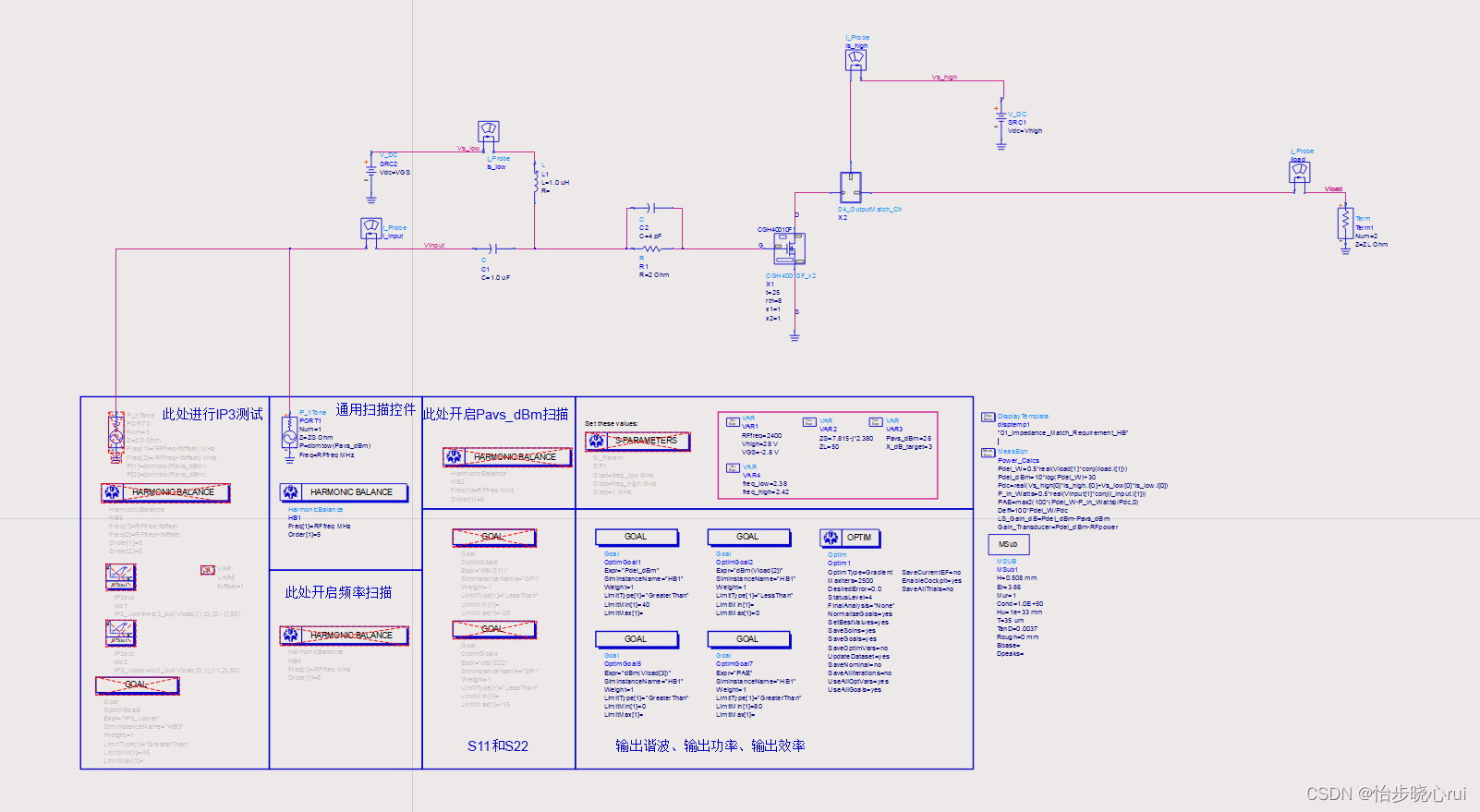

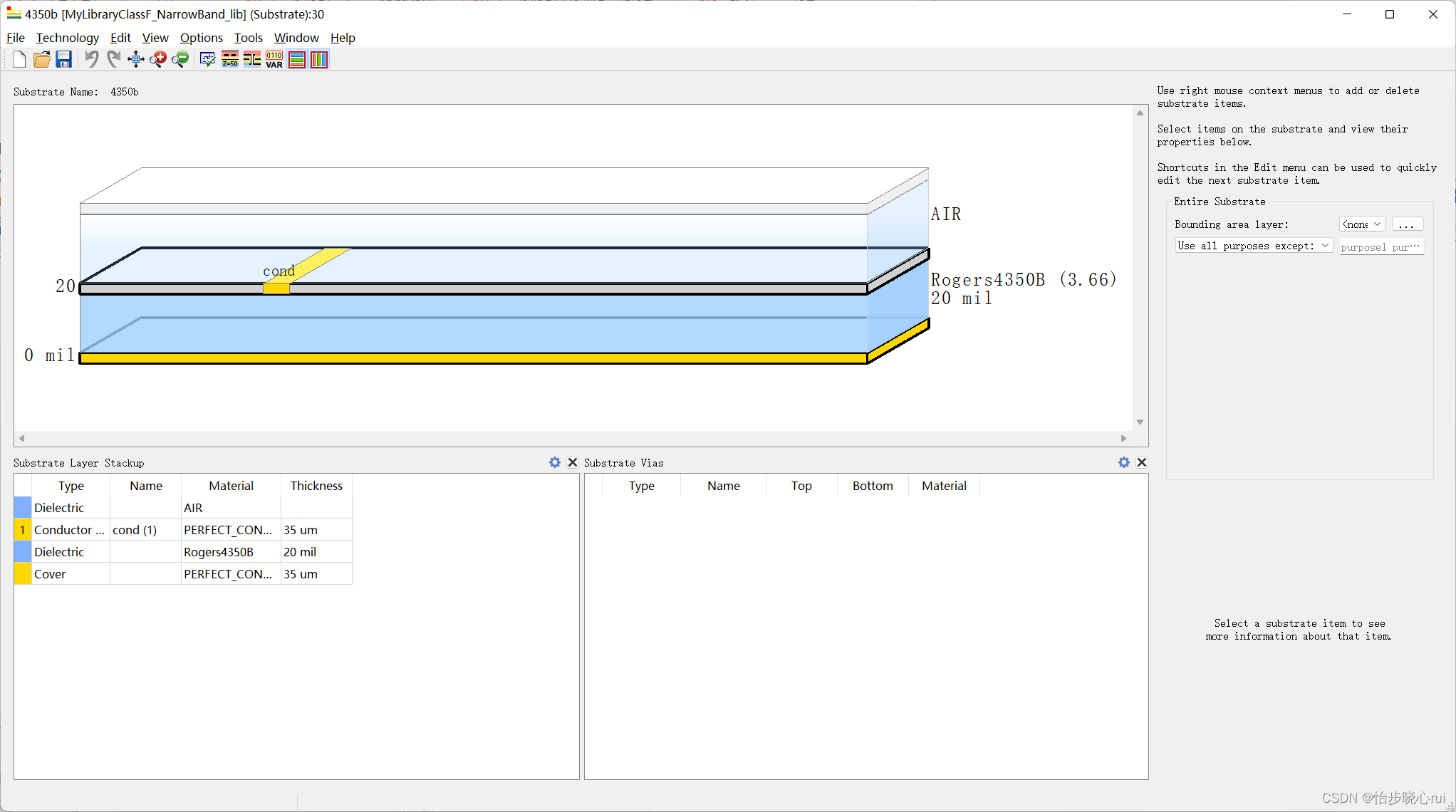

Inserte el circuito coincidente y el circuito de control de armónicos previamente diseñado en un solo diagrama esquemático y conecte los dispositivos relacionados para convertir el dispositivo en una línea microstrip real. Aquí, se utiliza la placa ROGERS4350B:

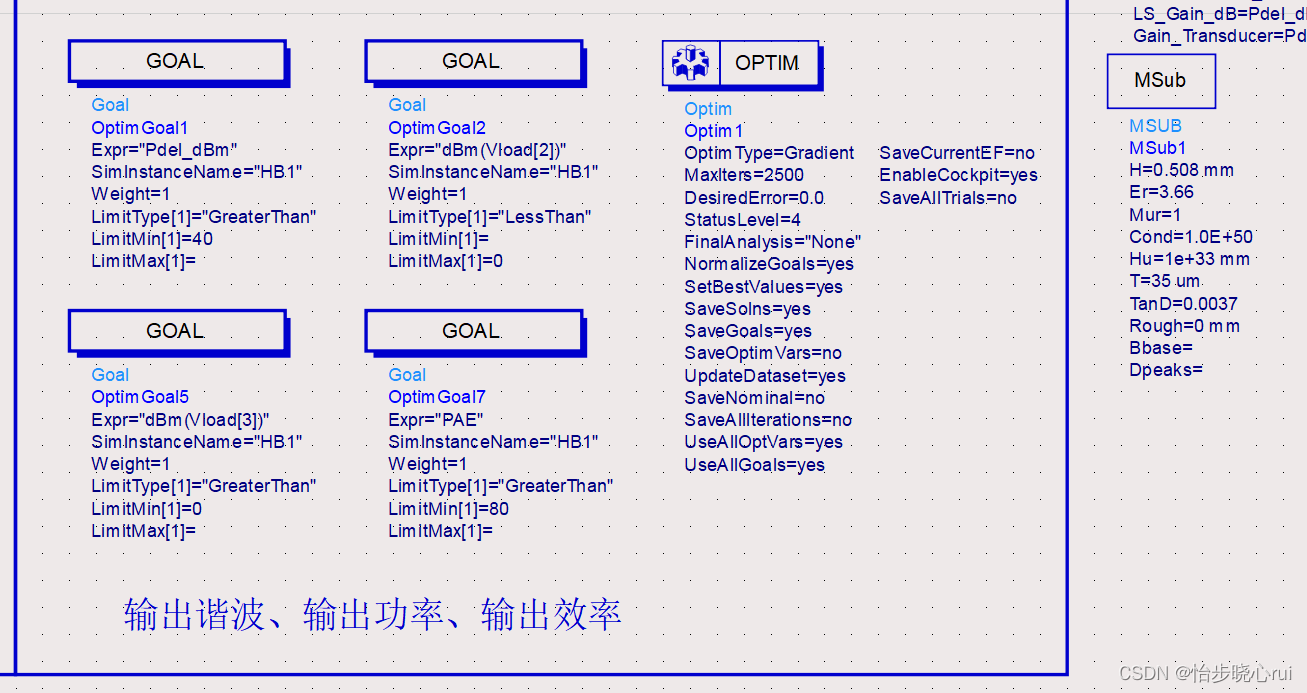

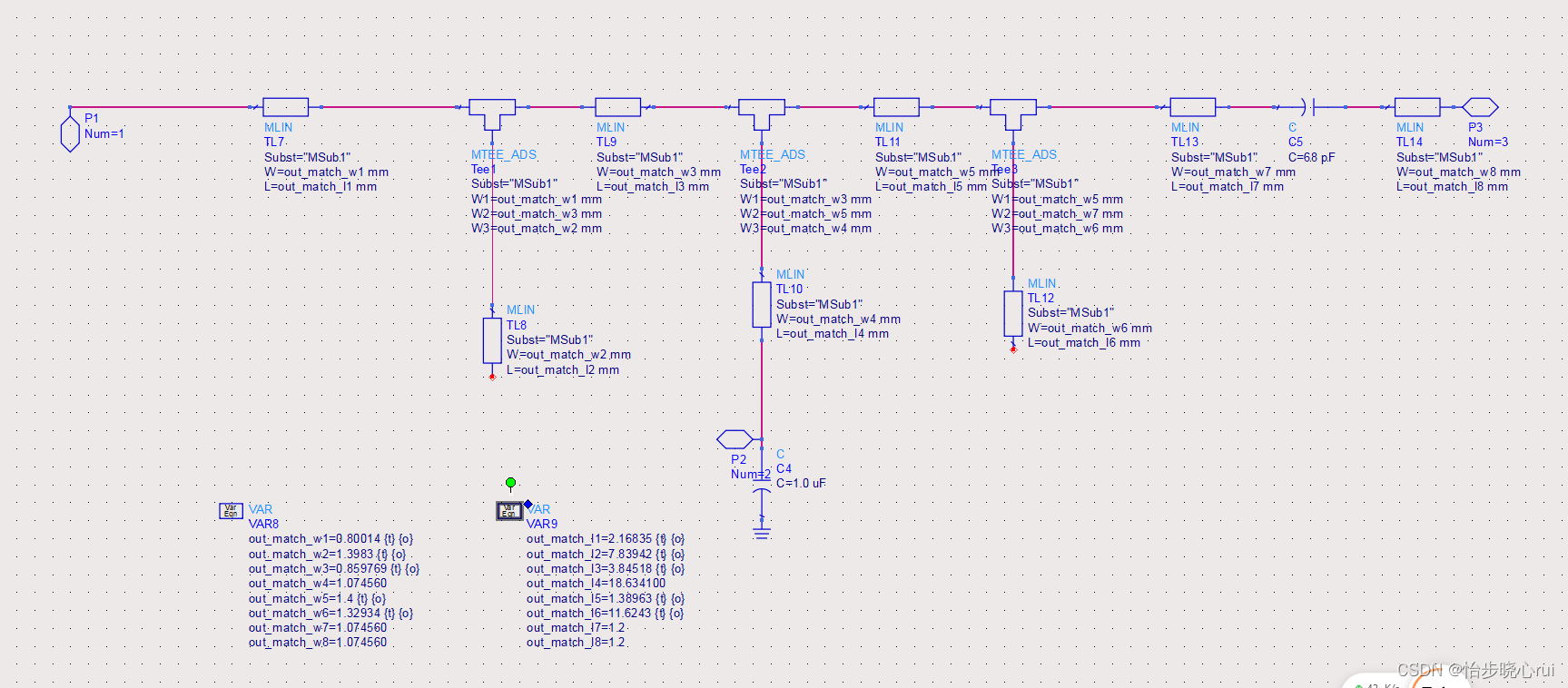

Configure el Objetivo correspondiente y ajuste automáticamente los parámetros del diagrama esquemático. Después del ajuste, se obtienen los siguientes resultados:

OPTIMICE el diagrama esquemático para obtener el resultado final:

8. Circuito de adaptación de entrada

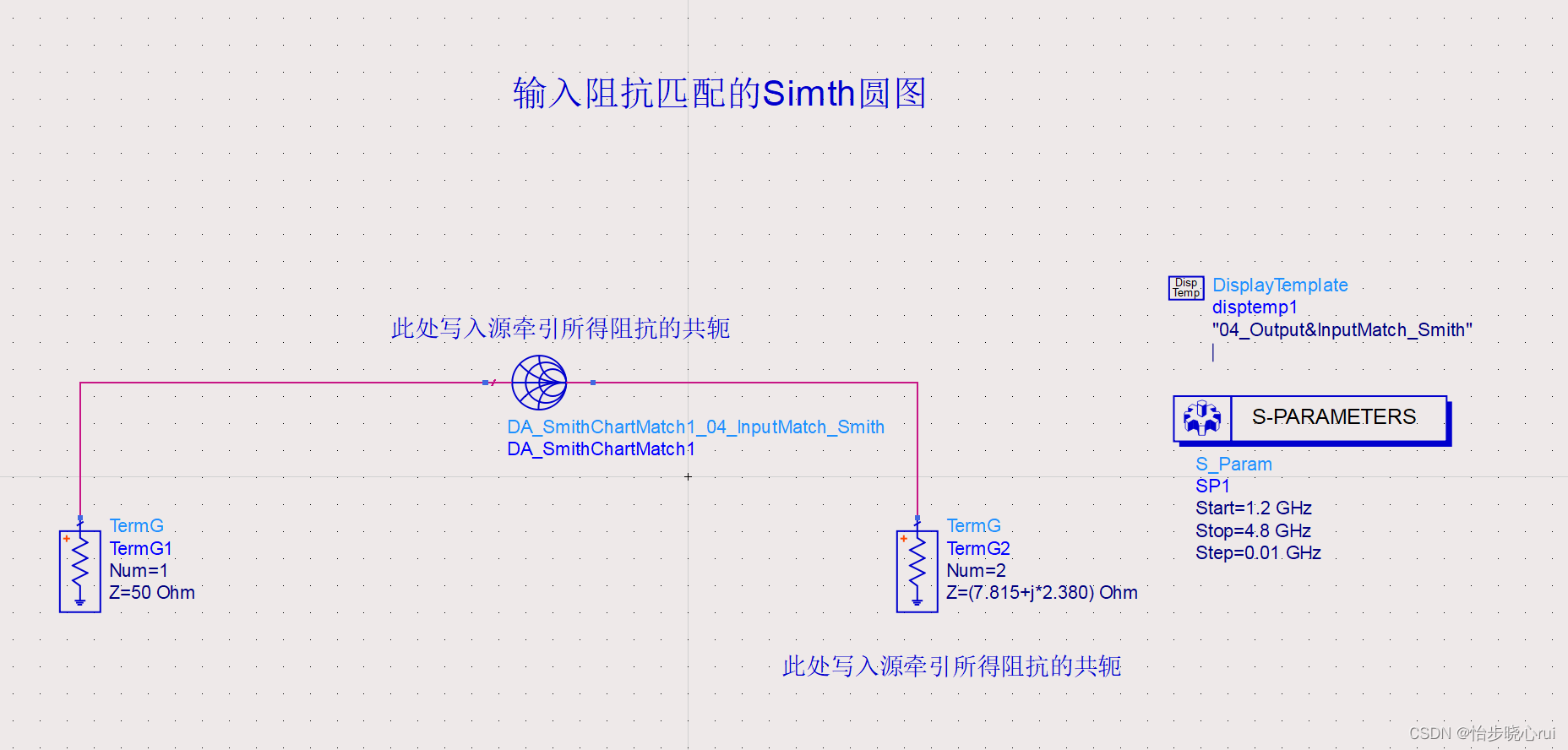

Construya el siguiente circuito de adaptación de impedancia de salida, use el gráfico SMITH para la coincidencia:

use la coincidencia L para la coincidencia de entrada:

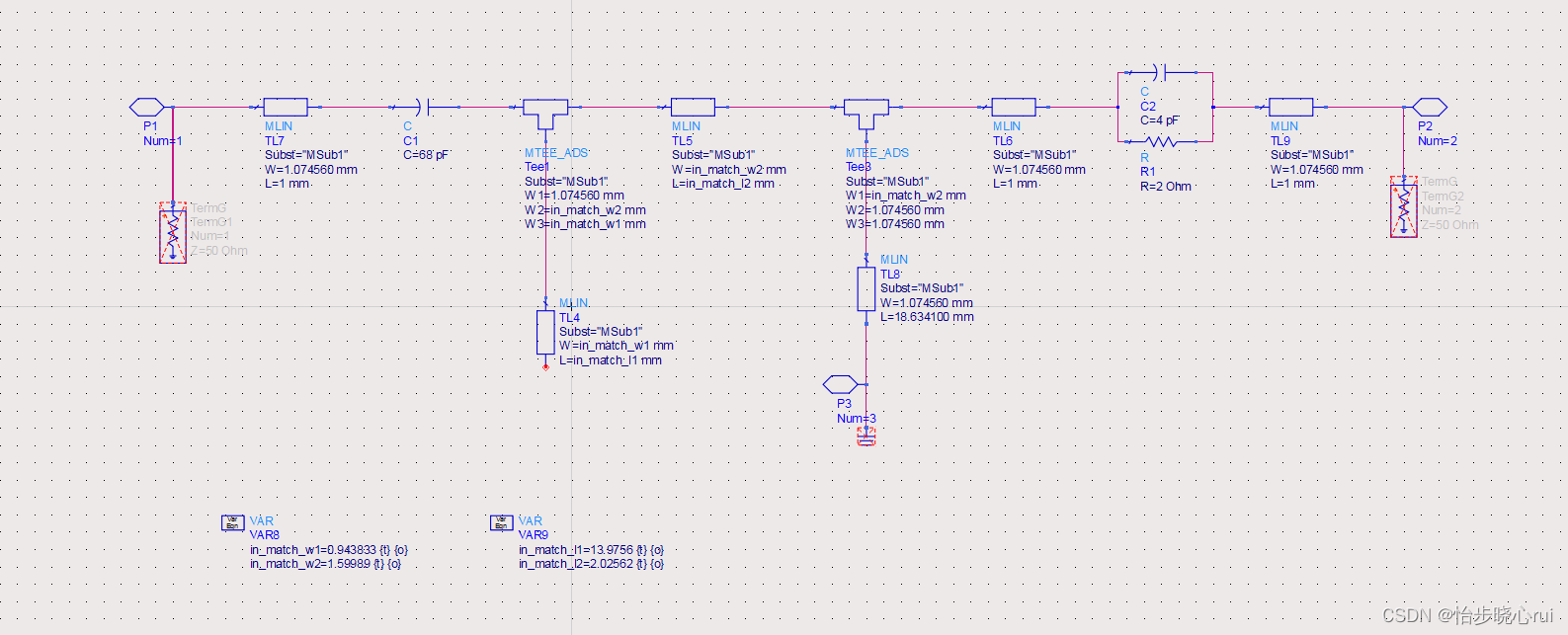

conviértalo en un diagrama de circuito real, use la placa 4350B (aquí se suma el circuito estable): pruebe esta

coincidencia de entrada y salida juntos:

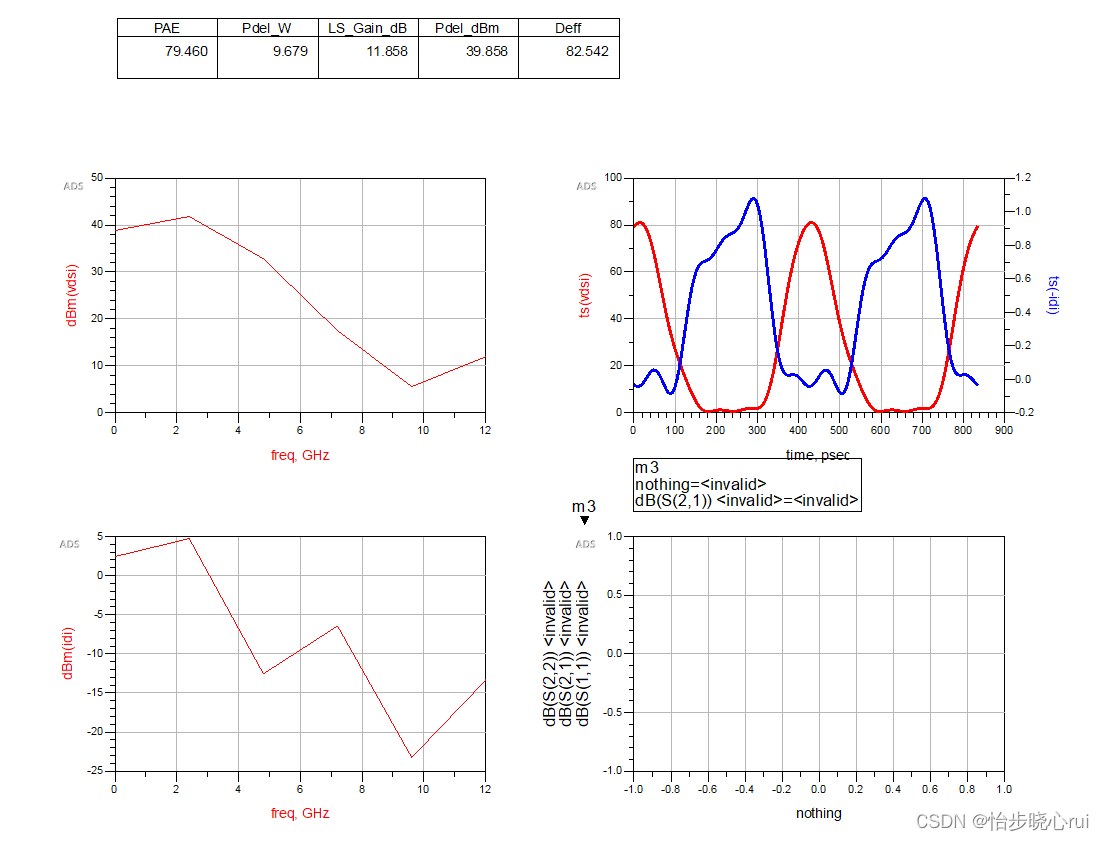

finalmente realice una prueba de simulación y descubra que la eficiencia de drenaje de 82 y la ganancia superior a 10db se pueden obtener durante la simulación esquemática:

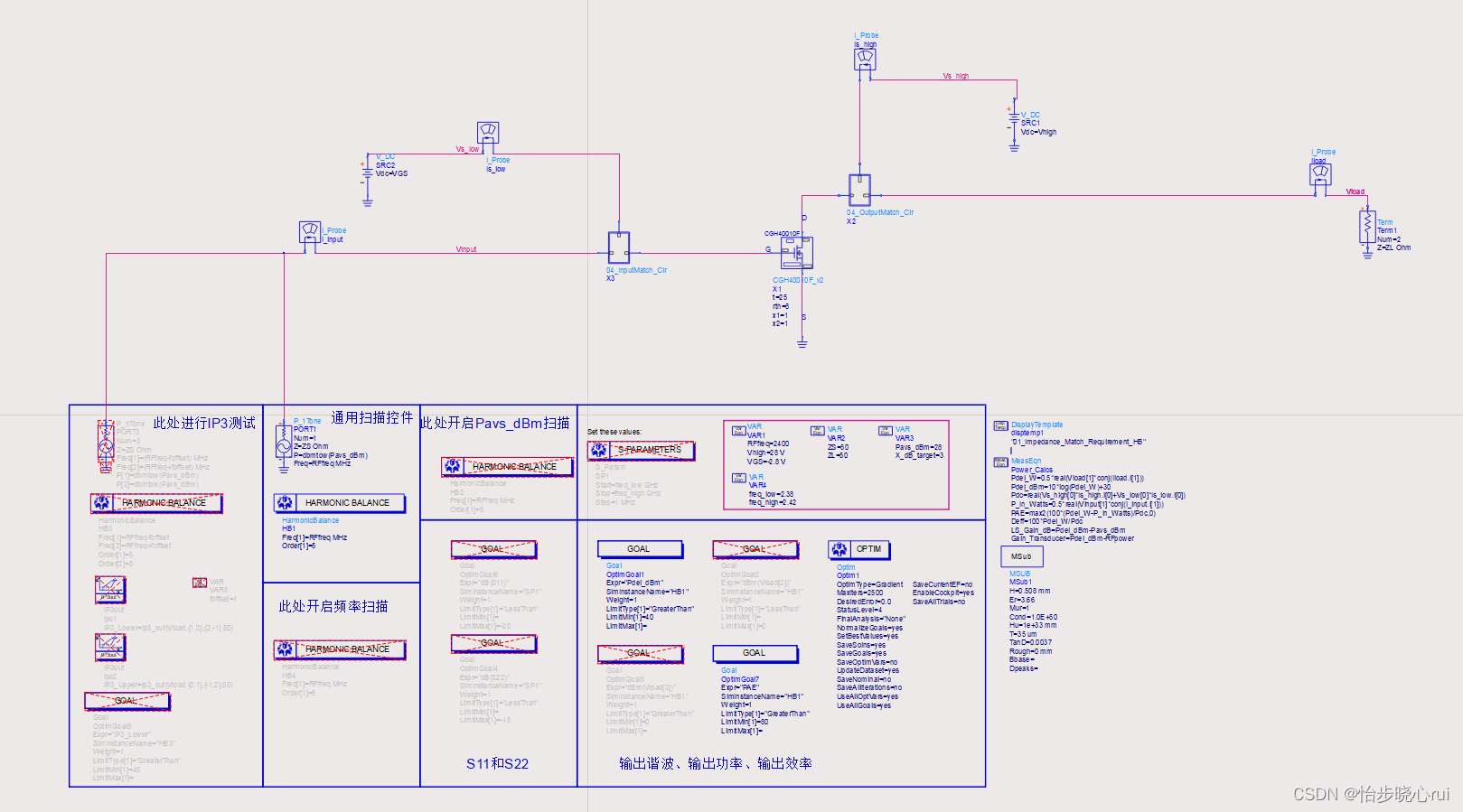

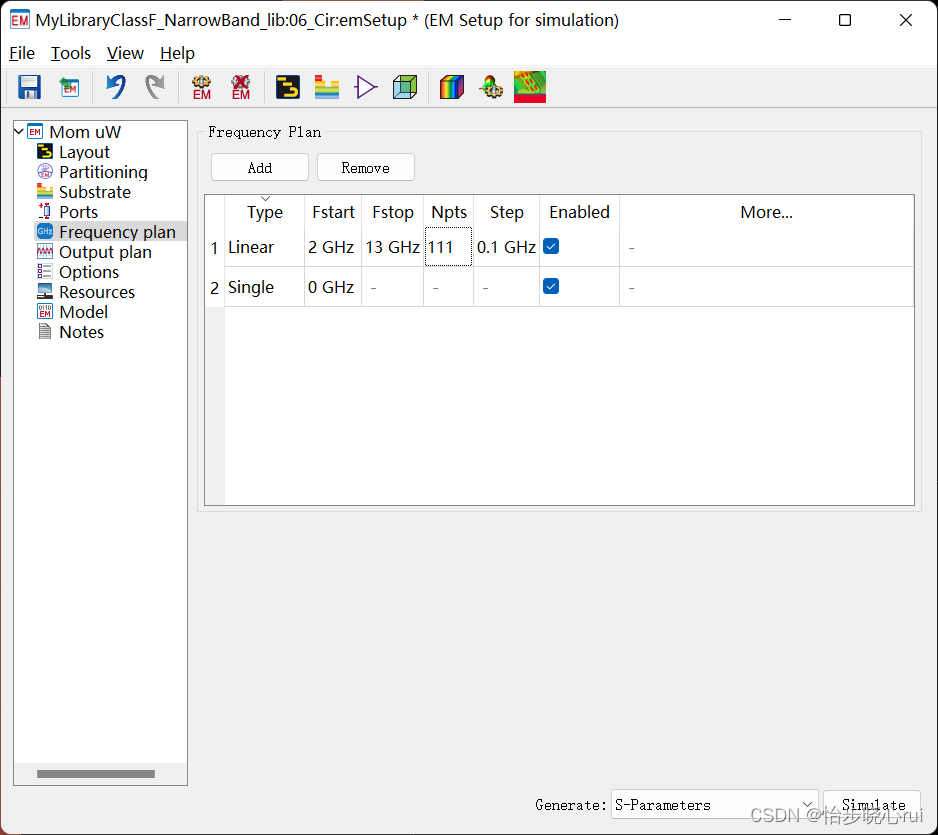

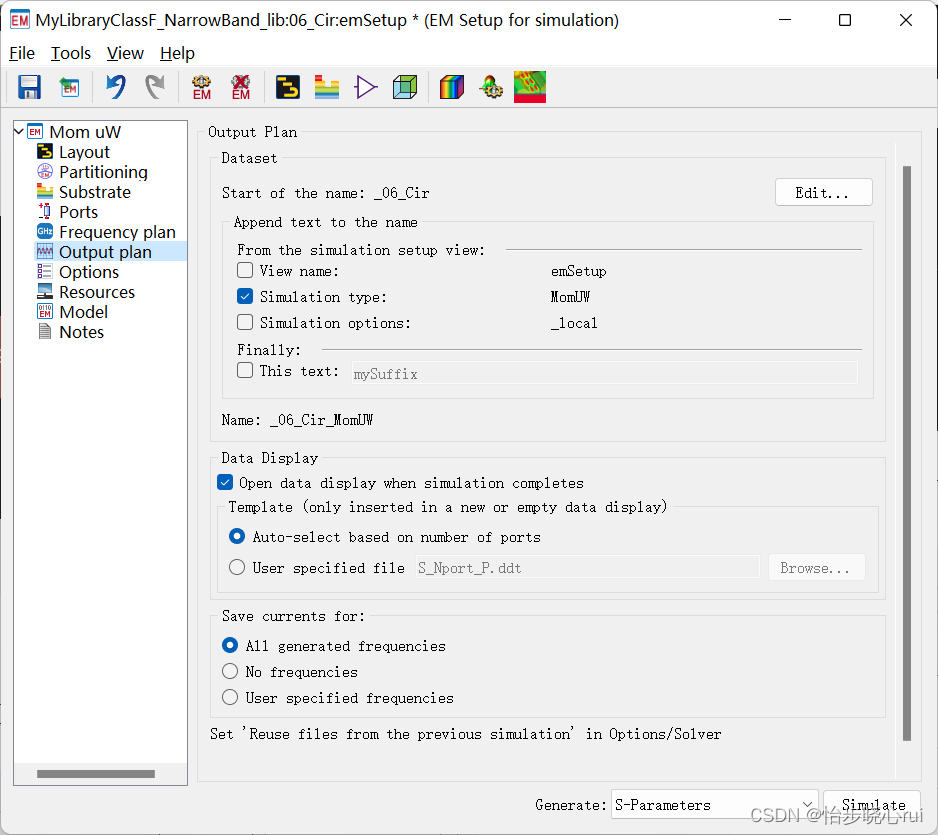

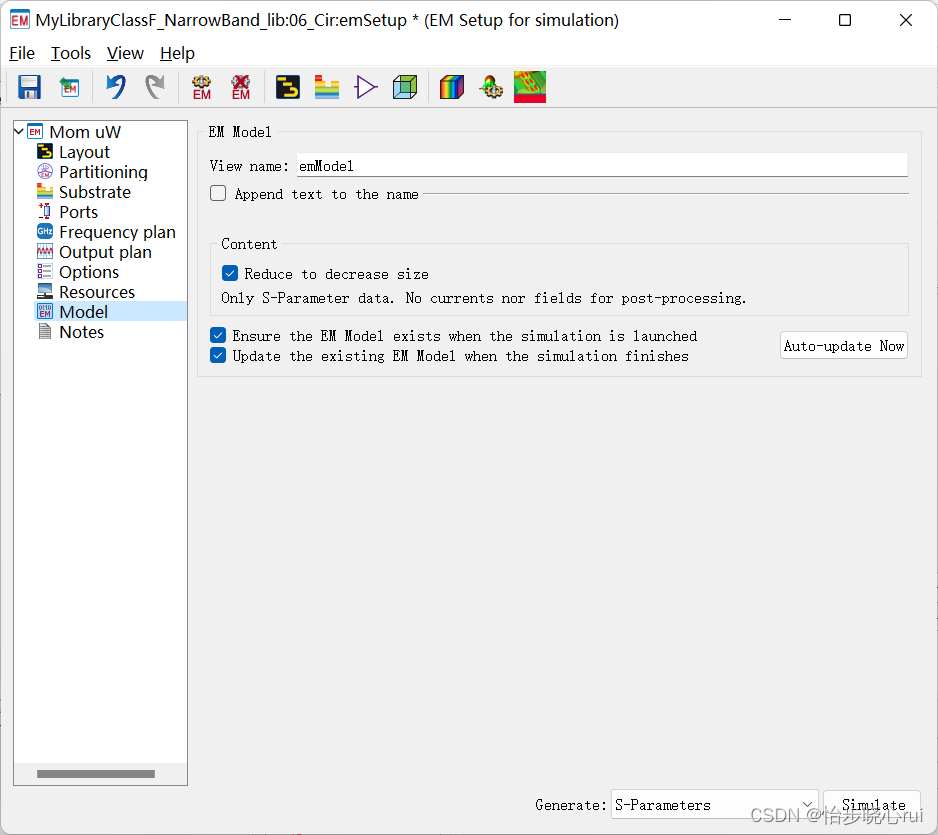

9. Simulación de diseño

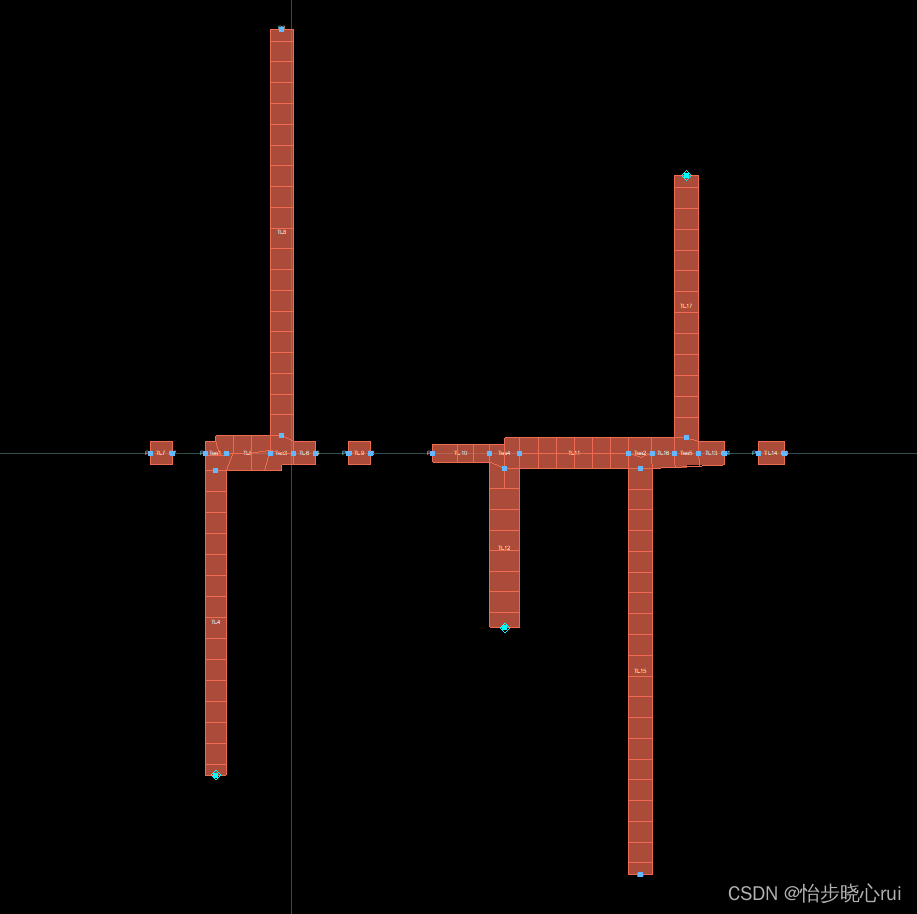

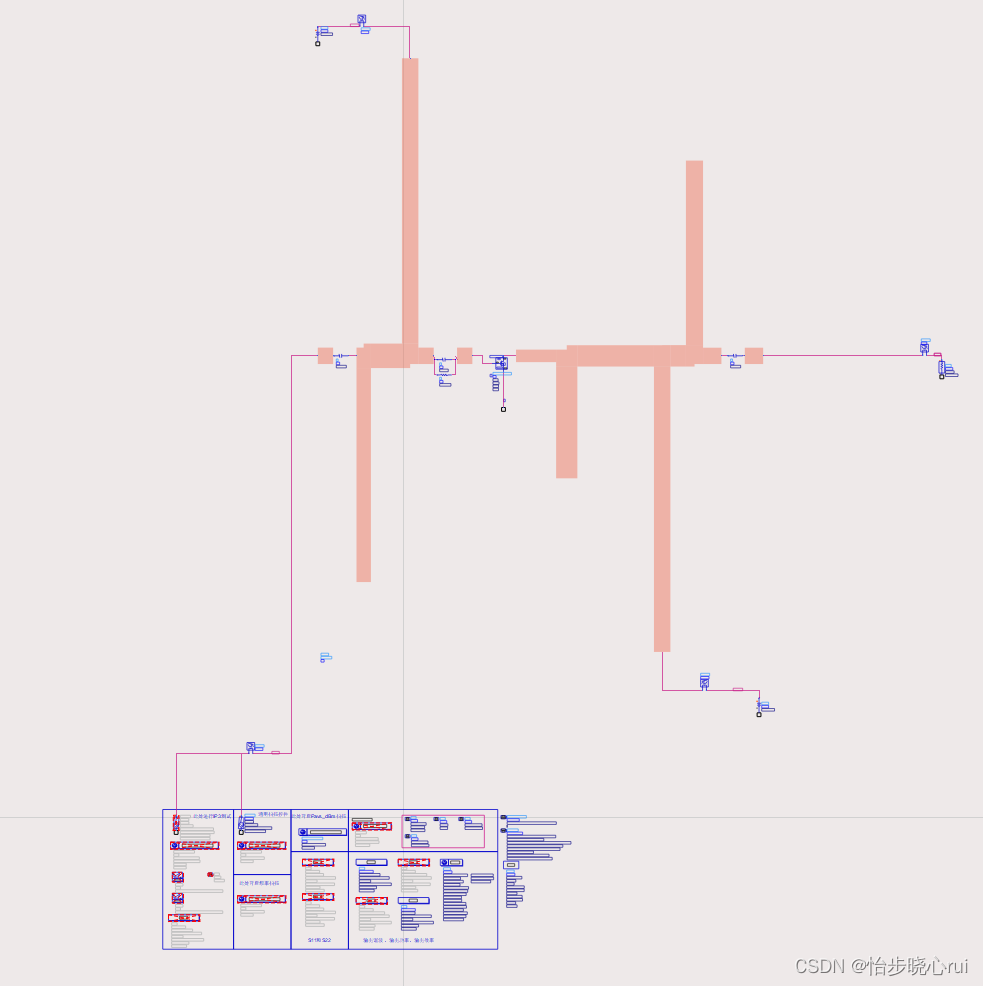

Coloque los circuitos coincidentes de entrada y salida en el nuevo diagrama esquemático:

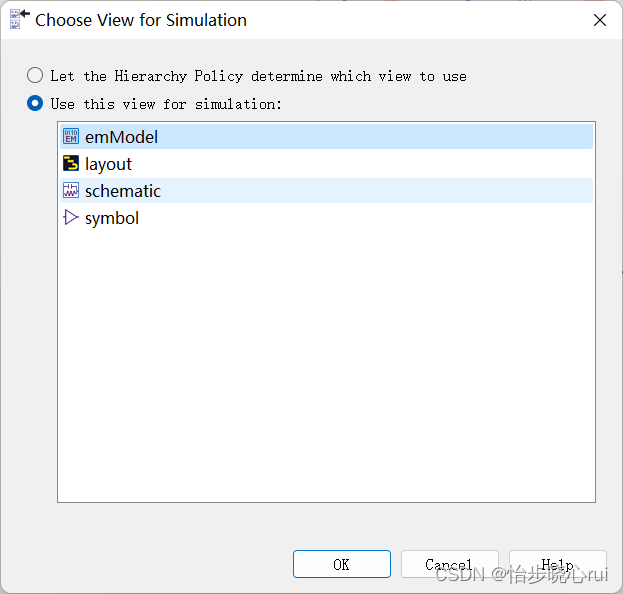

genere el diseño y organícelo razonablemente (normalmente, se usa un arco o una estructura simétrica para reducir el área, y el diagrama se omite aquí por conveniencia): inserte los puertos relevantes en la conexión: configure los parámetros de frecuencia de la simulación, etc.: configure la placa 4350B: haga clic para ejecutar la simulación, obtenga el resultado y cree un símbolo después de obtener el resultado: cree un nuevo diagrama esquemático, asígnele el nombre Co_sim, inserte el símbolo de placa de circuito anterior y conecte: configure la

opción

de

simulación

para

emmodelar

:

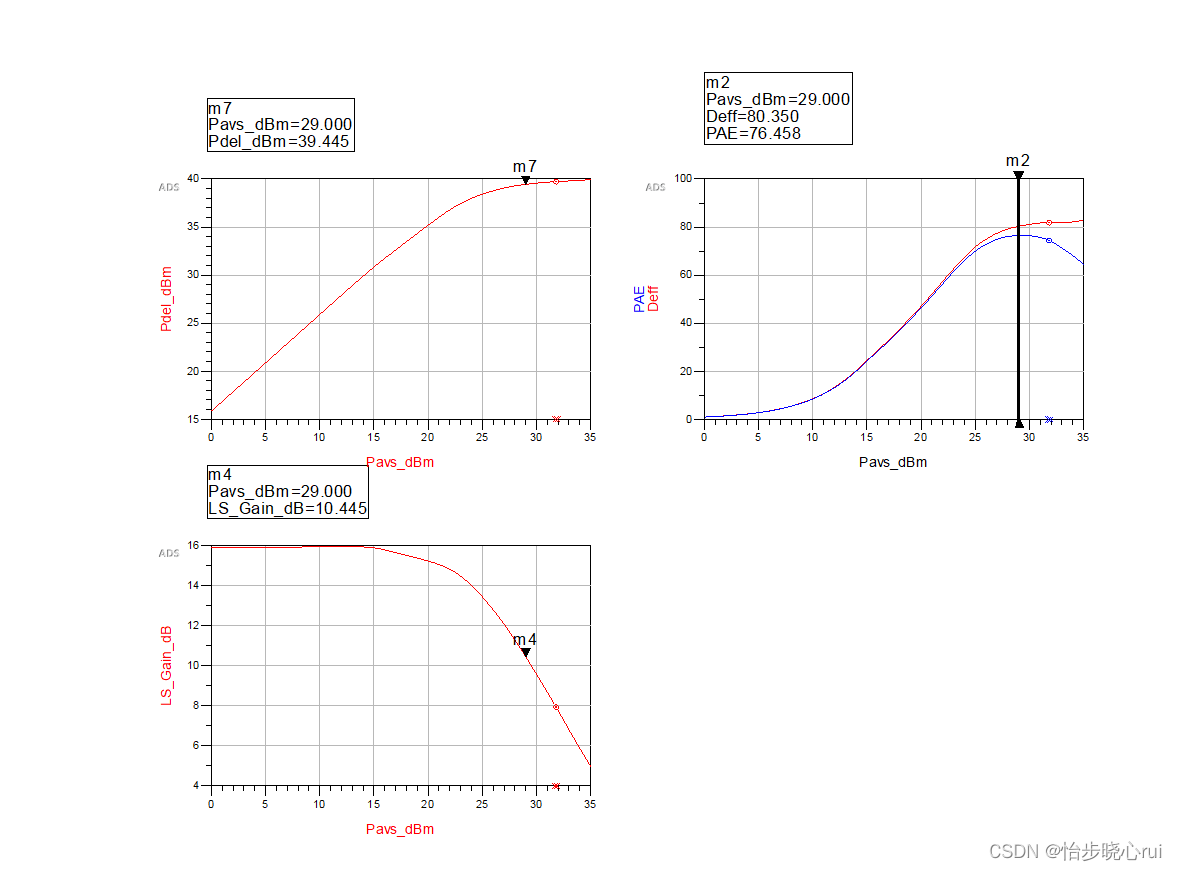

La co-simulación se lleva a cabo en este diagrama esquemático y se obtienen los resultados. Se puede ver que cuando la potencia de entrada es de 29dbm, la eficiencia de drenaje alcanza el 80% y la ganancia es superior a 10db, lo que cumple con los requisitos: