Introducción a MIPI (interfaz CSI DSI)

Introducción a MIPI (interfaz CSI DSI)

Interfaz de video (2) - MIPI Solution_mipi interface_Fate is your blog-CSDN blog

MIPI Overview_gooooooom's Blog-CSDN Blog

Introducción a las pruebas de interfaz Camera Mipi - Se busca programador

Interfaz multimedia MIPI - Zhihu

MIPI ( Interfaz de procesador de la industria móvil ) es una alianza establecida por ARM, Nokia, ST , TI y otras empresas en 2003. Complejidad de diseño y mayor flexibilidad de diseño. Hay diferentes grupos de trabajo bajo MIPI Alliance, que definen una serie de estándares de interfaz interna de teléfonos móviles , como la interfaz de cámara CSI , la interfaz de pantalla DSI , la interfaz de radiofrecuencia DigRF , la interfaz de micrófono/altavoz SLIMbus , etc. La ventaja de un estándar de interfaz unificado es que los fabricantes de teléfonos móviles pueden elegir de manera flexible diferentes chips y módulos del mercado según sus necesidades, lo que hace que sea más rápido y conveniente cambiar diseños y funciones. La siguiente figura muestra la arquitectura interna de la próxima generación de teléfonos inteligentes planificada según MIPI.

MIPI es un estándar relativamente nuevo, y sus especificaciones se revisan y mejoran constantemente. En la actualidad, las aplicaciones de interfaz relativamente maduras incluyen DSI ( interfaz de pantalla ) y CSI ( interfaz de cámara ). CSI/DSI significa que soportan el peso de las aplicaciones de cámara o pantalla, respectivamente, y ambas tienen estructuras de protocolo complejas. Tomando DSI como ejemplo, su estructura de capa de protocolo es la siguiente:

La capa física (Phy Layer) de CSI/DSI está formulada por un grupo de trabajo especial y su estándar actual es D-PHY . D-PHY utiliza 1 par de relojes diferenciales síncronos de fuente y de 1 a 4 pares de líneas de datos diferenciales para la transmisión de datos. La transmisión de datos adopta el modo DDR, es decir, hay transmisiones de datos en los bordes superior e inferior del reloj.

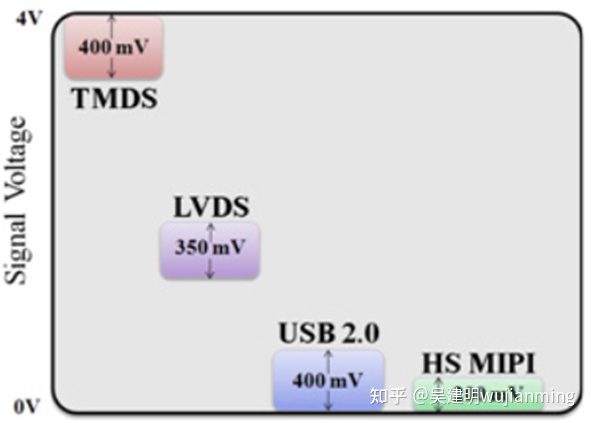

La capa física de D-PHY admite dos modos de trabajo: HS (alta velocidad) y LP (baja potencia) . En el modo HS, se usa una señal diferencial de bajo voltaje, que consume mucha energía, pero puede transmitir una alta velocidad de datos (la velocidad de datos es de 80 M ~ 1 Gbps); en el modo LP, se usa una señal de un solo extremo y los datos La velocidad es muy baja (<10 Mbps), pero el consumo de energía correspondiente también es muy bajo. La combinación de los dos modos garantiza que el bus MIPI pueda transmitir a alta velocidad cuando se necesita transmitir una gran cantidad de datos (como imágenes), y puede reducir el consumo de energía cuando no se requiere transmitir una gran cantidad de datos. .

interfaz CSI

CSI-2 es una interfaz serial diferencial unidireccional o bidireccional que contiene señales de reloj y datos . Estructura jerárquica de CSI-2: CSI-2 consta de capa de aplicación, capa de protocolo y capa física.

La capa de protocolo consta de tres capas:

capa de empaquetado/desempaquetado de píxeles/bytes,

.LLP (Protocolo de bajo nivel) 层,

Gestión de .LANE;

La capa física especifica el medio de transmisión, las características eléctricas, los circuitos de E/S y los mecanismos de sincronización. La capa física cumple con el estándar de la Alianza MIPI para D-PHY, y D-PHY es un estándar común para varios grupos de trabajo MIPI; todos CSI-2 Los receptores y transmisores deben admitir reloj continuo, puede optar por admitir reloj discontinuo; en el modo de reloj continuo, la línea de reloj entre los paquetes de datos mantiene el modo HS, y en el modo de reloj discontinuo, la línea de reloj entre los paquetes de datos mantiene el estado LP11.

La organización ha reunido a veteranos fabricantes de software y hardware en la industria, incluido el mayor fabricante de chips para teléfonos móviles TI, el fabricante líder de chips multimedia audiovisuales ST, el gigante mundial de teléfonos móviles Nokia, el líder del núcleo de procesadores ARM y el creador de la sistema operativo móvil Symbian. Con la incorporación de fabricantes de peso como Freescale, Intel, Samsung y Ericsson, MIPI ha sido reconocido gradualmente por la Organización Internacional de Normalización.

interfaz DSI

La Alianza Internacional de Procesadores de la Industria Móvil (MIPI) ha lanzado oficialmente la Especificación de Interfaz Serial de Pantalla (DSI) para teléfonos móviles. DSI se basa en la especificación de capa física D-PHY de la interconexión serial escalable de alta velocidad y bajo consumo de MIPI. La capa física basada en SLVS admite velocidades de datos de hasta 1 Gbps mientras genera un ruido mínimo.

Basado en la tecnología central D-PHY, DSI agrega funciones para satisfacer las necesidades de los subsistemas de visualización de dispositivos móviles, incluido el modo de bajo consumo, la comunicación bidireccional, la compatibilidad con el idioma nativo para píxeles de 16, 18 y 24 bits y una única interfaz para controlar 4 capacidades de pantalla y compatibilidad con paneles con y sin búfer.

"Este estándar brinda beneficios significativos a una amplia gama de sistemas móviles, desde dispositivos simples de gama baja hasta teléfonos inteligentes de alta complejidad y plataformas portátiles más grandes", dijo Dick Lawrence, presidente del MIPI Display Working Group, en un comunicado. La industria ha estado esperando la unificación en un estándar abierto, y SDI proporciona la tecnología obligatoria para impulsar esta transición.

La interfaz serial generalmente adopta una estructura diferencial y utiliza una señal diferencial de varios cientos de mV para transmitir datos entre los extremos receptor y receptor. En comparación con el paralelo, la relación en serie ahorra el área de cableado de la placa PCB y mejora la utilización del espacio; la señal diferencial mejora su propia capacidad antiinterferencias EMI y reduce la interferencia con otras señales; la oscilación de bajo voltaje puede alcanzar una mayor velocidad velocidad, menor consumo de energía.

MIPI aún es una especificación en desarrollo, y sus futuras direcciones de mejora incluyen el uso de M-PHY con un reloj integrado de mayor velocidad como capa física, el desarrollo de CSI/DSI a una versión superior, la mejora de la interfaz DigRF V4 entre la banda base y los chips RF, y definición de interfaz de almacenamiento de alta velocidad UFS (principalmente organización JEDEC), etc. Por supuesto, el éxito final de MIPI también depende de la elección del mercado.

En la actualidad, el mercado de terminales requiere nuevos diseños con menor consumo de energía, mayor tasa de transferencia de datos y menor huella de PCB Bajo esta enorme presión, algunas alternativas inteligentes y rentables han comenzado a ser utilizadas gradualmente por los diseñadores relevantes. Entre las diversas interfaces diferenciales en serie basadas en estándares que se utilizan en la actualidad, la interfaz MIPI está creciendo extremadamente rápido en el campo de los dispositivos portátiles móviles sensibles a la energía y de alto rendimiento. El principal impulsor de este crecimiento es la adopción generalizada de los protocolos MIPI Display Serial Interface (DSI) y Camera Serial Interface (CSI-2) en módulos de banda base y pantalla/cámara . DSI y CSI-2 son protocolos de nivel lógico para pantallas y cámaras, respectivamente, y administran, envían errores y comunican datos entre el host y los periféricos a través de la interconexión física. MIPI D-PHY especifica las características físicas y eléctricas de la capa física que conecta procesadores y periféricos.Estas interfaces MIPI están diseñadas específicamente para servir al mercado de dispositivos móviles.

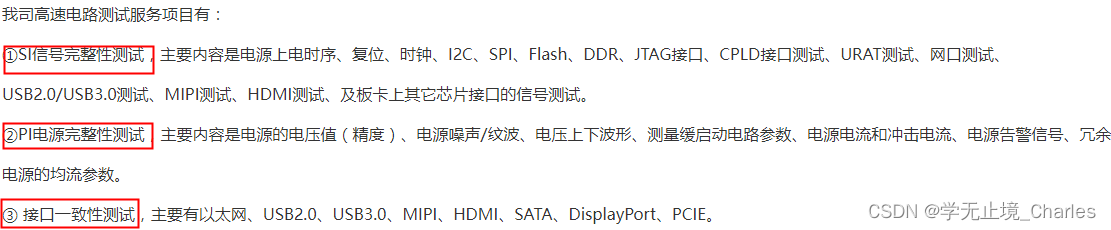

Elementos de prueba del circuito de alta velocidad:

1. Prueba de integridad de la señal SI

2. Prueba de integridad de potencia PI

3. Prueba de consistencia de la interfaz