1. Información general

- Propósito de la redacción

Este documento presentará el método de depuración de LCD en el módulo Display Engine de la plataforma Sunxi.

- Métodos de depuración de LCD y métodos de depuración.

- Escritura del controlador LCD.

- Explicación de cada atributo bajo el nodo lcd0.

- Configuración típica de la interfaz LCD.

Ámbito de aplicación: configuración de parámetros de pantalla LCD en la plataforma sunxi DE1.0/DE2.0.

2 Introducción a términos relacionados

| el término | explicar |

|---|---|

| SUNXI | Serie Allwinner de plataformas de hardware SoC |

| LCD | Pantalla de cristal líquido |

| MIPI | Interfaz de procesador de la industria móvil |

| DSI | Mostrar interfaz serie, mostrar interfaz serie |

| I8080 | Interfaz Intel 8080LCD |

| RGB | Esto se refiere a una interfaz LCD que envía componentes RGB sin ninguna codificación. |

| LVDS | Señalización diferencial de bajo voltaje Una interfaz LCD caracterizada por transmisión diferencial y de bajo voltaje |

3 especificaciones de circuitos integrados

Especificaciones relacionadas con la interfaz LCD:

-

Admite pantalla dual y pantalla diferencial. Es decir, el contenido de la pantalla puede ser diferente, la resolución de la pantalla puede ser diferente y la interfaz de la pantalla también puede ser diferente.

-

Admite interfaz MIPI-DSI, cantidad uno. La resolución máxima admitida es 1920x1200@60, el ancho y el alto no deben exceder los 2048 y el reloj de píxeles no debe exceder los 180MHz.

-

Admite interfaz RGB, cantidad 2. Entre ellos, la pantalla principal admite RGB666 paralelo y la pantalla secundaria admite RGB888 en paralelo. La interfaz RGB paralela admite una resolución máxima de 1920x1200 @ 60, y el ancho y alto no deben exceder 2048, como

Se admiten relojes Prime que no superen los 180 MHz. O dos interfaces RGB en serie, la resolución máxima de RGB en serie no supera 800*480@60

- Admite dos interfaces LVDS de doble enlace, que admiten una resolución máxima de 1920 x 1200 @ 60, un ancho y alto que no superan los 2048 y un reloj de píxeles que no supera los 180 MHz. O 4 conexiones LVDS de enlace único

puerto, la resolución admite hasta 1366*768@60.

-

Dos interfaces I8080. La resolución admite hasta 800*480@60.

-

La interfaz LVDS admite la visualización simultánea de señales. Cada dos interfaces LVDS de enlace único deben conectarse a la misma pantalla con la misma interfaz LVDS, y se enviarán los mismos datos a las dos pantallas para garantizar la misma señal. entonces

Teóricamente el T509 puede lograr 4 pantallas, de las cuales las dos primeras y las dos últimas pueden tener diferentes resoluciones, las resoluciones entre las dos deben ser iguales y deben estar conectadas a la misma pantalla LCD.

ilustrar

En un escenario de múltiples pantallas, las interfaces anteriores se pueden combinar libremente, excepto que se debe usar MIPI-DSI en la pantalla principal.

Habilidad

Una interfaz LVDS de doble enlace tiene un total de 20 líneas. Se puede dividir en dos interfaces LVDS de enlace único, asumiendo lvds0 y lvds1. Al seleccionar un enlace único para visualización, se debe seleccionar lvds0.

4 Introducción al módulo

4.1 Pasos para agregar el controlador de pantalla

- Para Linux 4.9 y versiones inferiores, es necesario modificar un total de tres lugares (es decir, los primeros tres elementos a continuación). Para Linux 5.4, es necesario modificar cuatro lugares. Para obtener más detalles, consulte la ubicación del código fuente del controlador de pantalla. .

• Repositorio de código fuente de Linux.

• Repositorio de código fuente de uboot. También hay controladores de pantalla en uboot, cuyo propósito es mostrar el logotipo.

• Almacén de configuración dts a nivel de placa. El propósito es configurar algunos parámetros de configuración LCD comunes a través de board.dts. Para Linux 4.9, esta configuración tiene efecto tanto en el kernel como en uboot. Para Linux-5.4, consulte el siguiente artículo.

• Para Linux5.4, es necesario configurar un almacén de configuración dts a nivel de placa específico de uboot adicional.

-

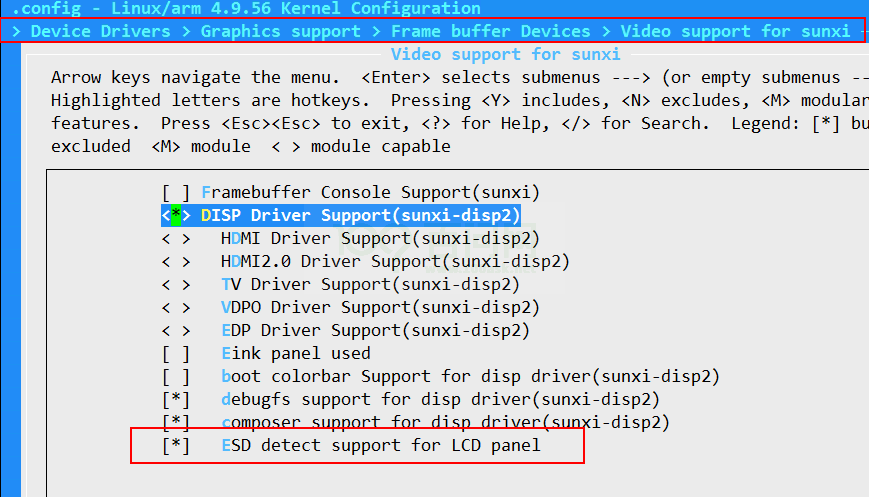

Asegúrese de que la configuración del kernel del marco de visualización Allwinner esté habilitada; consulte las instrucciones de configuración de menuconfig.

-

Prepare los siguientes materiales e información con anticipación:

• Manual de pantalla. Describe principalmente la información básica y características eléctricas de la pantalla, etc., y la solicita al fabricante de la pantalla.

• Manual del controlador IC. Describe principalmente la información detallada de la pantalla IC. Aquí principalmente se explica detalladamente cada comando, lo cual es útil para nuestra inicialización y personalización, solicítelo al fabricante de la pantalla.

• Información de sincronización de pantalla. Por favor, solicítelo al fabricante de la pantalla. Consulte la descripción del parámetro de sincronización de pantalla para obtener más información.

• Código de inicialización de pantalla. , consulte al fabricante de la pantalla. Generalmente, las pantallas DSI e I8080 requieren comandos de inicialización para inicializar la pantalla.

• Multímetro. Ajustar la pantalla no puede evitar medir voltajes relevantes.

-

Antes de agregar el controlador de pantalla, primero debe comprenderlo. Consulte el desglose del controlador de pantalla.

-

Localice el tipo de pantalla a través de la información del paso 3 y luego seleccione un controlador de pantalla existente del mismo tipo como plantilla para agregar el controlador de pantalla o modificarlo directamente.

-

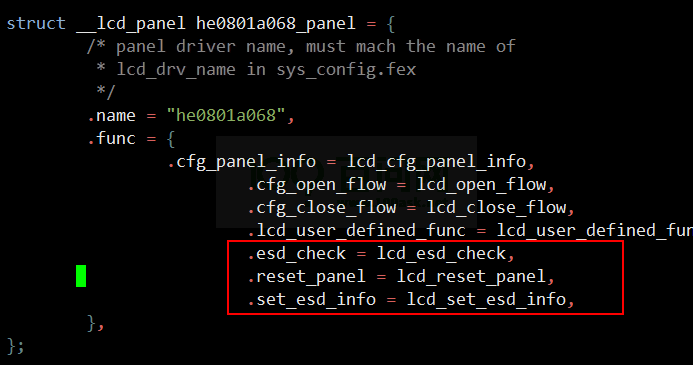

Modifique panel.c y panel.h en el directorio del controlador de pantalla. Agregue el puntero variable que acaba de agregar strcut_lcd_panel a la variable de estructura global panel_array. Se agregó el sonido strcut lcd_panel en panel.h

brillante.

-

Modifique el Makefile. Agregue el controlador de pantalla .o que acaba de agregar a disp-objs en el archivo Makefile en el nivel superior del directorio del controlador de pantalla LCD.

-

Modifique lcd0 en board.dts. Puede consultar la interfaz RGB, la interfaz MIPI-DSI, la interfaz I8080 y la interfaz LVDS, que presenta las configuraciones típicas de varias interfaces. Descripción de los parámetros de hardware, este capítulo contiene todas las secciones lcd0

Haga clic en las propiedades configurables para obtener una explicación detallada.

- Compile uboot, kernel, paquete y programa. Tenga en cuenta que los diferentes SDK tienen diferentes métodos de compilación y algunos SDK no compilan uboot de forma predeterminada.

- depurar. A través de métodos de depuración, podemos localizar inicialmente el problema y existen preguntas frecuentes que también son útiles para el ajuste de la pantalla.

4.2 Instrucciones del controlador de pantalla

4.2.1 Ubicación del código fuente del controlador de pantalla

Núcleo de la versión Linux 3.4:

linux3-4/drivers/video/sunxi/disp2/disp/lcd/

Núcleo de la versión Linux 3.10:

linux3-10/drivers/video/sunxi/disp2/disp/lcd/

Kernel Linux versión 4.9 y superior:

linux-4.9/drivers/video/fbdev/sunxi/disp2/disp/lcd/

uboot-2014:

brandy/u-boot-2014.07/drivers/video/sunxi/disp2/disp/lcd

uboot-2018:

brandy/brandy-2.0/u-boot-2018/drivers/video/sunxi/disp2/disp/lcd

Configuración a nivel de placa, donde "modelo de chip", como R818, y "nombre de placa", como demostración, reemplácelo de acuerdo con la situación real.

dispositivo/config/chips/modelo de chip/configs/nombre de la placa/board.dts

Configuración a nivel de placa Uboot utilizada para Linux5.4:

dispositivo/config/chips/modelo de chip/configs/nombre de la placa/uboot-board.dts

Configuración a nivel de placa del kernel utilizada para Linux 5.4:

dispositivo/config/chips/modelo de chip/configs/nombre de la placa/linux-5.4/board.dts

4.2.2 instrucciones de configuración de menuconfig

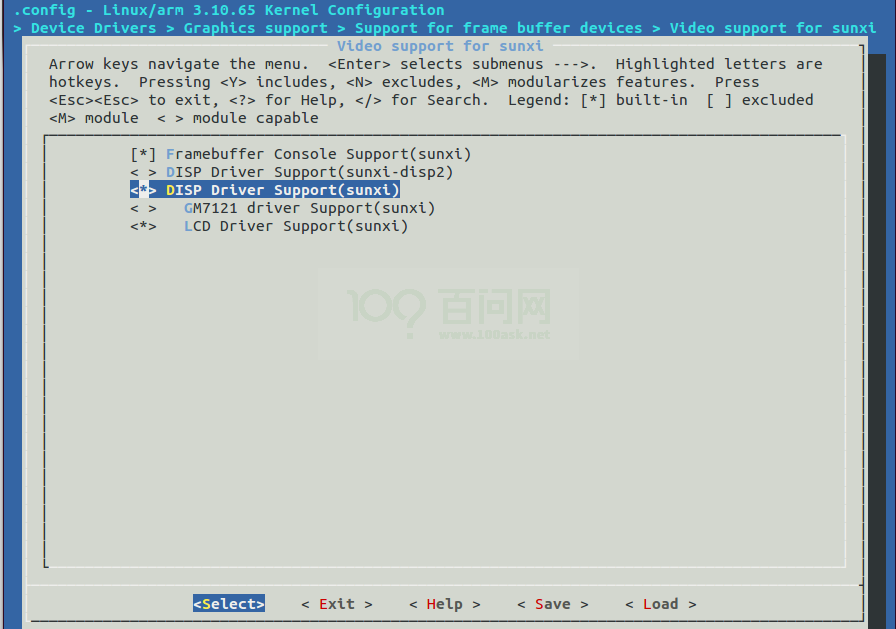

Los códigos relacionados con la pantalla LCD se incluyen en el módulo del controlador disp. Ingrese al directorio raíz del kernel y ejecute make ARCH=arm menuconfig o make ARCH=arm64 menuconfig (plataforma de 64 bits) para ingresar a la interfaz de configuración principal.

fideos. y sigue estos pasos:

Plataformas correspondientes DE1.0: R6 (linux-3.10), R16 (linux-3.4).

Plataformas correspondientes DE2.0: excepto R6 y R16.

Tomando R40 como ejemplo, el directorio de configuración específico es: Controladores de dispositivo->Soporte de gráficos->Soporte para dispositivos frame buffer->Soporte de video para sunxi -> Soporte de controlador DISP (sunxi-disp2).

4.2.3 Descomposición del controlador de pantalla

En la ubicación del código fuente del controlador de pantalla, se divide principalmente en cuatro tipos de archivos:

-

panel.c y panel.h, cuando el usuario agrega un nuevo controlador de pantalla, estos dos archivos deben modificarse y la variable de estructura de pantalla debe agregarse a la variable de estructura global panel_array.

-

lcd_source.c y lcd_source.h, estos dos archivos implementan las interfaces de funciones utilizadas por el controlador de pantalla, como el interruptor de encendido, gpio, interfaz de lectura y escritura dsi, etc. Los usuarios no necesitan modificarlos, solo necesitan usarlos. .

-

controlador de pantalla. Además de los archivos fuente mencionados anteriormente, generalmente un archivo c y un archivo h representan un controlador de pantalla.

-

En el nivel superior de la ubicación del código fuente del controlador de pantalla, hay un archivo Makefile que el usuario debe modificar.

Podemos abrir drivers/video/fbdev/sunxi/disp2/disp/lcd/default_panel.c como ejemplo del controlador de pantalla al final del archivo.

struct __lcd_panel default_panel = {

/* panel driver name, must mach the lcd_drv_name in board.dts */

.name = "default_lcd",

.func = {

.cfg_panel_info = LCD_cfg_panel_info,

.cfg_open_flow = LCD_open_flow,

.cfg_close_flow = LCD_close_flow,

}

,

};

El nombre de miembro de la variable global default_panel debe ser coherente con lcd_driver_name, lo que está relacionado con si el controlador puede encontrar el archivo especificado.

Lo siguiente es la inicialización del miembro func, donde se implementan principalmente tres funciones de devolución de llamada. LCD_cfg_panel_info, LCD_open_flow y LCD_close_flow.

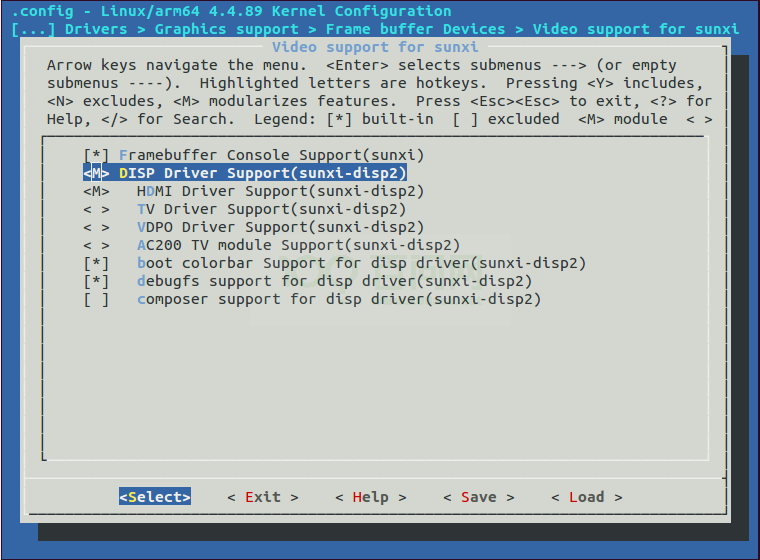

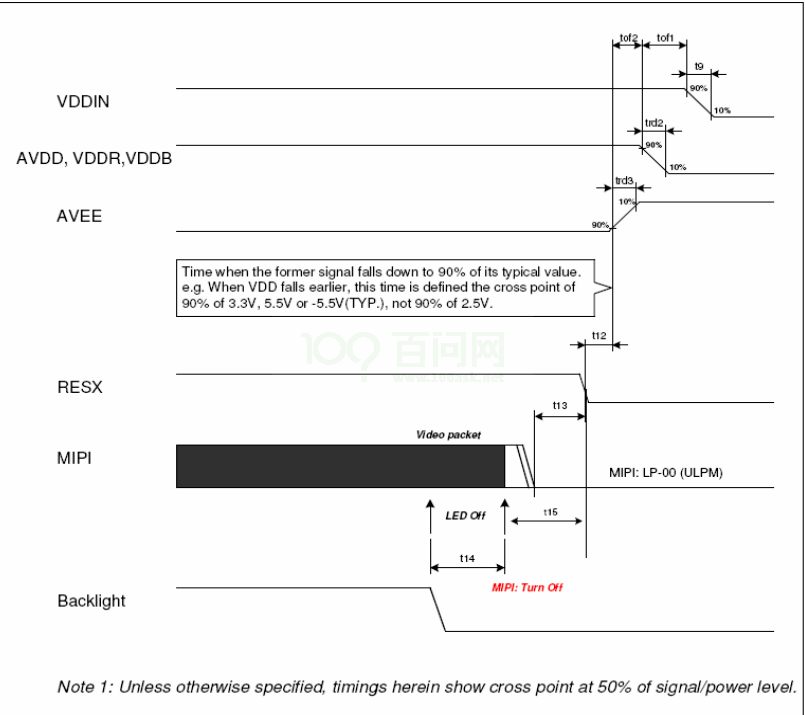

El proceso de encender y apagar la pantalla es el proceso de encender y apagar la pantalla, que es la secuencia de encendido y la secuencia de apagado en el manual de la pantalla o el manual del controlador IC.

El proceso de operación para cambiar la pantalla se muestra en la siguiente figura.

Entre ellas, LCD_open_flow y LCD_close_flow se denominan funciones de proceso de cambio de pantalla, y las funciones en el cuadro, como LCD_power_on, se denominan funciones de paso de cambio de pantalla.

Para pantallas LCD que no requieren operaciones de inicialización, como pantallas lvds, pantallas RGB, etc., las funciones LCD_panel_init y LCD_panel_exit pueden estar vacías.

Función: LCD_open_flow

Función: La función LCD_open_flow solo se llamará una vez durante la inicialización del sistema. Ejecutar cada LCD_OPEN_FUNC significa registrar la función de paso de apertura de pantalla correspondiente. Regístrese primero y ejecute primero, pero no se ejecuta inmediatamente.

Ejecute la función de paso de apertura de pantalla.

prototipo:

static s32 LCD_open_flow(u32 sel)

Las funciones comúnmente utilizadas son:

static __s32 LCD_open_flow(__u32 sel)

{

LCD_OPEN_FUNC(sel, LCD_power_on,10);

LCD_OPEN_FUNC(sel, LCD_panel_init, 50);

LCD_OPEN_FUNC(sel, sunxi_lcd_tcon_enable, 100);

LCD_OPEN_FUNC(sel, LCD_bl_open, 0);

return 0;

}

Como arriba, llamar a LCD_OPEN_FUNC cuatro veces registra cuatro funciones de devolución de llamada, correspondientes a cuatro procesos de apertura de pantalla. Regístrese primero y ejecute primero. De hecho, corresponde al usuario decidir cuántas funciones registrar, siempre que sea razonable.

- LCD_power_on significa encender la fuente de alimentación de la pantalla LCD y luego retrasarla durante 10 ms; este paso se usa generalmente para encender la fuente de alimentación relacionada con la pantalla LCD y los pines relacionados, como el pin de reinicio. Aquí, generalmente se utilizan la descripción de la función de control de potencia y el control de pines.

Descripción de la función a operar.

- LCD_panel_init es la pantalla de inicialización, y luego se retrasa 50 ms; para las pantallas que no requieren inicialización, este paso se puede omitir. Esta función generalmente se usa para enviar comandos de inicialización a la pantalla para la inicialización de la pantalla. Si es una pantalla DSI, mira la fase DSI.

Con respecto a la descripción de la función, si es una pantalla I8080, use la descripción de la función de la interfaz I8080. Si se trata de otras situaciones como i2c o spi, puede usar la inicialización de la interfaz serial iic/spi, o puede usar GPIO para simular.

-

sunxi_lcd_tcon_enable activa TCON y retrasa 100 ms; este paso es fijo y significa comenzar a enviar señales de imagen.

-

LCD_bl_open enciende la luz de fondo y luego retrasa 0 ms. Encienda la luz de fondo después de completar los primeros tres pasos, para que no vea parpadeos. Consulte la descripción de la función de control de retroiluminación para conocer las funciones que se utilizan generalmente aquí.

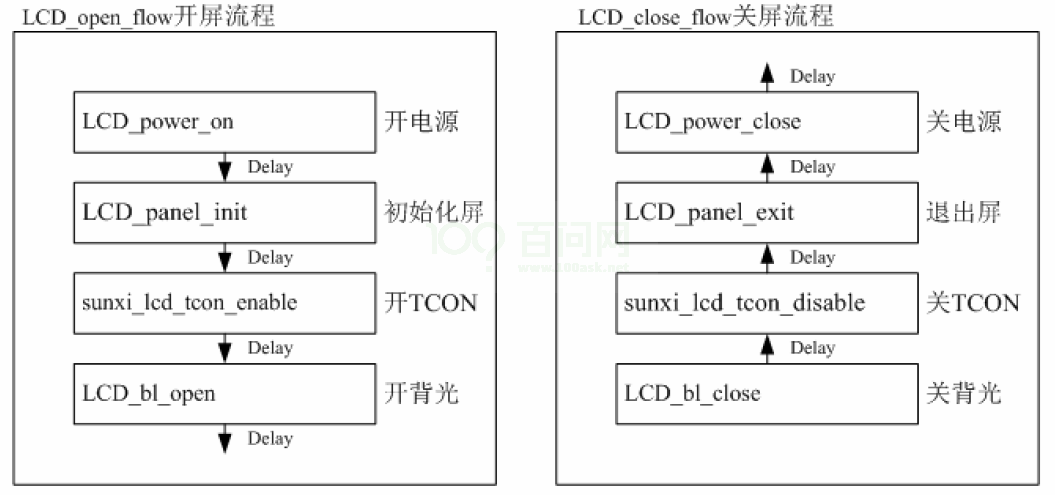

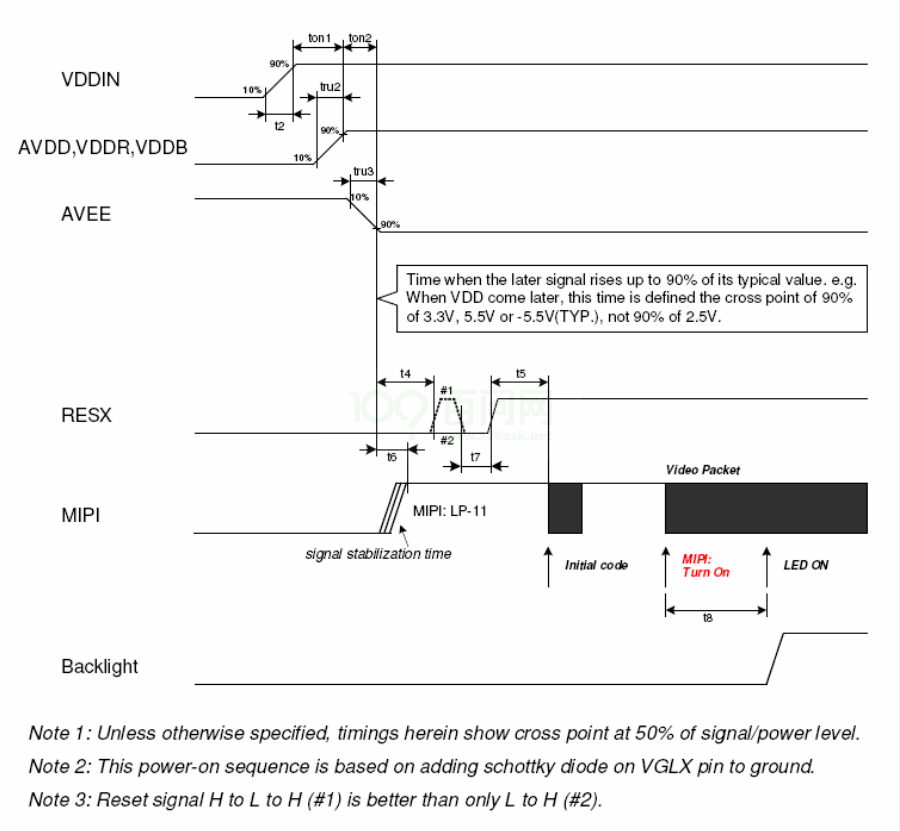

Como se muestra a continuación, este es un diagrama de secuencia de encendido típico en el manual de pantalla. Cuando escribimos el controlador de pantalla, también debemos prestar atención al retraso.

Función: LCD_OPEN_FUNC

Función: Registre la función del paso de apertura de pantalla en el proceso de apertura de pantalla. Recuerde, esto es registro, no ejecución.

prototipo:

void LCD_OPEN_FUNC(__u32 sel, LCD_FUNC func, __u32 delay)

Descripción de parámetros:

func es un puntero de función, su tipo es: void (*LCD_FUNC) (__u32 sel) Las funciones definidas por el usuario también deben usar una forma unificada. Por ejemplo:

void user_defined_func(__u32 sel)

{

//do something

}

El retraso es el tiempo de retraso después de ejecutar este paso, la unidad de tiempo es milisegundos.

El segundo parámetro de LCD_OPEN_FUNC es la duración del retardo de los dos pasos antes y después, la unidad es ms. Tenga en cuenta que el valor aquí debe completarse de acuerdo con las regulaciones del manual de la pantalla. Completar aleatoriamente puede causar una inicialización anormal de la pantalla o El tiempo de cambio de pantalla expirará.

largo, afectando la experiencia del usuario.

Correspondiente a LCD_open_flow es LCD_close_flow, que se utiliza para registrar la función de cierre de pantalla. Utilice LCD_CLOSE_FUNC para registrar la función. Regístrese primero y ejecute primero. Aquí, la función de devolución de llamada solo se registra y no se ejecuta inmediatamente.

DE ACUERDO.

static s32 LCD_close_flow(u32 sel)

{

/* close lcd backlight, and delay 0ms */

LCD_CLOSE_FUNC(sel, LCD_bl_close, 0);

/* close lcd controller, and delay 0ms */

LCD_CLOSE_FUNC(sel, sunxi_lcd_tcon_disable, 50);

/* open lcd power, than delay 200ms */

LCD_CLOSE_FUNC(sel, LCD_panel_exit, 100);

/* close lcd power, and delay 500ms */

LCD_CLOSE_FUNC(sel, LCD_power_off, 0);

return 0;

}

-

Primero apague la luz de fondo, para que el usuario no vea el proceso de parpadeo durante todo el proceso de apagado de la pantalla.

-

Es necesario cerrar TCON, lo que significa dejar de enviar datos. Retraso otros 50 ms.

-

Ejecute el código de apagado de la pantalla y espere 200 ms (este paso se puede omitir para las pantallas que no requieren inicialización).

-

Finalmente apague la alimentación y retrase 0 ms.

La siguiente figura es un diagrama típico de sincronización de pantalla apagada.

Función: LCD_cfg_panel_info

Función: Parámetros extendidos de TCON configurados, como la función gamma y la función de mapeo de color.

prototipo:

static void LCD_cfg_panel_info(__panel_extend_para_t * info)

Los parámetros extendidos de TCON solo se pueden configurar en el archivo de pantalla. Para la definición de los parámetros, consulte los parámetros relacionados con el efecto de visualización.

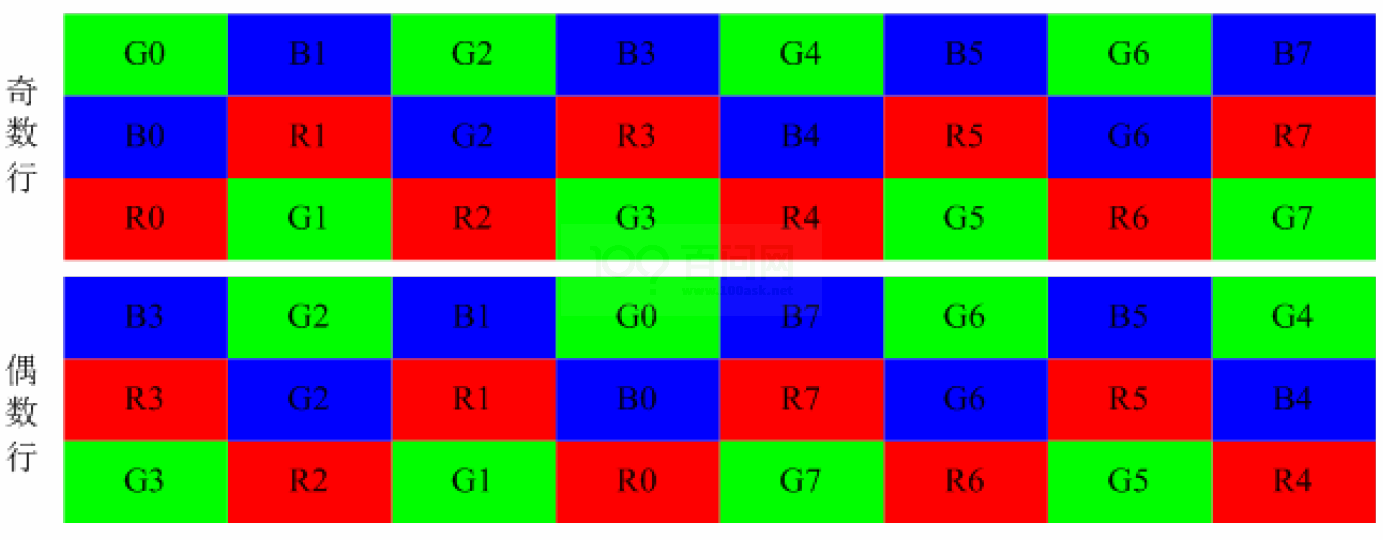

Si se requiere corrección de gamma o mapeo de color, establezca el parámetro de habilitación del módulo correspondiente en 1 en board.dts, lcd_gamma_en, lcd_cmap_en, y complete 3 tablas de coeficientes, lcd_gamma_tbl,

lcd_cmap_tbl, la parte del código se muestra a continuación. Nota: gamma, la plantilla proporciona 18 valores de puntos de inflexión y luego interpola todos los valores (255). Si crees que no está lo suficientemente detallado, puedes agregarlo a la tabla correspondiente.

niño. El tamaño de cmap_tbl es fijo y el tamaño de la tabla no se puede reducir ni aumentar.

La entrada final de la tabla gamma generada se compone de tres valores gamma, rgb, cada uno de los cuales ocupa 8 bits. En la plantilla proporcionada actualmente, los tres valores gamma son iguales.

static void LCD_cfg_panel_info(struct panel_extend_para *info)

{

u32 i = 0, j = 0;

u32 items;

u8 lcd_gamma_tbl[][2] = {

/* {input value, corrected value} */

{0, 0},

{15, 15},

{30, 30},

{45, 45},

{60, 60},

{75, 75},

{90, 90},

{105, 105},

{120, 120},

{135, 135},

{150, 150},

{165, 165},

{180, 180},

{195, 195},

{210, 210},

{225, 225},

{240, 240},

{255, 255},

};

u32 lcd_cmap_tbl[2][3][4] = {

{

{LCD_CMAP_G0, LCD_CMAP_B1, LCD_CMAP_G2, LCD_CMAP_B3},

{LCD_CMAP_B0, LCD_CMAP_R1, LCD_CMAP_B2, LCD_CMAP_R3},

{LCD_CMAP_R0, LCD_CMAP_G1, LCD_CMAP_R2, LCD_CMAP_G3},

},

{

{LCD_CMAP_B3, LCD_CMAP_G2, LCD_CMAP_B1, LCD_CMAP_G0},

{LCD_CMAP_R3, LCD_CMAP_B2, LCD_CMAP_R1, LCD_CMAP_B0},

{LCD_CMAP_G3, LCD_CMAP_R2, LCD_CMAP_G1, LCD_CMAP_R0},

},

};

items = sizeof(lcd_gamma_tbl) / 2;

for (i = 0; i < items - 1; i++) {

u32 num = lcd_gamma_tbl[i + 1][0] - lcd_gamma_tbl[i][0];

for (j = 0; j < num; j++) {

u32 value = 0;

value =

lcd_gamma_tbl[i][1] +

((lcd_gamma_tbl[i + 1][1] -

lcd_gamma_tbl[i][1]) * j) / num;

info->lcd_gamma_tbl[lcd_gamma_tbl[i][0] + j] =

(value << 16) + (value << 8) + value;

}

}

info->lcd_gamma_tbl[255] =

(lcd_gamma_tbl[items - 1][1] << 16) +

(lcd_gamma_tbl[items - 1][1] << 8) + lcd_gamma_tbl[items - 1][1];

memcpy(info->lcd_cmap_tbl, lcd_cmap_tbl, sizeof(lcd_cmap_tbl));

}

4.2.4 Descripción de la función de retardo

Nombre: sunxi_lcd_delay_ms / sunxi_lcd_delay_us

Función: Función de retardo, respectivamente nivel de milisegundos/retardo de nivel de microsegundos.

Ejemplo: s32 sunxi_lcd_delay_ms(u32 ms) / s32 sunxi_lcd_delay_us(u32 us)

4.2.5 Descripción de la función de habilitación de datos de imagen

Nombre: sunxi_lcd_tcon_enable / sunxi_lcd_tcon_disable

Función: Encienda el controlador LCD y comience a actualizar la pantalla LCD. Apague el controlador LCD y deje de actualizar los datos.

Ejemplo:void sunxi_lcd_tcon_enable(u32 screen_id)

anular sunxi_lcd_tcon_disable (u32 screen_id)

4.2.6 Descripción de la función de control de retroiluminación

Ejemplo: sunxi_lcd_backlight_enable / sunxi_lcd_backlight_disable

Función: enciende/apaga la luz de fondo, operando el gpio configurado por lcd_bl en board.dts. Ver lcd_bl_en.

Ejemplo:void sunxi_lcd_backlight_enable(u32 screen_id)

void sunxi_lcd_backlight_disable (u32 screen_id)

Nombre: sunxi_lcd_pwm_enable / sunxi_lcd_pwm_disable

Función: enciende/apaga el controlador pwm. Cuando se enciende, el pwm emitirá la forma de onda pwm. Correspondiente al pwm correspondiente a lcd_pwm_ch.

Ejemplo: s32 sunxi_lcd_pwm_enable (u32 screen_id)

s32 sunxi_lcd_pwm_disable (u32 screen_id)

4.2.7 Descripción de la función de control de potencia

Nombre: sunxi_lcd_power_enable / sunxi_lcd_power_disable

Función: Enciende/apaga la alimentación de la pantalla LCD, la operación es lcd_power/lcd_power1/lcd_power2 en board.dts (pwr_id identifica el índice de potencia).

Ejemplo: void sunxi_lcd_power_enable(u32 screen_id, u32 pwr_id)

anular sunxi_lcd_power_disable (u32 screen_id, u32 pwr_id)

- pwr_id = 0: corresponde a lcd_power en board.dts.

- pwr_id = 1: corresponde a lcd_power1 en board.dts.

- pwr_id = 2: corresponde a lcd_power2 en board.dts.

- pwr_id = 3: corresponde a lcd_power3 en board.dts.

Función: sunxi_lcd_pin_cfg

Función: Configurar LCD IO.

Ejemplo: s32 sunxi_lcd_pin_cfg (u32 screen_id, u32 bon)

Descripción: Configure los pines data/clk y otros pines del lcd, correspondientes a lcdd0-lcdd23/lcddclk/lcdde/lcdhsync/lcdvsync en board.dts.

Dado que dsi es un pin dedicado, la pantalla de la interfaz dsi no necesita configurar este conjunto de pines en board.dts, pero los pines correspondientes también se activarán y desactivarán en esta interfaz de función.

Bon: 1: significa activado, 0: significa configurado para desactivar el estado.

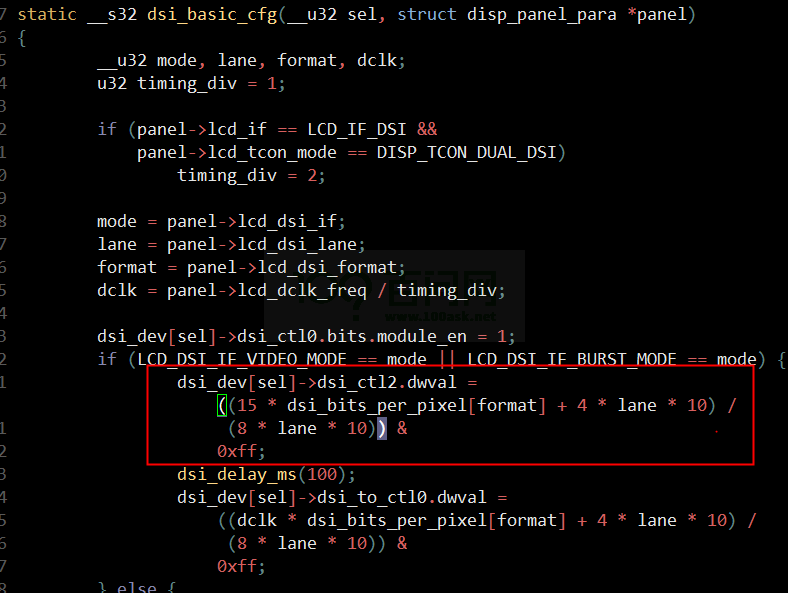

4.2.8 Descripción de funciones relacionadas con DSI

La mayoría de las pantallas MIPI DSI deben inicializarse, utilizando el modo LP del canal DSI-D0 para la inicialización. Las funciones de interfaz proporcionadas se describen a continuación:

Nombre: sunxi_lcd_dsi_clk_enable / sunxi_lcd_dsi_clk_disble

Función: Sólo se utiliza en la pantalla de la interfaz dsi. Habilita/deshabilita la salida de señal de reloj de alta velocidad de dsi. Debe llamarse durante la inicialización.

Ejemplo: s32 sunxi_lcd_dsi_clk_enable(u32 scree_id)

s32 sunxi_lcd_dsi_clk_disable (u32 scree_id)

Función: sunxi_lcd_dsi_dcs_wr

Función: operación de escritura dcs en la pantalla.

Ejemplo:__s32 sunxi_lcd_dsi_dcs_wr(__u32 sel,__u8 cmd,__u8* para_p,__u32 para_num)

Descripción de parámetros:

• cmd: dcs escribe el contenido del comando.

• para_p: dirección inicial del parámetro del comando de escritura dcs.

• para_num: el número de parámetros para el comando de escritura dcs, en bytes.

Función: sunxi_lcd_dsi_dcs_wr_2para

Función: operación de escritura dcs en la pantalla.Este comando toma dos parámetros.

Ejemplo:__s32 sunxi_lcd_dsi_dcs_wr_2para(__u32 sel,__u8 cmd,__u8 para1,__u8 para2)

Descripción de parámetros:

• cmd: dcs escribe el contenido del comando.

• para1: El contenido del primer parámetro del comando de escritura dcs.

• para2: El contenido del segundo parámetro del comando de escritura dcs.

sunxi_dsi_dcs_wr_0para,sunxi_dsi_dcs_wr_1para,sunxi_dsi_dcs_wr_3para,sunxi_dsi_dcs_wr_4para,

La definición de sunxi_dsi_dcs_wr_5para es similar a la de dsi_dcs_wr_2para, la diferencia es la cantidad de parámetros.

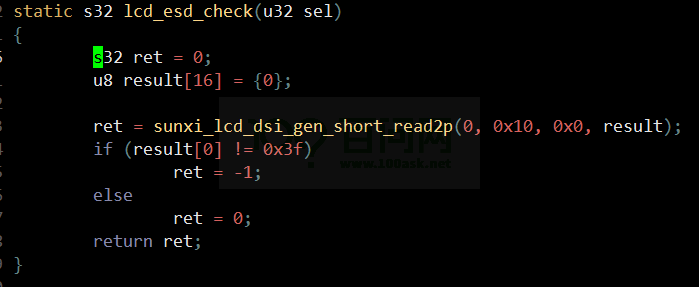

Función: sunxi_lcd_dsi_dcs_read

Función: operación de lectura dsi.

Ejemplo: s32 sunxi_lcd_dsi_dcs_read(u32 sel, u8 cmd, u8 resultado, u32 num_p)

Descripción de parámetros:

• sel, mostrar identificación.

• cmd, el registro a leer.

• resultado, una matriz utilizada para almacenar la interfaz de lectura. El usuario debe asegurarse de que haya suficiente espacio para guardar la interfaz de lectura.

• num_p, el puntero se utiliza para almacenar el número de bytes a leer y el usuario debe asegurarse de que no sea un puntero nulo.

4.2.9 Descripción de la función de la interfaz I8080

El controlador de pantalla proporciona 5 funciones de interfaz para su uso. como sigue:

Función: sunxi_lcd_cpu_write

Función: Establece el registro especificado de la pantalla de la CPU al valor especificado.

Ejemplo: void sunxi_lcd_cpu_write(__u32 sel, __u32 index, __u32 data)

El contenido de la función es:

Void sunxi_lcd_cpu_write(__u32 sel, __u32 index, __u32 data)

{

sunxi_lcd_cpu_write_index(sel, index);

sunxi_lcd_cpu_wirte_data(sel, data);

}

Se implementan dos operaciones de escritura en el bus 8080.

sunxi_lcd_cpu_write_index implementa la primera operación de escritura. En este momento, el pin PIN RS (A1) es de nivel bajo y el contenido de datos en los datos del bus es el valor del índice del parámetro.

Sunxi_lcd_cpu_wirte_data implementa la segunda operación de escritura. En este momento, el pin PIN RS (A1) es de nivel alto y el contenido de datos en los datos del bus es el valor de los datos del parámetro.

Función: sunxi_lcd_cpu_write_index

Función: establece la pantalla de la CPU en el registro especificado.

prototipo:

void sunxi_lcd_cpu_write_index(__u32 sel,__u32 index)

Consulte sunxi_lcd_cpu_write para obtener instrucciones específicas.

Función: sunxi_lcd_cpu_write_data

Función: Establece el valor del registro de pantalla de la CPU al valor especificado.

prototipo:

void Sunxi_lcd_cpu_write_data(__u32 sel, __u32 data);

Función: tcon0_cpu_rd_24b_data

Función: operación de lectura.

prototipo:

s32 tcon0_cpu_rd_24b_data(u32 sel, u32 index, u32 *data, u32 size)

Descripción de parámetros:

• sel: identificación de visualización.

• índice: el registro a leer.

• datos: se utiliza para almacenar el puntero de matriz de la interfaz de lectura, el usuario debe asegurarse de que tenga suficiente espacio para almacenar datos.

• tamaño: Número de bytes a leer.

4.2.10 Descripción de la función de control de pines

Función: sunxi_lcd_gpio_set_value

Función: El pin LCD_GPIO PIN emite un nivel alto o bajo.

Ejemplo: s32 sunxi_lcd_gpio_set_value(u32 screen_id, u32 io_index, u32 value)

Descripción de parámetros:

• io_index = 0: Corresponde a lcd_gpio_0 en board.dts.

• io_index = 1: Corresponde a lcd_gpio_1 en board.dts.

• io_index = 2: Corresponde a lcd_gpio_2 en board.dts.

• io_index = 3: Corresponde a lcd_gpio_3 en board.dts.

• valor = 0: corresponde al nivel bajo de salida IO.

• Valor = 1: Corresponde al nivel alto de salida IO.

Solo se usa cuando el GPIO está definido como salida.

Función: sunxi_lcd_gpio_set_direction

Función: Configure el pin LCD_GPIO PIN en modo de entrada o salida.

prototipo:

s32 sunxi_lcd_gpio_set_direction(u32 screen_id, u32 io_index, u32 direction);

Descripción de parámetros:

• io_index = 0: Corresponde a lcd_gpio_0 en board.dts.

• io_index = 1: Corresponde a lcd_gpio_1 en board.dts.

• io_index = 2: Corresponde a lcd_gpio_2 en board.dts.

• io_index = 3: Corresponde a lcd_gpio_3 en board.dts.

• dirección = 0: La IO correspondiente se configura como entrada.

• dirección = 1: La IO correspondiente se establece en salida.

Algunas pantallas necesitan ser inicializadas. En la función de paso de apertura de pantalla, correspondiente a la función LCD_panel_init, se proporcionan varios métodos para inicializar la pantalla.

Para la pantalla DSI, se inicializa a través del canal DSI-D0. Para la pantalla de la CPU, se inicializa a través del bus 8080 y utiliza LCDIO (PD, PH). En este método de inicialización, los bits de pin de su bus

La definición de configuración es consistente con la pantalla de la CPU.

Las siguientes interfaces están definidas e implementadas en lcd_source.c y lcd_source.h cuyas rutas se mencionan en la descomposición del controlador de pantalla.

4.2.11 Inicialización mediante la interfaz serie iic/spi

El acceso del dispositivo iic/spi a la interfaz serie debe registrarse en el controlador de pantalla.

Utilice hardware spi para detectar o transferir IC para inicializar, como se muestra en el siguiente fragmento de código.

Primero llame a la función spi_init para inicializar el hardware spi. La función spi_init se puede dividir en varios pasos. Primero, obtenga el maestro; de acuerdo con la conexión real del hardware, seleccione spi (spi1 está seleccionado en el código). Si esto

Si el paso arroja un error que indica que spi no está configurado correctamente, comuníquese con la persona a cargo del controlador spi. El segundo paso es configurar el dispositivo spi, que incluye la velocidad máxima, el modo de transmisión spi y la cantidad de bits contenidos en cada palabra. Finalmente llame a spi_setup para completar

La relación entre maestro y dispositivo.

comm_out es un ejemplo de transferencia spi y el núcleo es la función spi_sync_transfer.

static int spi_init(void)

{

int ret = -1;

struct spi_master *master;

master = spi_busnum_to_master(1);

if (!master) {

lcd_fb_wrn("fail to get master\n");

goto OUT

}

spi_device = spi_alloc_device(master);

if (!spi_device) {

lcd_fb_wrn("fail to get spi device\n");

goto OUT;

}

spi_device->bits_per_word = 8;

spi_device->max_speed_hz = 60000000; /*50MHz*/

spi_device->mode = SPI_MODE_0;

ret = spi_setup(spi_device);

if (ret) {

lcd_fb_wrn("Faile to setup spi\n");

goto FREE;

}

lcd_fb_inf("Init spi1:bits_per_word:%d max_speed_hz:%d mode:%d\n",

spi_device->bits_per_word, spi_device->max_speed_hz,

spi_device->mode);

ret = 0;

goto OUT;

FREE:

spi_master_put(master);

kfree(spi_device);

spi_device = NULL;

OUT:

return ret;

}

static int comm_out(unsigned int sel, unsigned char cmd)

{

struct spi_transfer t;

if (!spi_device)

return -1;

DC(sel, 0);

memset(&t, 0, sizeof(struct spi_transfer));

t.tx_buf = &cmd;

t.len = 1;

t.bits_per_word = 8;

t.speed_hz = 24000000;

return spi_sync_transfer(spi_device, &t, 1);

}

Utilice el hardware i2c para inicializar la pantalla LCD y el adaptador IC. La función principal para inicializar el hardware i2c es i2c_add_driver, y lo que debe hacer es inicializar su parámetro struct i2c_driver.

it66121_id contiene el nombre del dispositivo y el índice del bus i2c (i2c0, i2c1...).

it66121_i2c_probe Si puede ingresar a esta función, puede comenzar a usar i2c. En el segmento de código, solo el parámetro cilent que se necesitará más adelante se asigna a una variable de puntero global.

it66121_match, esta es la tabla de coincidencias de dts. Dado que está agregando un controlador a disp2, la tabla de coincidencias aquí es la tabla de coincidencias de disp2. Esta tabla está relacionada con si se puede usar i2c. Por favor, preste atención.

Complete el formulario incorrecto.

La función tv_i2c_detect es muy crítica aquí. Esta función se llama antes que la función de sonda. Solo después de que se llame con éxito se puede comenzar a usar i2c. La llamada de strlcpy significa éxito.

normal_i2c es la lista de direcciones del dispositivo esclavo, completada con la dirección del dispositivo esclavo de la pantalla LCD o IC de transferencia y el índice i2c.

Si puede comenzar a usar I2C depende de si se llama a la función de sonda.

Usar i2c_smbus_write_byte_data o i2c_smbus_read_byte_data para leer y escribir puede satisfacer la mayoría de los escenarios.

#define IT66121_SLAVE_ADDR 0x4c

#define IT66121_I2C_ID 0

static const struct i2c_device_id it66121_id[] = {

{ "IT66121", IT66121_I2C_ID },

{ /* END OF LIST */ }

};

MODULE_DEVICE_TABLE(i2c, it66121_id);

static int it66121_i2c_probe(struct i2c_client *client, const struct i2c_device_id *id)

{

this_client = client;

return 0;

}

static const struct of_device_id it66121_match[] = {

{.compatible = "allwinner,sun8iw10p1-disp",},

{.compatible = "allwinner,sun50i-disp",},

{.compatible = "allwinner,sunxi-disp",},

{},

};

static int tv_i2c_detect(struct i2c_client *client, struct i2c_board_info *info)

{

const char *type_name = "IT66121";

if (IT66121_I2C_ID == client->adapter->nr) {

strlcpy(info->type, type_name, 20);

} else

pr_warn("%s:%d wrong i2c id:%d, expect id is :%d\n", __func__, __LINE__,

client->adapter->nr, IT66121_I2C_ID);

return 0;

}

static unsigned short normal_i2c[] = {IT66121_SLAVE_ADDR, I2C_CLIENT_END};

static struct i2c_driver it66121_i2c_driver = {

.class = I2C_CLASS_HWMON,

.id_table = it66121_id,

.probe = it66121_i2c_probe,

.remove = it66121_i2c_remove,

.driver = {

.owner = THIS_MODULE,

.name = "IT66121",

.of_match_table = it66121_match,

},

.detect = tv_i2c_detect,

.address_list = normal_i2c,

};

static void LCD_panel_init(u32 sel)

{

int ret = -1;

ret = i2c_add_driver(&it66121_i2c_driver);

if (ret) {

pr_warn("Add it66121_i2c_driver fail!\n");

return;

}

//start init chip with i2c

}

void it6612_twi_write_byte(it6612_reg_set* reg)

{

u8 rdata = 0;

u8 tmp = 0;

rdata = i2c_smbus_read_byte_data(this_client, reg->offset);

tmp = (rdata & (~reg->mask))|(reg->mask®->value);

i2c_smbus_write_byte_data(this_client, reg->offset, tmp);

}

4.2.12 Precauciones del controlador de pantalla U-boot

Los pasos para escribir controladores de pantalla en U-boot son los mismos que los del kernel, y los archivos de ruta del código están organizados de la misma manera. Aquí están las cosas a las que debe prestar atención.

1. Para acelerar la velocidad de visualización de U-boot, se adoptan llamadas asincrónicas entre varias funciones que abren la pantalla. El principio es utilizar la interrupción del temporizador para llamar regularmente a la función de apertura de la pantalla. Por lo tanto, en este caso, el El marco bootGUI está cargado y

No significa que se complete la apertura de la pantalla, pero cuando vea la pantalla LCD abierta terminará de imprimir.

Sugerencia: para aprovechar las ventajas de las llamadas asincrónicas, especifique el retraso requerido al registrar la devolución de llamada. Por ejemplo, el siguiente retraso de 10 ms utiliza la devolución de llamada asincrónica del temporizador. Durante este tiempo de 10 ms, uboot

Puede hacer otras cosas para lograr el propósito de las llamadas asincrónicas.

LCD_OPEN_FUNC(sel, LCD_power_on,10);

2. Las funciones sunxi_lcd_power_enable y sunxi_lcd_pin_cfg no se pueden llamar fuera de LCD_power_on; de lo contrario, uboot será anormal.

Estrictamente hablando, solo se puede llamar en la primera función de devolución de llamada registrada con LCD_OPEN_FUNC.

4.3 Interfaz RGB

4.3.1 Descripción general

A continuación se presentan los ejemplos de configuración y RGB de la plataforma Allwinner. En cuanto a la explicación detallada de cada atributo debajo de lcd0, consulte la descripción del parámetro de hardware.

La interfaz RGB también se denomina interfaz HV (sincronización horizontal y sincronización vertical) en la plataforma Allwinner.

Para inicialización de pantalla RGB:

Algunas pantallas LCD admiten funciones avanzadas como gamma, configuración de formato de píxeles, etc., pero el protocolo RGB en sí no admite transmisiones que no sean datos de imagen, por lo que la pantalla LCD no se puede configurar a través de los pines RGB.

Entonces, si obtiene una pantalla de interfaz RGB, no necesita un comando de inicialización o la pantalla proporcionará pines adicionales para que el SoC configure, como SPI e I2C.

4.3.2 pines de interfaz RGB

Para conocer los pines y funciones de SoC específicos (funciones de multiplexación de pines) de los pines anteriores, consulte la tabla de mux de pines. Los nombres de las funciones de multiplexación de pines generalmente comienzan con "LCDX_", donde X es un número.

El número de pines de datos no es necesariamente 24. RGB se subdivide en varias interfaces, que se seleccionan configurando lcd_hv_if.

| ancho de bits | ciclo de reloj | Cuente la cantidad y el formato del color. |

|---|---|---|

| 24 bits | 1 ciclo | 16,7 millones de colores, RGB888 |

| 18 bits | 1 ciclo | 262.000 colores, RGB666 |

| 16 bits | 1 ciclo | 65.000 colores, RGB565 |

| 6 bits | 3 ciclos | 262.000 colores, RGB666 |

| 6 bits | 3 ciclos | 65.000 colores, RGB565 |

ilustrar

El significado del número de ciclos de reloj: significa cuántos ciclos de reloj se necesitan para enviar un píxel.

Cuando el ciclo de reloj es 1, llamamos a esta interfaz RGB una interfaz paralela. En otros casos, es una interfaz en serie. El principio más general es que cualquier interfaz que requiera múltiples ciclos de reloj para enviar un píxel es en serie.

interfaz.

¿Cómo juzgar si se admite el ancho de bits de 24 bits? La forma más sencilla es contar el número de pines de datos en la tabla pinmux. Si hay 24 pines, admite 24 bits. Si solo hay 18 pines, admite 18 bits.

Conexión de hardware

Para interfaces RGB paralelas, cuando el ancho de bits es menor a 24, la conexión de hardware debe optar por conectar los bits altos en cada componente y abandonar los bits bajos, el motivo de esto es perder una menor cantidad de colores.

Para la interfaz RGB en serie, la conexión de hardware puede consultar las columnas de sincronización RGB en el diagrama de configuración de pines RGB e I8080.

La interfaz RGB tiene dos métodos de sincronización. Según la experiencia, intente utilizar el segundo método. Asegúrese de que el pin DE esté conectado al hardware.

- Sincronización H+Sincronización V

- DE (Habilitación de datos)

4.3.3 Ejemplo de configuración de interfaz RGB paralela

Cuando configuramos la interfaz RGB paralela, no es necesario distinguir entre 24 bits, 18 bits y 16 bits en la configuración. Para conocer el ancho máximo de bits, consulte la tabla de pin mux. Si la pantalla LCD admite un ancho de bits que es más ancho que el que admite el SoC

Si el ancho de la broca es pequeño, por supuesto sólo puedes elegir el más pequeño.

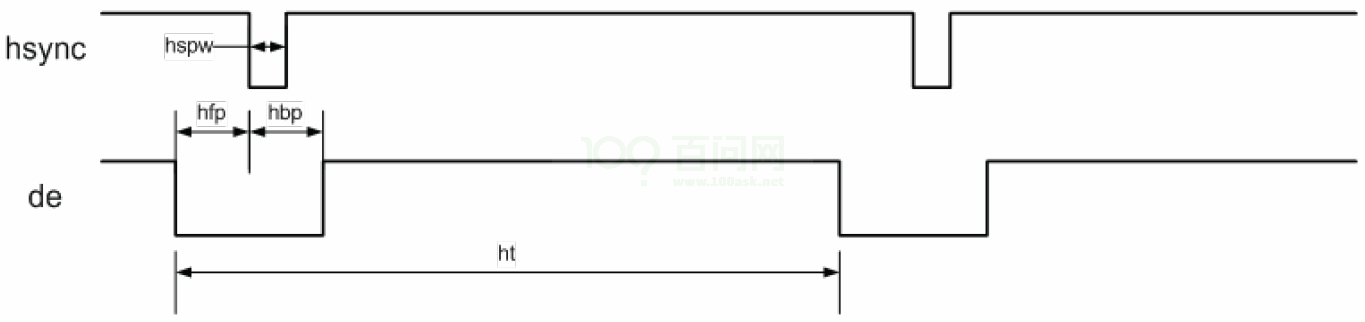

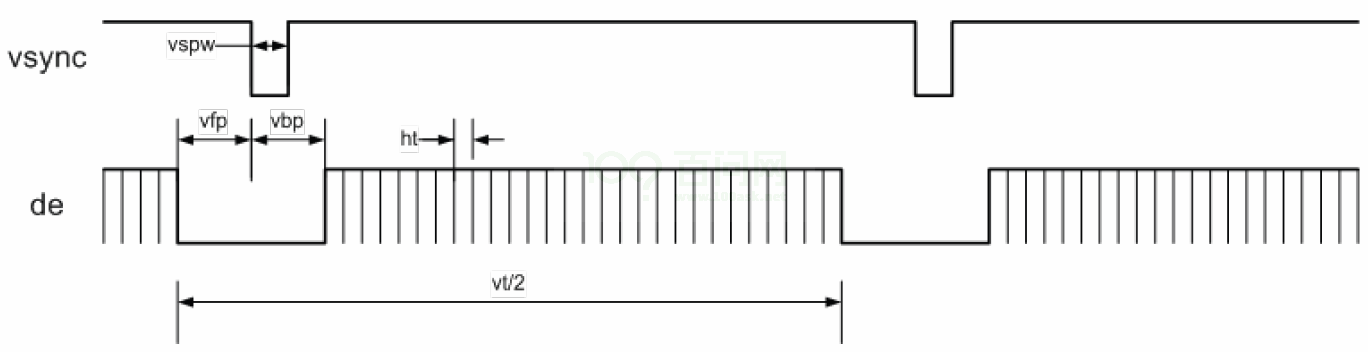

Debido a que no requiere inicialización, hay muy pocos problemas con la interfaz RGB. Concéntrese en la racionalidad de la sincronización de la pantalla LCD, es decir, la racionalidad de los atributos de lcd_ht, lcd_hspw, lcd_hbp, lcd_vt, lcd_vspw y lcd_vbp.

sexo.

El siguiente es un ejemplo típico de configuración de placa de interfaz RGB paralela.dts, en el que se utilizan líneas en blanco para dividir la configuración en varias partes.

- La primera parte determina si se usa la configuración y qué controlador de pantalla usar. lcd_driver_name determina qué controlador de pantalla usar para la inicialización. Aquí está default_lcd, que está configurado para configuraciones que no requieren inicialización.

pantalla rgb

-

La segunda parte determina si la siguiente configuración es una configuración RGB paralela.

-

La tercera parte determina el tiempo de transmisión del módulo LCD en el SoC. Verifique la descripción del parámetro de tiempo de pantalla.

-

La cuarta parte determina la luz de fondo (pwm y lcd_bl_en). Consulte los parámetros relacionados con la retroiluminación.

-

La quinta parte es la configuración de la parte del efecto de visualización. Si no es RGB de 24 bits, generalmente debe configurar lcd_frm.

-

La sexta parte es la fuente de alimentación y la configuración de pines. Se debe decidir si utilizar RGB666 o RGB888 en función de la tabla pinmux real. Si el chip solo tiene 18 datos rgb, solo puede ser rgb18. Consulte la fuente de alimentación y los pines.

parámetro.

&lcd0 {

/* part 1 */

lcd_used = <1>;

lcd_driver_name = "default_lcd";

/* part 2 */

lcd_if = <0>;

lcd_hv_if = <0>;

/* part 3 */

lcd_width = <150>;

lcd_height = <94>;

lcd_x = <800>;

lcd_y = <480>;

lcd_dclk_freq = <33>;

lcd_hbp = <46>;

lcd_ht = <1055>;

lcd_hspw = <0>;

lcd_vbp = <23>;

lcd_vt = <525>;

lcd_vspw = <0>;

/* part 4 */

lcd_backlight = <50>;

lcd_pwm_used = <1>;

lcd_pwm_ch = <8>;

lcd_pwm_freq = <10000>;

lcd_pwm_pol = <1>;

lcd_bl_en = <&pio PD 27 1 0 3 1>;

lcd_bright_curve_en = <0>;

/* part 5 */

lcd_frm = <0>;

lcd_io_phase = <0x0000>;

lcd_gamma_en = <0>;

lcd_cmap_en = <0>;

lcd_hv_clk_phase = <0>;

lcd_hv_sync_polarity= <0>;

/* part 6 */

lcd_power = "vcc-lcd";

lcd_pin_power = "vcc-pd";

pinctrl-0 = <&rgb24_pins_a>;

pinctrl-1 = <&rgb24_pins_b>;

};

4.3.4 Configuración típica de la interfaz RGB serie

El RGB serial es relativo al RGB paralelo. No significa que solo use una línea para enviar datos. Siempre que se puedan usar múltiples ciclos de reloj para enviar los datos de un píxel, entonces dicha interfaz RGB es RGB serial.

Al igual que la interfaz RGB paralela, la interfaz RGB serie específica no es necesaria y no se puede reflejar en la configuración, lo único que hay que hacer es conectar el hardware correctamente.

El siguiente es un ejemplo típico de configuración de una placa de interfaz RGB en serie.dts. Tiene solo 8 pines de datos. Se utilizan líneas en blanco para dividir la configuración en varias partes.

-

La primera parte determina si se usa la configuración y qué controlador de pantalla usar. lcd_driver_name determina qué controlador de pantalla usar para la inicialización.

-

La División 2 determina que la siguiente configuración es una configuración RGB en serie.

-

La tercera parte determina el tiempo de transmisión del módulo LCD en el SoC. Verifique la descripción del parámetro de tiempo de pantalla.

Consejos Lo que

hay que tener en cuenta aquí es que para esta interfaz, el SoC requiere un total de tres ciclos para enviar un píxel, por lo que cuando configuramos el tiempo, debemos cumplir con lcd_dclk_freq 3=lcd_ht lcd_vt 60 , o

lcd_dclk_freq=lcd_ht 3 lcd_vt 60 es 3 veces lcd_ht o 3 veces lcd_dclk_freq.

-

La cuarta parte determina la luz de fondo. Eso es pwm y lcd_bl_en. Consulte los parámetros relacionados con la retroiluminación.

-

La quinta parte es la configuración del efecto de visualización.

-

Parte 6: Definición de pines y fuentes de alimentación. Consulte la fuente de alimentación y los parámetros del pin.

ilustrar

El IC del controlador LCD en el siguiente ejemplo es stv7789v, que debe inicializarse. El protocolo de interfaz inicializado es SPI, por lo que hay varias configuraciones de pines SPI más. GPIO se usa en el controlador para simular el protocolo SPI, así que aquí están las configuraciones

función gpio.

&lcd0 {

/* part 1 */

lcd_used = <1>;

lcd_driver_name = "st7789v";

/* part 2 */

lcd_if = <0>;

lcd_hv_if = <8>;

/* part 3 */

lcd_x = <240>;

lcd_y = <320>;

lcd_width = <108>;

lcd_height = <64>;

lcd_dclk_freq = <19>;

lcd_hbp = <120>;

;10 + 20 + 10 + 240*3 = 760 real set 1000

lcd_ht = <850>;

lcd_hspw = <2>;

lcd_vbp = <13>;

lcd_vt = <373>;

lcd_vspw = <2>;

/* part 4 */

lcd_backlight = <50>;

lcd_pwm_used = <1>;

lcd_pwm_ch = <8>;

lcd_pwm_freq = <50000>;

lcd_pwm_pol = <1>;

lcd_pwm_max_limit = <255>;

lcd_bl_en = <&pio PB 1 1 0 3 1>;

lcd_bright_curve_en = <1>;

/* part 5 */

lcd_frm = <1>;

lcd_hv_clk_phase = <0>;

lcd_hv_sync_polarity= <0>;

lcd_hv_srgb_seq = <0>;

lcd_io_phase = <0x0000>;

lcd_gamma_en = <0>;

lcd_cmap_en = <0>;

lcd_rb_swap = <0>;

/* part 6 */

lcd_power = "vcc-lcd";

lcd_pin_power = "vcc-pd";

/*reset */

lcd_gpio_0 = <&pio PD 9 1 0 3 1>;

/* cs */

lcd_gpio_1 = <&pio PD 10 1 0 3 0>;

/*sda */

lcd_gpio_2 = <&pio PD 13 1 0 3 0>;

/*sck */

lcd_gpio_3 = <&pio PD 12 1 0 3 0>;

pinctrl-0 = <&rgb8_pins_a>;

pinctrl-1 = <&rgb8_pins_b>;

};

4.4 Interfaz MIPI-DSI

4.4.1 Descripción general

MIPI-DSI, interfaz serie de pantalla de interfaz de procesador de la industria móvil, es la interfaz serie de pantalla de interfaz de procesador de la industria móvil.

Los usuarios necesitan saber:

-

El modo de comando, similar a la interfaz MPU, requiere GRAM dentro del IC para el almacenamiento en búfer.

-

Modo de vídeo. Al igual que en la interfaz RGB, no hay GRAM, por lo que es necesario enviar datos constantemente al panel. El modo de vídeo se divide en tres submodos.

• Modo sin ráfagas con pulsos de sincronización

• Modo sin ráfagas con eventos de sincronización

• Modo de ráfaga. El entendimiento simple es que la relación de datos efectiva es mayor y la eficiencia de transmisión es mayor.

- carril significa un par de pasadores diferenciales.

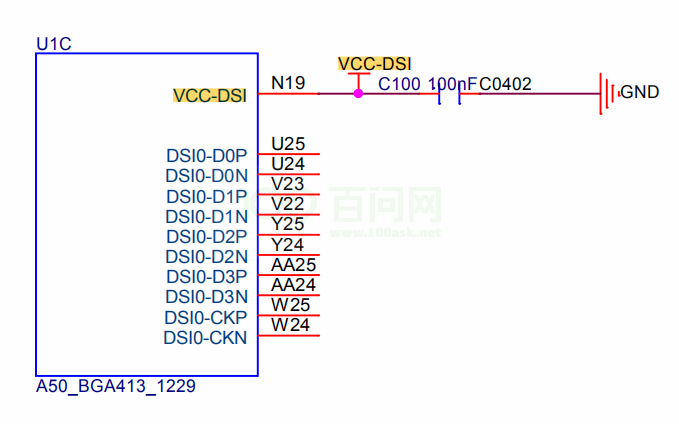

4.4.2 Pines MIPI-DSI

Los pines MIPI-DSI están dedicados en la mayoría de los circuitos integrados y no es necesario configurarlos en board.dtsi, siempre que el hardware esté conectado.

Sin embargo, los pines DSI de algunos IC no están dedicados y se reutilizan con pines de otras funciones. En este caso, es necesario configurar pinctrl-0 y pinctrl-1.

Los pines de mipi-dsi son diferenciales y se dividen en dos tipos de pines, uno es un pin de reloj y el otro es un pin de datos. El número de pines de datos es variable y la unidad de cantidad es el carril. Cada carril de pines en realidad contiene dos lineas.

En términos generales, la cantidad de carriles mencionada en el manual de la pantalla LCD se refiere a la cantidad de pines de datos, excluyendo los pines de reloj. Por ejemplo, una pantalla MIPI-DSI de 4 carriles tiene un total de (4+1)*2 pines.

4.4.3 Fuente de alimentación MIPI-DSI

Generalmente, hay una fuente de alimentación que suministra el módulo MIPI-DSI. Puede considerarlo como alimentación de pin o alimentación de módulo. Diferentes IC pueden tener diferentes requisitos de voltaje para esta fuente de alimentación. Una vez que se determina el modelo de IC, los requisitos de voltaje de este fuente de alimentación

Si el voltaje de este circuito se cambia sin autorización, el módulo puede volverse anormal.

4.4.4 Determinar si se admite una determinada pantalla MIPI-DSI

1. Limitación de resolución. Hay un límite de velocidad en el carril y podemos obtener el límite de resolución máximo. La fórmula de cálculo es la siguiente: siempre que lane_speed no exceda la velocidad especificada en la especificación IC anterior, es teóricamente compatible.

Por favor verifique las especificaciones del IC.

velocidad_carril=lcd_vt * lcd_ht * fps * bit_por_píxel / número_carril / 1e9

• Unidad: Gbps.

• fps: La frecuencia de actualización esperada, que se puede conocer en el manual de la pantalla, suele ser 60. Consulte lcd_dclk_freq.

• bit_per_pixel: el número de bits contenidos en cada píxel, normalmente 24 o 18, se establece mediante lcd_dsi_format.

• lane_num: Número de carril, establecido por lcd_dsi_lane.

• 1e9:1000000000 escrito en notación científica.

- Al elegir una resolución, debe considerar el ancho de banda del sistema y las capacidades DE. Por lo tanto, incluso si la interfaz admite esta resolución, es posible que no sea compatible con todo el sistema. Por ejemplo, el hardware elige una resolución de alta velocidad para ahorrar costos.

Obviamente, no es realista utilizar una memoria DDR muy lenta y al mismo tiempo querer elegir una pantalla de alta resolución.

- límite de número de carriles. La mayoría de los circuitos integrados Allwinner admiten hasta 4 carriles de MIPI-DSI. Si ve una pantalla con más de 4 carriles, definitivamente no lo admitirá. Algunos IC admiten hasta 8 carriles, por lo que debes elegir este modelo.

IC。

- El estándar MIPI-DSI no es compatible. Por favor verifique las especificaciones del IC.

4.4.5 Calcular la frecuencia del carril de reloj MIPI-DSI

Utilice un osciloscopio para medir la señal del reloj MIPI-DSI y determinar si su frecuencia satisface las necesidades de la pantalla.

Primero, podemos calcular la frecuencia de la señal CLK teórica a partir del reloj de píxeles y el número de carril dados, de la siguiente manera:

Freq_dsi_clk = (Dclk * colordepth * 3 / lane ) / 2

- Freq_dsi_clk: La frecuencia del pin del reloj dsi que queremos medir. La unidad es MHz.

- Dclk: reloj de píxeles. Calculado a partir de la fórmula lcd_ht lcd_vt fps/1e6.

- Profundidad de color: Profundidad de color, generalmente 8 o 6.

- Multiplicar por 3 significa que hay 3 componentes RGB.

- Carril: Número de carril de dsi.

- Dividido por 2: porque el reloj dsi se muestrea en ambos bordes.

4.4.6 Ejemplo de configuración de pantalla del modo Vídeo MIPI-DSI

La mayoría de las pantallas MIPI-DSI están configuradas en modo vídeo.

El siguiente es un ejemplo típico de configuración de board.dts para el modo de vídeo MIPI-DSI, en el que se utilizan líneas en blanco para dividir la configuración en varias partes.

- La primera parte determina si se usa la configuración y qué controlador de pantalla usar. lcd_driver_name determina qué controlador de pantalla usar para la inicialización.

- La segunda parte es determinar que la configuración es una interfaz dsi y que la interfaz dsi usa el modo de video.

- La tercera parte determina el tiempo de transmisión del módulo LCD en el SoC. Verifique la descripción del parámetro de tiempo de pantalla.

- La cuarta parte, configuraciones relacionadas con la luz de fondo. Consulte los parámetros relacionados con la retroiluminación.

- Parte 5, configuración detallada de la interfaz dsi.

- La sexta parte muestra la configuración relacionada con los efectos.

- Parte 7, configuración de pines y energía. Consulte la fuente de alimentación y los parámetros del pin.

&lcd0 {

/* part 1 */

lcd_used = <1>;

lcd_driver_name = "k101im2qa04";

/* part 2 */

lcd_if = <4>;

lcd_dsi_if = <0>;

/* part 3 */

lcd_x = <800>;

lcd_y = <1280>;

lcd_width = <135>;

lcd_height = <216>;

lcd_dclk_freq = <68>;

lcd_hbp = <36>;

lcd_ht = <854>;

lcd_hspw = <18>;

lcd_vbp = <12>;

lcd_vt = <1320>;

lcd_vspw = <4>;

/* part 4 */

lcd_backlight = <50>;

lcd_pwm_used = <1>;

lcd_pwm_ch = <0>;

lcd_pwm_freq = <50000>;

lcd_pwm_pol = <1>;

lcd_pwm_max_limit = <255>;

lcd_bl_en = <&pio PB 8 1 0 3 1>;

lcd_bright_curve_en = <0>;

/* part 5 */

lcd_dsi_lane = <4>;

lcd_dsi_format = <0>;

lcd_dsi_te = <0>;

/* part 6 */

lcd_frm = <0>;

lcd_gamma_en = <0>;

lcd_cmap_en = <0>;

/* part 7 */

lcd_pin_power = "dcdc1";

lcd_pin_power1 = "eldo3";

lcd_power = "dc1sw";

lcd_gpio_0 = <&pio PD 22 1 0 3 1>;

pinctrl-0 = <&dsi4lane_pins_a>;

pinctrl-1 = <&dsi4lane_pins_b>;

};

4.4.7 Ejemplo de configuración de pantalla de ultra alta resolución MIPI-DSI

Según el nivel de resolución, se suele dividir en varios modos de configuración. Resolución de 1080p e inferior: simplemente configure lcd_dsi_if para controlar. El modo comando es generalmente una pantalla de baja resolución, mientras que el modo video

Y el modo ráfaga es para alta resolución. Si la resolución alcanza los 2k, se requieren configuraciones adicionales.

Una pantalla con una resolución de 2k o superior en realidad requiere hasta 8 líneas de datos para mostrarse normalmente. Cuatro de las líneas envían píxeles impares en una imagen y la otra imagen envía píxeles impares.

ilustrar

Tenga en cuenta que solo algunos circuitos integrados admiten resolución ultraalta; consulte la parte MIPI-DSI de las especificaciones del chip para obtener más detalles.

El siguiente es un ejemplo de configuración de board.dts MIPI-DSI de alta y ultra alta resolución (superior a 2k), en el que se utilizan líneas en blanco para dividir la configuración en varias partes.

- La primera parte determina si se usa la configuración y qué controlador de pantalla usar. lcd_driver_name determina qué controlador de pantalla usar para la inicialización.

- La segunda parte es determinar que la configuración es una interfaz dsi y que la interfaz dsi usa el modo de video.

- La tercera parte determina el tiempo de transmisión del módulo LCD en el SoC. Verifique la descripción del parámetro de tiempo de pantalla.

- La cuarta parte, configuraciones relacionadas con la retroiluminación, consulte los parámetros relacionados con la retroiluminación.

- Parte 5, configuración detallada de la interfaz dsi.

Explique que

la razón por la que lcd_dsi_lane todavía está configurado en 4 carriles es porque esto es para establecer el número de carriles para un dsi, y esta pantalla requiere dos dsi. En total son 8 carriles.

En este momento, las tres opciones lcd_tcon_mode, lcd_dsi_port_num y lcd_tcon_en_odd_even_div deben configurarse especialmente. Haga clic para ver el significado específico. Si es una pantalla con una resolución de 1080p o menos (use solo

4lane o inferior), estas tres configuraciones se pueden establecer en 0 de forma predeterminada.

6. La sexta parte muestra los ajustes de la parte de efectos.

7. La séptima parte es la configuración de pines y fuente de alimentación. Configure según el diagrama del circuito. Consulte la fuente de alimentación y los parámetros del pin.

&lcd0 {

/* part 1 */

lcd_used = <1>;

lcd_driver_name = "lq101r1sx03";

/* part 2 */

lcd_if = <4>;

lcd_dsi_if = <0>;

/* part 3 */

lcd_x = <2560>;

lcd_y = <1600>;

lcd_width = <216>;

lcd_height = <135>;

lcd_dclk_freq = <268>;

lcd_hbp = <80>;

lcd_ht = <2720>;

lcd_hspw = <32>;

lcd_vbp = <37>;

lcd_vt = <1646>;

lcd_vspw = <6>;

/* part 4 */

lcd_backlight = <50>;

lcd_pwm_used = <1>;

lcd_pwm_ch = <0>;

lcd_pwm_freq = <50000>;

lcd_pwm_pol = <1>;

lcd_pwm_max_limit = <255>;

lcd_bl_en = <&pio PH 10 1 0 3 1>;

/* part 5 */

lcd_dsi_lane = <4>;

lcd_dsi_format = <0>;

lcd_dsi_te = <0>;

lcd_dsi_port_num = <1>;

lcd_tcon_mode = <4>;

lcd_tcon_en_odd_even_div = <1>;

/* part 6 */

lcd_frm = <0>;

lcd_io_phase = <0x0000>;

lcd_gamma_en = <0>;

lcd_bright_curve_en = <0>;

lcd_cmap_en = <0>;

/* part 7 */

lcd_power = "vcc18-lcd";

lcd_power1 = "vcc33-lcd";

lcd_pin_power = "vcc-pd";

lcd_gpio_0 = <&pio PH 11 1 0 3 1>;

lcd_gpio_1 = <&pio PH 12 1 0 3 1>;

};

4.4.8 Ejemplo de configuración de pantalla del modo Comando MIPI-DSI

La pantalla DSI en modo Comando es similar a la interfaz I8080. La pantalla tiene RAM en su interior para almacenamiento en búfer y procesamiento de imágenes. En este caso, generalmente es necesario usar el pin te de la pantalla para activar la interrupción vsync, por lo que es diferente. de otros tipos de DSI.

La diferencia con la pantalla es que el pin lcd_vsync debe configurarse aquí. El pin te de la pantalla está conectado a lcd_vsync y lcd_dsi_te está configurado en 1.

La configuración del pin te es muy crítica. En términos generales, si la pantalla tiene un pin te, debe estar conectado. De lo contrario, la pantalla se romperá al mostrar imágenes dinámicas y el software no podrá resolverlo, lo que resulta directamente en la el hardware final no se puede producir en masa.

fruta.

Aquí solo enumeramos las diferencias clave con el modo de vídeo MIPI-DSI. Para obtener más información, consulte la sección anterior.

- La primera parte determina si se usa la configuración y qué controlador de pantalla usar. lcd_driver_name determina qué controlador de pantalla usar para la inicialización.

- La segunda parte determina que la configuración es una interfaz dsi y lcd_dsi_if se establece en 1 para indicar el modo de comando.

- La tercera parte determina el tiempo de transmisión del módulo LCD en el SoC. Verifique la descripción del parámetro de tiempo de pantalla.

- La cuarta parte, configuraciones relacionadas con la luz de fondo. Consulte los parámetros relacionados con la retroiluminación.

- Parte 5, configuración detallada de la interfaz dsi. lcd_dsi_te, configurarlo en 1 aquí significa habilitar el disparador.

- La sexta parte muestra la configuración relacionada con los efectos.

- Parte 7, configuración de pines y energía. lcd_vsync, aquí está el pin te. En el hardware, este pin debe estar conectado al pin te de la pantalla. En el software, debe configurarse en la función vsync. Consulte la fuente de alimentación y los parámetros del pin.

&lcd0 {

/* part 1 */

lcd_used = <1>;

lcd_driver_name = "h245qbn02";

/* part 2 */

lcd_if = <4>;

lcd_dsi_if = <1>;

/* part 3 */

lcd_x = <240>;

lcd_y = <432>;

lcd_width = <52>;

lcd_height = <52>;

lcd_dclk_freq = <18>;

lcd_hbp = <96>;

lcd_ht = <480>;

lcd_hspw = <2>;

lcd_vbp = <21>;

lcd_vt = <514>;

lcd_vspw = <2>;

/* part 4 */

lcd_backlight = <100>;

lcd_pwm_used = <1>;

lcd_pwm_ch = <0>;

lcd_pwm_freq = <50000>;

lcd_pwm_pol = <1>;

lcd_pwm_max_limit = <255>;

lcd_bright_curve_en = <0>;

lcd_bl_en = <&pio PB 3 1 0 3 1>;

/* part 5 */

lcd_dsi_lane = <1>;

lcd_dsi_format = <0>;

lcd_dsi_te = <1>;

lcd_frm = <0>;

lcd_io_phase = <0x0000>;

lcd_gamma_en = <0>;

lcd_cmap_en = <0>;

/* part 7 */

lcd_power = "axp233_dc1sw"

lcd_power1 = "axp233_eldo1"

lcd_gpio_0 = <&pio PB 2 1 0 3 0>;

lcd_vsync = <&pio PD 21 2 0 3 0>;

};

4.4.9 Ejemplo de configuración de pantalla dual MIPI-DSI VR

La escena real son dos pantallas físicas, cada pantalla es de 1080p y cada pantalla tiene 4 carriles. Se requiere que cada una de las dos pantallas muestre la mitad izquierda y derecha de un cuadro de imagen. Debido a la relación de aspecto, las pantallas horizontales y verticales y capacidades de procesamiento DE, factor,

Un DE+ un tcon+ dos DSI ya no es suficiente, se deben usar dos tcon para controlar un dsi cada uno, sin embargo, las dos pantallas deben estar sincronizadas, lo que requiere el uso del modo de sincronización de los dos tcon.

-

LCD0 está marcado como tcon esclavo, que es controlado por el tcon maestro (lcd_tcon_mode está configurado).

-

LCD1 está marcado como master tcon y es responsable de todos los interruptores de alimentación, retroiluminación y pines de las dos pantallas.

-

Encienda los pines, la fuente de alimentación, etc. en LCD1. Primero se enciende LCD0 y se inicializan los registros del módulo correspondiente, pero la fuente de alimentación no se enciende. Luego, encienda LCD1. Cuando LCD1 esté habilitado, LCD0 se encenderá. activado para enviar datos juntos. Haz esto al mismo tiempo

Encendido y apagado.

ilustrar

Nota: solo unos pocos circuitos integrados admiten este modo

&lcd0 {

lcd_used = <1>;

lcd_driver_name = "lpm025m475a";

;lcd_bl_0_percent = <0>;

;lcd_bl_40_percent = <23>;

;lcd_bl_100_percent = <100>;

lcd_backlight = <50>;

lcd_if = <4>;

lcd_x = <1080>;

lcd_y = <1920>;

lcd_width = <31>;

lcd_height = <56>;

lcd_dclk_freq = <141>;

lcd_pwm_used = <0>;

lcd_pwm_ch = <0>;

lcd_pwm_freq = <20000>;

lcd_pwm_pol = <0>;

lcd_pwm_max_limit = <255>;

lcd_hbp = <100>;

lcd_ht = <1212>;

lcd_hspw = <5>;

lcd_vbp = <8>;

lcd_vt = <1936>;

lcd_vspw = <2>;

lcd_dsi_if = <0>;

lcd_dsi_lane = <4>;

lcd_dsi_format = <0>;

lcd_dsi_te = <0>;

lcd_dsi_eotp = <0>;

lcd_frm = <0>;

lcd_io_phase = <0x0000>;

lcd_hv_clk_phase = <0>;

lcd_hv_sync_polarity= <0>;

lcd_gamma_en = <0>;

lcd_bright_curve_en = <0>;

lcd_cmap_en = <0>;

lcd_dsi_port_num = <0>;

lcd_tcon_mode = <3>;

lcd_slave_stop_pos = <0>;

lcd_sync_pixel_num = <0>;

lcd_sync_line_num = <0>;

};

&lcd1 {

lcd_used = <1>;

lcd_driver_name = "lpm025m475a";

;lcd_bl_0_percent = <0>;

;lcd_bl_40_percent = <23>;

;lcd_bl_100_percent = <100>;

lcd_backlight = <50>;

lcd_if = <4>;

lcd_x = <1080>;

lcd_y = <1920>;

lcd_width = <31>;

lcd_height = <56>;

lcd_dclk_freq = <141>;

lcd_pwm_used = <1>;

lcd_pwm_ch = <0>;

lcd_pwm_freq = <20000>;

lcd_pwm_pol = <0>;

lcd_pwm_max_limit = <255>;

lcd_hbp = <100>;

lcd_ht = <1212>;

lcd_hspw = <5>;

lcd_vbp = <8>;

lcd_vt = <1936>;

lcd_vspw = <2>;

lcd_dsi_if = <0>;

lcd_dsi_lane = <4>;

lcd_dsi_format = <0>;

lcd_dsi_te = <0>;

lcd_dsi_eotp = <0>;

lcd_frm = <0>;

lcd_io_phase = <0x0000>;

lcd_hv_clk_phase = <0>;

lcd_hv_sync_polarity= <0>;

lcd_gamma_en = <0>;

lcd_bright_curve_en = <0>;

lcd_cmap_en = <0>;

lcd_dsi_port_num = <0>;

lcd_tcon_mode = <1>;

lcd_tcon_slave_num = <0>;

lcd_slave_stop_pos = <0>;

lcd_sync_pixel_num = <0>;

lcd_sync_line_num = <0>;

lcd_bl_en = <&pio PH 10 1 0 3 1>;

lcd_power = "vcc-dsi";

lcd_power1 = "vcc18-lcd";

lcd_power2 = "vcc33-lcd";

lcd_gpio_0 = <&pio PH 8 1 0 3 1>;

lcd_gpio_1 = <&pio PH 11 1 0 3 1>;

lcd_gpio_2 = <&pio PH 12 1 0 3 1>;

lcd_pin_power = "vcc-ph"

};

4.5 Interfaz I8080

4.5.1 Descripción general

La interfaz de pantalla Intel 8080 (también conocida como interfaz MCU) es un protocolo muy antiguo y generalmente se utiliza en pantallas con resoluciones muy pequeñas.

Línea de señal:

• Señal de selección de chip CS, determina si el chip funciona.

• Señal de selección de registro RS, bajo significa seleccionar índice o registro de estado, alto significa seleccionar registro de control. En escenarios reales, generalmente está conectado al pin LCD_DE (pin de habilitación de datos) del SoC.

• /WR (bajo significa escribir datos) señal de distinción del comando de datos, que es la señal de reloj de escritura, generalmente conectada al pin LCD_CLK del SoC.

• La señal de lectura de datos /RD (bajo significa leer datos), que es la señal de reloj de lectura, generalmente está conectada al pin LCD_HSYNC del SoC.

• RESET Restablece la pantalla LCD (use el comando fijo serie 0 1 0 para restablecer).

• Datos Bus de datos para transmisión bidireccional.

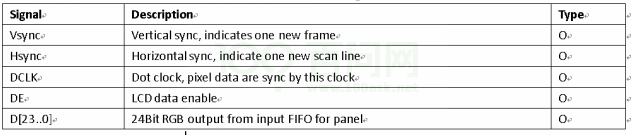

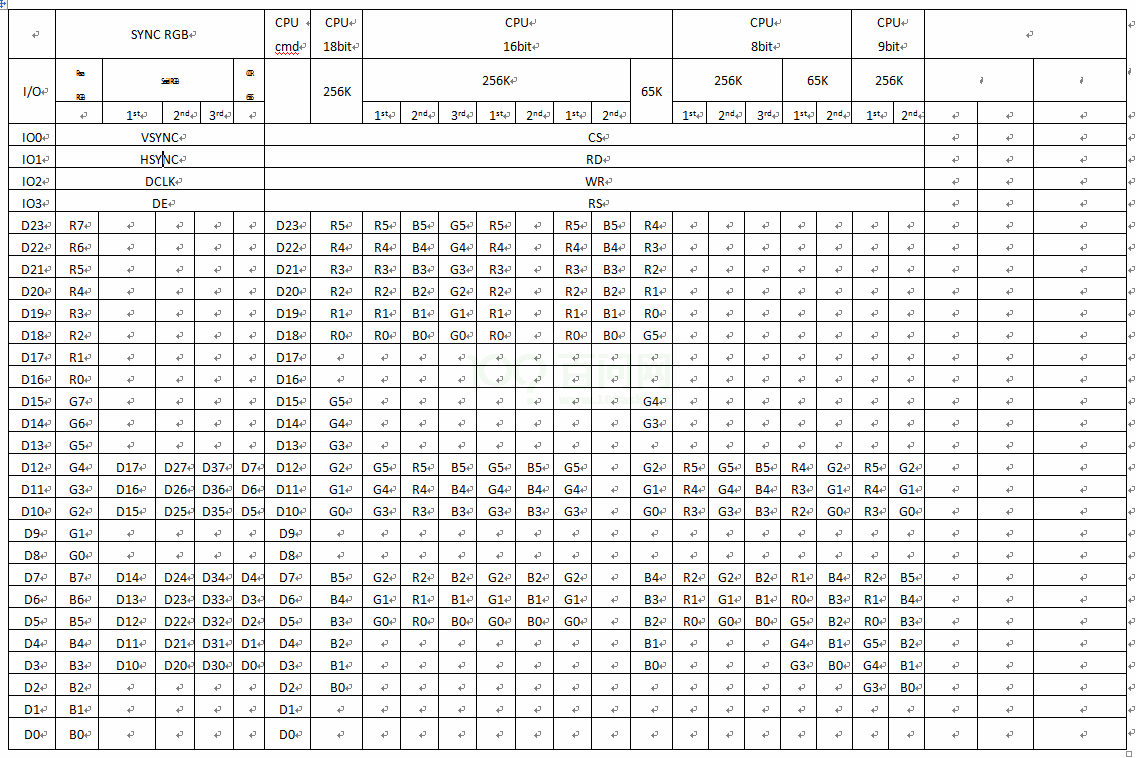

Las interfaces de ancho de bits de datos basadas en I8080 son 8/9/16/18. ¿Qué pines están conectados a la referencia? Incluso si el ancho de bits es el mismo, los pines conectados son diferentes. Otro factor a considerar es el formato RGB.

-

RGB565, hay un total de 65K colores.

-

RGB666, un total de 262K colores.

-

9 bits está fijado en 262K.

Aprenda del manual de la pantalla: ancho de bits de datos, suma del número de colores, consulte el diagrama de configuración de pines RGB e I8080 para la conexión del hardware.

4.5.2 Ejemplo de configuración típica de la pantalla de interfaz I8080

下面是典型是一个RGB565 的,位宽为8 位的I8080 接口的屏的board.dts 配置示例

1.第一部分,决定该配置是否使用,以及使用哪个屏驱动,lcd_driver_name 决定了用哪个屏驱动来初始化。

2.第二部分,决定该配置是I8080 接口,而且是8bit/2cycle 格式RGB565。

技巧

为什么叫做8bit/2cycle RGB565 呢,首先它的格式是RGB565,也就是一个像素是16bit,然后它是8bit 的位宽,就需要两个时钟周期才能发完一个像素,所以才

叫2 cycle。

-

第三部分,决定了SoC 中的LCD 模块发送时序,请查看屏时序参数说明。这里比较特殊的是设置像素时钟要满足以下公式:lcd_dclk_freq2>=lcd_htlcd_vtfps,或者lcd_dclk_freq=lcd_ht

2lcd_vt60, 也就是要么双倍lcd_ht要么双倍lcd_dclk_freq。 -

第四部分,背光相关的设置。请看背光相关参数。

-

第五部分,cpu 接口的详细设置。这里使能了lcd_cpu_te和lcd_cpu_mode,意思是使用te触发和规定了触发间隔。这是非常关键的设置。

-

第六部分,显示效果相关的设置。这里使能了lcd_frm也是比较关键的设置,详细意思点击查看。

-

第七部分,管脚和电源设置。这里为了用te 触发,同样需要设置lcd_vsync,该脚功能定义已经包括在pinctrl-0 中。这里自定义了一组管脚。参考RGB 和

I8080 管脚配置示意图,通过确定I8080 的位宽,像素格式(颜色数量),在表中确定需要连接哪些管脚。请看电源和管脚参数。

&pio {

I8080_8bit_pins_a: I8080_8bit@0 {

allwinner,pins = "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD8", "PD18", "

PD19", "PD20", "PD21";

allwinner,pname = "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD8", "PD18", "

PD19", "PD20", "PD21";

allwinner,function = "I8080_8bit";

allwinner,muxsel = <2>;

allwinner,drive = <3>;

allwinner,pull = <0>;

};

I8080_8bit_pins_b: I8080_8bit@1 {

allwinner,pins = "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD8", "PD18", "

PD19", "PD20", "PD21";

allwinner,pname = "PD1", "PD2", "PD3", "PD4", "PD5", "PD6", "PD7", "PD8", "PD18", "

PD19", "PD20", "PD21";

allwinner,function = "I8080_8bit_suspend";

allwinner,muxsel = <7>;

allwinner,drive = <3>;

allwinner,pull = <0>;

};

};

&lcd0 {

/* part 1 */

lcd_used = <1>;

lcd_driver_name = "s2003t46g";

/* part 2 */

lcd_if = <1>;

lcd_cpu_if = <14>;

/* part 3 */

lcd_x = <240>;

lcd_y = <320>;

lcd_width = <108>;

lcd_height = <64>;

lcd_dclk_freq = <16>;

lcd_hbp = <20>;

lcd_ht = <298>;

lcd_hspw = <10>;

lcd_vbp = <8>;

lcd_vt = <336>;

lcd_vspw = <4>;

/* part 4 */

lcd_pwm_used = <1>;

lcd_pwm_ch = <8>;

lcd_pwm_freq = <50000>;

lcd_pwm_pol = <1>;

lcd_pwm_max_limit = <255>;

lcd_bright_curve_en = <1>;

/* part 5 */

lcd_cpu_mode = <1>;

lcd_cpu_te = <1>;

/* part 6 */

lcd_frm = <1>;

lcd_gamma_en = <0>;

lcd_cmap_en = <0>;

lcd_rb_swap = <0>;

/* part 7 */

lcd_power = "vcc-lcd";

lcd_pin_power = "vcc-pd";

;reset pin

lcd_gpio_0 = <&pio PD 9 1 0 3 1>;

;cs pin

lcd_gpio_1 = <&pio PD 10 1 0 3 0>;

pinctrl-0 = <&I8080_8bit_pins_a>;

pinctrl-1 = <&I8080_8bit_pins_a>;

};

4.6 LVDS 接口

4.6.1 概述

LVDS significa Señalización diferencial de bajo voltaje, que es una interfaz de señal diferencial de bajo voltaje.

4.6.2 Configuración típica de enlace único LVDS

Para la interfaz LVDS, los pines lvds correspondientes a lcd0 y los pines lvds correspondientes a lcd1 son fijos y diferentes.

Dado que el protocolo lvds no tiene la capacidad de transmitir datos, generalmente el lado de la pantalla no necesita ninguna inicialización, solo es necesario inicializar el lado SoC. Entonces, el nombre del controlador lcd aquí sigue siendo "lcd predeterminado", por supuesto que puedes

Se realiza una optimización especial para el retraso del inicio de la inicialización.

El siguiente es un ejemplo típico de configuración de board.dts para una pantalla lvds de enlace único, en el que se utilizan líneas en blanco para dividir la configuración en varias partes.

-

La primera parte determina si se usa la configuración y qué controlador de pantalla usar. lcd_driver_name determina qué

controlador de pantalla usar para la inicialización. -

La segunda parte es decidir si la configuración es una interfaz lvds y un enlace único.

Consejos

Si es una pantalla Dual Link, además de cambiar lcd_lvds_if a 1, también se deben mover los pines de lcd1 hacia abajo, es decir, se deben configurar un total de PD0 a PD9 y PD10 a

Un total de veinte pines de PD19 son funciones de pines lvds (función 3). Por supuesto, el tiempo de la pantalla también debe cambiarse según la pantalla.

-

La tercera parte determina el tiempo de transmisión del módulo LCD en el SoC. Verifique la descripción del parámetro de tiempo de pantalla.

-

La cuarta parte, configuraciones relacionadas con la luz de fondo. Consulte los parámetros relacionados con la retroiluminación.

-

Parte 5, configuración detallada de la interfaz lvds.

-

La sexta parte muestra la configuración relacionada con los efectos.

-

Parte 7, configuración de pines y energía. Consulte la fuente de alimentación y los parámetros del pin.

&lcd0 {

/* part 1 */

lcd_used = 1

lcd_driver_name = "default_lcd";

/* part 2 */

lcd_if = 3

lcd_lvds_if = 0

/* part 3 */

lcd_x = 1280

lcd_y = 800

lcd_width = 150

lcd_height = 94

lcd_dclk_freq = 70

lcd_hbp = 20

lcd_ht = 1418

lcd_hspw = 10

lcd_vbp = 10

lcd_vt = 814

lcd_vspw = 5

/* part 4 */

lcd_pwm_used = 1

lcd_pwm_ch = 0

lcd_pwm_freq = 50000

lcd_pwm_pol = 0

lcd_pwm_max_limit = 255

lcd_backlight = 50

lcd_bright_curve_en = 0

lcd_bl_en = <&pio PD 21 1 0 3 1>;

/* part 5 */

lcd_lvds_colordepth = 1

lcd_lvds_mode = 0

/* part 6 */

lcd_frm = 1

lcd_hv_clk_phase = 0

lcd_hv_sync_polarity= 0

lcd_gamma_en = 0

lcd_cmap_en = 0

/* part 7 */

lcd_power = "vcc-lcd"

pinctrl-0 = <&lvds0_pins_a>;

pinctrl-1 = <&lvds0_pins_b>;

};

4.6.3 Configuración típica de doble enlace LVDS

Si la pantalla Dual Link:

- lcd_lvds_if se establece en 1 (escenario 1) o 2 (escenario 2).

- En términos de configuración de pines, también cambió de 4 carriles de datos a 8 carriles de datos, incluidos un total de 20 pines en el carril clk.

Escenario 1, conectando físicamente una pantalla con 8 líneas de datos, el SoC transmite la mitad de los píxeles, píxeles impares o píxeles pares a cada 4 líneas.

&lcd1 {

lcd_used = <1>;

lcd_driver_name = "bp101wx1";

lcd_backlight = <50>;

lcd_if = <3>;

lcd_x = <2560>;

lcd_y = <800>;

lcd_width = <150>;

lcd_height = <94>;

lcd_dclk_freq = <138>;

lcd_pwm_used = <0>;

lcd_pwm_ch = <2>;

lcd_pwm_freq = <50000>;

lcd_pwm_pol = <1>;

lcd_pwm_max_limit = <255>;

lcd_hbp = <40>;

lcd_ht = <2836>;

lcd_hspw = <20>;

lcd_vbp = <10>;

lcd_vt = <814>;

lcd_vspw = <5>;

lcd_lvds_if = <1>;

lcd_lvds_colordepth = <0>;

lcd_lvds_mode = <0>;

lcd_frm = <0>;

lcd_hv_clk_phase = <0>;

lcd_hv_sync_polarity= <0>;

lcd_gamma_en = <0>;

lcd_bright_curve_en = <0>;

lcd_cmap_en = <0>;

lcd_fsync_en = <0>;

lcd_fsync_act_time = <1000>;

lcd_fsync_dis_time = <1000>;

lcd_fsync_pol = <0>;

deu_mode = <0>;

lcdgamma4iep = <22>;

smart_color = <90>;

lcd_bl_en = <&pio PJ 27 1 0 3 1>;

lcd_gpio_0 = <&pio PI 1 1 0 3 1>;

lcd_pin_power = "bldo5";

lcd_power = "dc1sw";

pinctrl-0 = <&lcd1_lvds2link_pins_a>;

pinctrl-1 = <&lcd1_lvds2link_pins_b>;

};

Escenario 2 (compatible con algunos IC). Dos pantallas están conectadas físicamente. Cada pantalla tiene 4 carriles. Las dos pantallas son del mismo modelo, con la misma resolución y temporización. En este momento, algunos IC admiten el envío de todos los píxeles a cada pantalla. ,lograr

Pantalla dual (visualización dual en la señal), tenga en cuenta que en este momento, la sincronización de la pantalla LCD es la sincronización de una pantalla y lcd_lvds_if es 2.

lcd1: lcd1@01c0c001 {

lcd_used = <1>;

lcd_driver_name = "bp101wx1";

lcd_backlight = <50>;

lcd_if = <3>;

lcd_x = <1280>;

lcd_y = <800>;

lcd_width = <150>;

lcd_height = <94>;

lcd_dclk_freq = <70>;

lcd_pwm_used = <0>;

lcd_pwm_ch = <2>;

lcd_pwm_freq = <50000>;

lcd_pwm_pol = <1>;

lcd_pwm_max_limit = <255>;

lcd_hbp = <20>;

lcd_ht = <1418>;

lcd_hspw = <10>;

lcd_vbp = <10>;

lcd_vt = <814>;

lcd_vspw = <5>;

lcd_lvds_if = <2>;

lcd_lvds_colordepth = <0>;

lcd_lvds_mode = <0>;

lcd_frm = <0>;

lcd_hv_clk_phase = <0>;

lcd_hv_sync_polarity= <0>;

lcd_gamma_en = <0>;

lcd_bright_curve_en = <0>;

lcd_cmap_en = <0>;

lcd_fsync_en = <0>;

lcd_fsync_act_time = <1000>;

lcd_fsync_dis_time = <1000>;

lcd_fsync_pol = <0>;

deu_mode = <0>;

lcdgamma4iep = <22>;

smart_color = <90>;

lcd_bl_en = <&pio PJ 27 1 0 3 1>;

lcd_gpio_0 = <&pio PI 1 1 0 3 1>;

lcd_pin_power = "bldo5";

lcd_power = "dc1sw";

pinctrl-0 = <&lcd1_lvds2link_pins_a>;

pinctrl-1 = <&lcd1_lvds2link_pins_a>;

};

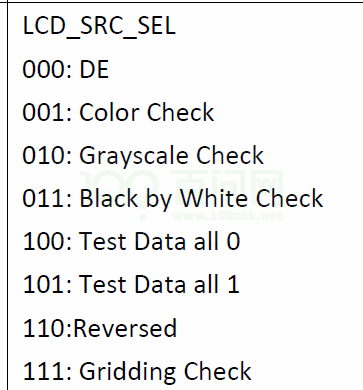

4.7 Diagrama de configuración de pines RGB e I8080

4.8 Notas sobre la migración de sys_config.fex a board.dtsi

Por estandarización y otras razones, algunas plataformas implementan la configuración en board.dtsi. A continuación se describen las precauciones para modificar board.dtsi.

4.8.1 Definición de pines

Al configurar una pantalla RGB o LVDS, no hay necesidad de definiciones complejas, no es necesario saber qué pines deben configurarse y no es necesario el nodo lcd0_suspend. donde está el nombre rgb24_pins_a

Una vez definido, puede usarlo directamente. Generalmente, las configuraciones disponibles directamente para las pantallas LCD se indicarán en los comentarios. Puede usar platform-pinctrl en el directorio del kernel arch/arm/boot/dts o arch/arm64/boot/ dts.dtsi texto

Encuéntrelo en el archivo.

ejemplo:

pinctrl-0 = <&rgb24_pins_a>;

pinctrl-1 = <&rgb24_pins_b>;//休眠时候的定义,io_disable

Por supuesto, también puedes personalizar un par de pies y escribirlos en board.dtsi, siempre y cuando el nombre no repita el nombre existente.

En aras de la estandarización, mantendremos nombres consistentes en todas las plataformas, donde el sufijo a significa que el pin está habilitado y b significa que io_disable se usa cuando el dispositivo está apagado.

Las siguientes definiciones de pines están disponibles actualmente:

| Nombre del pin | describir |

|---|---|

| rgb24_pins_a y rgb24_pins_b | Interfaz de pantalla RGB y el ancho de bits de datos es 24, RGB888 |

| rgb18_pins_a y rgb18_pins_b | Interfaz de pantalla RGB y el ancho de bits de datos es 16, RGB666 |

| lvds0_pins_a y lvds0_pins_b | Interfaz LVDS de enlace único Definición de 0 pines (pantalla principal lcd0) |

| lvds1_pins_a y lvds1_pins_b | Interfaz LVDS de enlace único Definición de 1 pin (pantalla principal lcd0) |

| lvds2link_pins_a y lvds2link_pins_b | Definición de pin de interfaz LVDS de doble enlace (pantalla principal lcd0) |

| lvds2_pins_a y lvds2_pins_b | Interfaz LVDS de enlace único Definición de 0 pines (pantalla principal lcd1) |

| lvds3_pins_a y lvds3_pins_b | Interfaz LVDS de enlace único Definición de 1 pin (pantalla principal lcd1) |

| lcd1_lvds2link_pins_a y lcd1_lvds2link_pins_b | Definición de pin de interfaz LVDS de doble enlace (pantalla principal LCD1) |

| dsi4lane_pins_a y dsi4lane_pins_b | Definición de pin de interfaz de pantalla DSI, 4 carriles, si es otro número de carril, solo |

4.8.2 Definición de fuente de alimentación

No es necesario prestar atención a la definición de la fuente de alimentación en el SDK anterior. Puede asignar directamente la cadena de alias de axp a un atributo como lcd_power. Sin embargo, en el nuevo SDK, si necesita utilizar una determinada fuente de alimentación, debe debe primero

Se define en el nodo disp y la cadena utilizada en la parte lcd debe ser coherente con la definida en disp. Por ejemplo, el siguiente ejemplo:

disp: disp@01000000 {

disp_init_enable = <1>;

disp_mode = <0>;

/* VCC-LCD */

dc1sw-supply = <®_sw>;

/* VCC-LVDS and VCC-HDMI */

bldo1-supply = <®_bldo1>;

/* VCC-TV */

cldo4-supply = <®_cldo4>;

};

Entre ellos, "-supply" es fijo y la cadena anterior es arbitraria, pero se recomienda elegir un nombre significativo. Los siguientes como <®_sw> deben encontrarse en el nodo regulator0 de board.dtsi.

Luego, en el nodo lcd0, si desea utilizar reg_sw, simplemente escríbalo de la siguiente manera: dc1sw corresponde a dc1sw-supply.

lcd_power=”dc1sw”

Dado que también hay un controlador axp y un controlador de pantalla en u-boot, leen la misma configuración que el kernel. Para que sean compatibles entre sí, existen las siguientes restricciones al nombrar.

En u-boot 2018, el controlador axp solo reconoce nombres definidos en el chip axp como bldo1, por lo que al nombrar xxxsupply, es mejor nombrarlo de acuerdo con la definición del chip axp.

4.8.3 Otras precauciones

board.dtsi puede contener solo lcd0 pero no lcd1, o solo tv0 pero no tv1. Si desea agregarlo en este momento, debe consultar la plataforma correspondiente en el directorio del kernel arch/arm/boot/dts o arch/ arm64/boot/dts.

Archivo .dtsi. Lo más crítico es que la cadena de direcciones después de @ debe ser coherente con la definición en el kernel, por ejemplo:

lcd1: lcd1@01c0c000

5 Descripción de los parámetros de hardware

5.1 Descripción de los parámetros de la interfaz LCD

5.1.1 nombre_controlador_LCD

El nombre del controlador de la pantalla LCD (cadena) debe corresponder al nombre del controlador de la pantalla.

5.1.2 nombre_modelo_lcd

El nombre del modelo de pantalla LCD, opcional, se puede utilizar en el mismo controlador de pantalla para distinguir aún más diferentes pantallas.

5.1.3 lcd_si

Interfaz LCD

El significado correspondiente de establecer el valor correspondiente es:

0:HV RGB接口

1:CPU/I80接口

2:Reserved

3:LVDS接口

4:DSI接口

5.1.4 lcd_hv_if

Interfaz del panel LCD HV

Este parámetro solo es válido cuando lcd_if=0. Defina varios tipos de interfaz en la pantalla de sincronización RGB.

El significado correspondiente de establecer el valor correspondiente es:

0:Parallel RGB

8:Serial RGB

10:Dummy RGB

11:RGB Dummy

12:Serial YUV (CCIR656)

5.1.5 lcd_hv_clk_fase

Panel LCD HV Fase del reloj