Tabla de contenido

02. ETH introducción de STM32F207

3.1. Interfaz de gestión de la estación: SMI

3.3, operación de escritura SMI

01. Introducción a Ethernet

Los periféricos Ethernet de STM32F20X y STM32F21 pueden aceptar y enviar datos de acuerdo con el estándar IEE802.3-2002.

Ethernet proporciona un periférico completo y flexible para cumplir con diferentes aplicaciones y requisitos. Admite dos interfaces industriales estándar conectadas al exterior (PHY): la interfaz independiente de medios (MII) definida en la especificación IEEE802.3 y la interfaz independiente de calidad fina (RMII) se utilizan de forma predeterminada. Se puede utilizar para una gran cantidad de requisitos, como conmutadores (conmutadores), tarjetas de interfaz de red, etc.

Ethernet cumple con los siguientes estándares:

● IEEE 802.3-2002, utilizado para Ethernet MAC.

● El estándar IEEE 1588-2008 se utiliza para especificar la precisión de la sincronización del reloj de la red.

● AMBA 2.0, utilizado para puertos maestro / esclavo AHB.

● La especificación RMII de RMII Alliance.

El clúster de protocolos TCP / IP de Ethernet también se ha explicado anteriormente.

" Arquitectura de paquetes Ethernet "

" 5000 palabras" hígado "este protocolo IP "

" 10 mil palabras y 30 imágenes para explicar el protocolo TCP "

" Explicación detallada del protocolo UDP "

02. ETH introducción de STM32F207

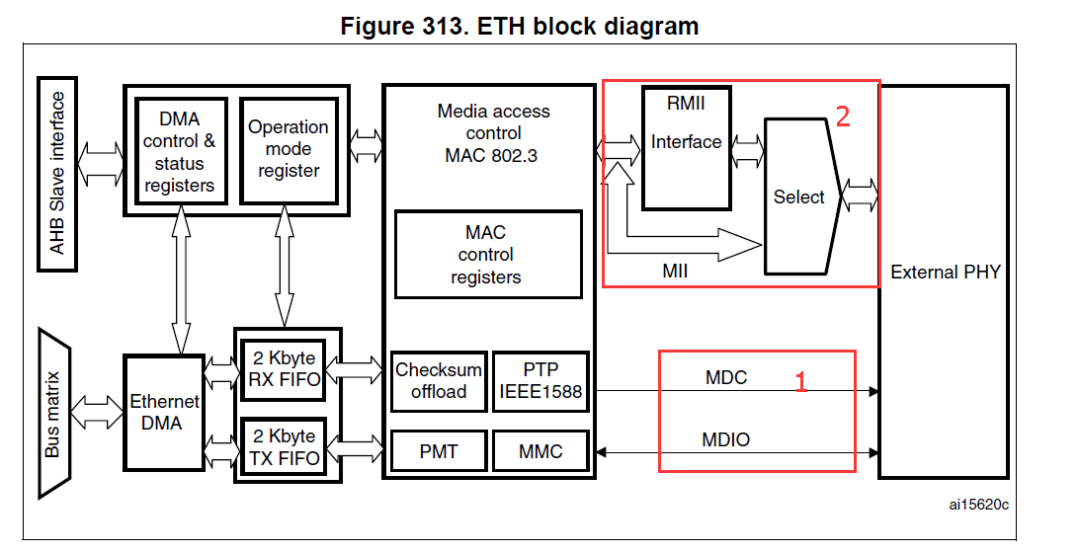

STM32F207 admite la interfaz MII y la interfaz RMII. Los periféricos Ethernet STM32F207 incluyen un MAC802.3 (Control de acceso a medios) y un controlador DMA. Admite interfaces MII y RMII de forma predeterminada y se conmuta mediante un bit de selección (consulte el registro SYSCFG_PMC).

El controlador DMA está conectado a la memoria a través de la interfaz maestro-esclavo AHB y el kernel. La interfaz maestra AHB controla la transmisión de datos y la interfaz esclava AHB se utiliza para acceder al espacio de registro de control y estado (CSR).

Antes de que el núcleo MAC envíe los datos, los datos se envían al búfer en el FIFO por DMA. De manera similar, el FIFO de recepción almacena las tramas de datos Ethernet recibidas a través de la línea hasta que estas tramas de datos se transfieren a la memoria del sistema a través de DMA.

El periférico Ethernet también incluye un SMI para la comunicación con un PHY externo. Mediante la configuración de un conjunto de registros, el usuario puede seleccionar diferentes modos y funciones de los controladores MAC y DMA.

Cuando se usa Ethernet, el reloj AHB debe ser de al menos 25 MHZ.

A continuación se muestra el diagrama de bloques de ETH

Acerca de la información de conexión de AHB:

Área 1 : la llamamos interfaz SMI, que se utiliza para configurar el chip PHY externo.

Área 2 : Es la interfaz de intercambio de datos, que es la interfaz MII y la interfaz RMII que mencionamos anteriormente.

03, interfaz SMI

3.1. Interfaz de gestión de la estación: SMI

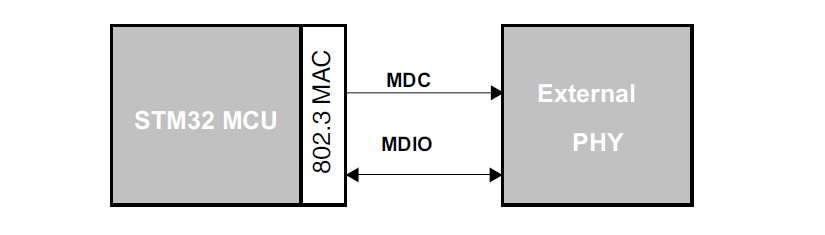

La interfaz de administración de la estación permite que cualquier solicitud de registro PHY pase a través del reloj de 2 hilos y las líneas de datos. Esta interfaz admite hasta 32 PHY.

El programa de aplicación puede seleccionar una PHY de 32 PHY, y luego seleccionar un registro de los 32 registros incluidos en cualquier PHY para enviar datos de control o recibir información de estado. Solo se puede abordar un registro en una PHY en un momento dado.

La línea de reloj MDC y la línea de datos MDIO se utilizan como E / S de función multiplex en el microcontrolador:

MDC: reloj periódico que proporciona una sincronización de referencia al transmitir datos a una frecuencia máxima de 2,5 MHz. El tiempo mínimo de alto nivel y el tiempo mínimo de bajo nivel de MDC deben ser ambos 160 ns. El período mínimo de MDC debe ser de 400 ns. En el estado inactivo, la interfaz de administración SMI lleva la señal de reloj MDC a un nivel bajo.

MDIO: flujo de bits de entrada / salida de datos, utilizado para transmitir sincrónicamente información de estado hacia / desde el dispositivo PHY a través de la señal de reloj MDC.

3.2, estructura del marco SMI

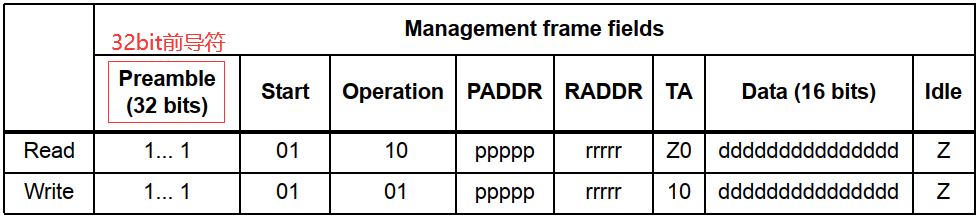

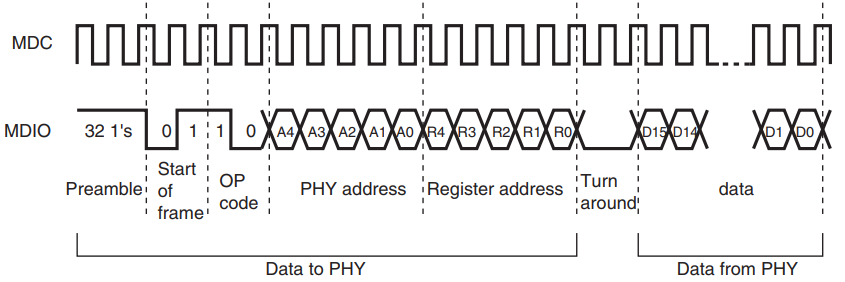

La siguiente figura muestra la estructura de la trama de la operación de lectura y la operación de escritura , y la transmisión de bits debe ser de izquierda a derecha.

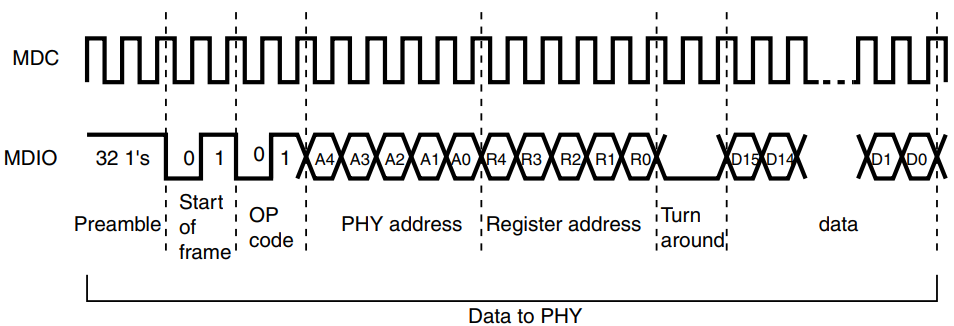

Preámbulo ( preámbulo de 32 bits ): Cada transmisión (lectura o escritura) debe comenzar con un preámbulo. El preámbulo son 32 señales lógicas consecutivas '1' en la línea MDIO y 32 señales de reloj en la línea MDC correspondiente. Esta parte de la señal se utiliza para establecer sincronización con el dispositivo PHY.

Inicio (carácter de inicio): El carácter de inicio de la trama se define como '01', es decir, la línea MDIO pasa del '1' lógico a '0' y luego vuelve a '1' para marcar la transmisión.

Comienzo.

Operación : Se utiliza para definir el tipo de operación: lectura o escritura.

PADDR : la dirección PHY tiene 5 bits, que pueden distinguir 32 PHY. Los bits altos se envían y reciben primero.

RADDR : La dirección del registro tiene 5 bits, que pueden direccionar 32 registros independientes. Los bits altos se envían y reciben primero.

TA : carácter de dirección de 2 bits, insertado entre RADDR y los datos (DATA) para evitar conflictos durante las operaciones de lectura. Durante la operación de lectura, durante estos 2 bits de TA, el controlador MAC mantiene el estado de alta impedancia de la línea MDIO, y el dispositivo PHY primero mantiene el estado de alta impedancia de 1 bit y emite una señal '0' en el segundo bit. Durante la operación de escritura, durante el tiempo de 2 bits del TA, el controlador MAC impulsa la línea MDIO para emitir una señal '10', y la configuración PHY mantiene un estado de alta impedancia.

DATOS ( datos ) : campo de datos de 16 bits. El primero en enviar y recibir es el bit 15 del registro ETH_MIID.

Bit inactivo: la línea MDIO permanece en un estado de alta impedancia. Cancele todas las unidades de tres estados y la resistencia pull-up de PHY asegura que la línea MDIO esté en el '1' lógico.

3.3, operación de escritura SMI

Cuando el programa de aplicación establece el bit de ocupación y escritura MII (registro de dirección MACMII de Ethernet (ETH_MACMIIAR)), la interfaz SMI transmitirá la dirección PHY y la dirección del registro PHY a la PHY, y luego transferirá los datos (registro de datos Ethernet MAC MII (ETH_MACMIIDR )). En el proceso de transmisión de datos en la interfaz SMI, el contenido del registro de direcciones MII y el registro de datos MII no se pueden modificar; durante este proceso (el bit de ocupado es alto), la operación de escritura en el registro de direcciones MII o el registro de datos MII se ignorará y no afectará La transferencia completa se completó correctamente. Cuando se completa la operación de escritura, la interfaz SMI borrará el bit de ocupado para informar al programa de aplicación.

La siguiente figura describe el formato del marco durante la operación de escritura.

3.4, operación de lectura SMI

Cuando el programa establece el bit de ocupado MII del registro de direcciones MACMII de Ethernet (ETH_MACMIIAR) en '1' y mantiene el bit de escritura MII en '0', la interfaz SMI envía la dirección PHY y la dirección del registro PHY para realizar la operación de lectura. el registro PHY. Durante todo el proceso de transmisión, el programa de aplicación no puede modificar el contenido del registro de direcciones MII y el registro de datos MII. Durante el proceso de transmisión (el bit de ocupado es alto), la operación de escritura en el registro de direcciones MII o en el registro de datos MII se ignorará y no afectará la finalización correcta de toda la transmisión. Una vez completada la operación de lectura, la interfaz SMI borrará el bit de ocupado y actualizará la lectura de datos desde la PHY al registro de datos MII.

La siguiente figura describe el formato de trama de la operación de lectura

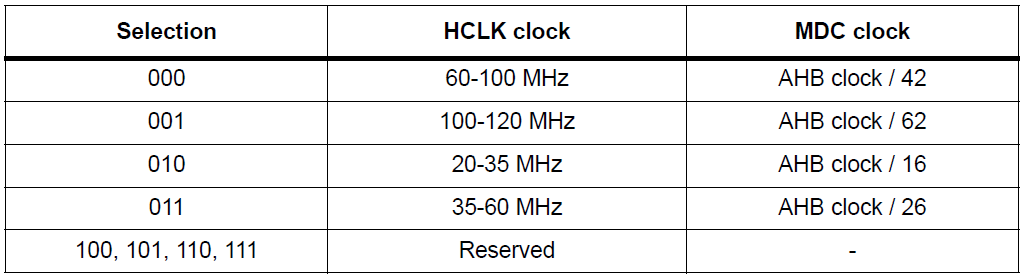

3.5, selección de reloj SMI

El MAC inicia las operaciones de escritura / lectura de gestión. El reloj SMI es un reloj dividido cuya fuente de reloj es el reloj de la aplicación (reloj AHB). El factor de división de frecuencia depende del rango de reloj configurado en el registro de direcciones MII. Ahora que se menciona el reloj aquí, mencionaré nuevamente el contenido mencionado anteriormente: cuando se usa Ethernet, el reloj AHB debe ser de al menos 25MHZ.

04, código

La inicialización de la interfaz MII del puerto de red STM32 es muy simple.

Inicialice GPIO.

RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOA | RCC_AHB1Periph_GPIOC |RCC_AHB1Periph_GPIOF, ENABLE);

/* Enable SYSCFG clock */

RCC_APB2PeriphClockCmd(RCC_APB2Periph_SYSCFG, ENABLE);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_2;

GPIO_Init(GPIOA, &GPIO_InitStructure);

GPIO_PinAFConfig(GPIOA, GPIO_PinSource2, GPIO_AF_ETH);

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_1;

GPIO_Init(GPIOC, &GPIO_InitStructure);

GPIO_PinAFConfig(GPIOC, GPIO_PinSource1, GPIO_AF_ETH);Debido a que la interfaz MII requiere la cooperación del MAC, debe ser el reloj que habilite el MAC.

RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_ETH_MAC |RCC_AHB1Periph_ETH_MAC_Tx |RCC_AHB1Periph_ETH_MAC_Rx, ENABLE);Función de lectura y función de escritura de la interfaz MII.

uint16_t ETH_ReadPHYRegister(uint16_t PHYAddress, uint16_t PHYReg)

uint32_t ETH_WritePHYRegister(uint16_t PHYAddress, uint16_t PHYReg,uint16_t PHYValue)

Haga clic para ver el álbum donde se encuentra este artículo, desarrollo de la red STM32F207

Preste atención a la cuenta oficial y reciba actualizaciones de artículos lo antes posible .