Tabla de contenido

3. Los pines correspondientes de las dos interfaces.

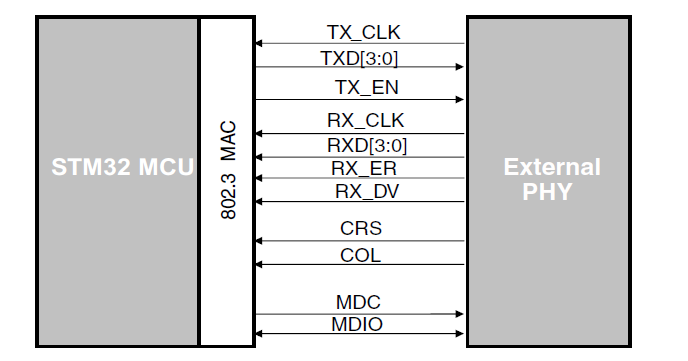

En el último artículo " Interfaz SMI de la red STM32 ", presentamos la interfaz SMI del controlador de red STM32. La interfaz SMI se utiliza principalmente para comunicarse con el chip PHY externo y configurar el registro PHY.

El flujo de datos de la comunicación de red real no se transmite a través de la interfaz SMI, sino a través de la interfaz MII o la comunicación RMII.

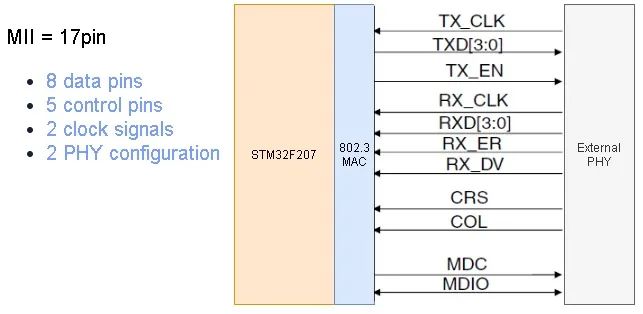

1. Interfaz MII

La Interfaz Independiente de Medios (MII) define la interconexión entre la subcapa MAC y la PHY a velocidades de transmisión de datos de 10 Mbit / sy 100 Mbit / s.

Introducción a la definición de pines:

-

MII_TX_CLK: Señal de reloj continua. Esta señal proporciona el tiempo de referencia para la transmisión de datos TX. La frecuencia nominal es: 2,5 MHz a una velocidad de 10 Mbit / s; 25 MHz a una velocidad de 100 Mbit / s.

-

MII_TXD [3: 0]: Señal de transmisión de datos. Esta señal es un grupo de 4 señales de datos, que son impulsadas sincrónicamente por la subcapa MAC y se convierte en una señal válida (datos válidos) cuando la señal MII_TX_EN es válida. MII_TXD [0] es el bit menos significativo, MII_TXD [3] es el bit más significativo. Cuando MII_TX_EN está deshabilitado, el envío de datos no tendrá ningún impacto en la PHY.

-

MII_TX_EN: Enviar señal de habilitación. Esta señal indica que el MAC está enviando nibbles para MII. Esta señal debe sincronizarse con el primer nibble del encabezado (MII_TX_CLK) y debe sincronizarse cuando todos los nibbles que se van a enviar se envían al MII.

-

MII_RX_CLK: Señal de reloj continua. Esta señal proporciona el tiempo de referencia para la transmisión de datos RX. La frecuencia nominal es: 2,5 MHz a una velocidad de 10 Mbit / s; 25 MHz a una velocidad de 100 Mbit / s.

-

MII_RXD [3: 0]: señal de recepción de datos. Esta señal es un grupo de 4 señales de datos, que son impulsadas sincrónicamente por la PHY, y son señales válidas (datos válidos) cuando la señal MII_RX_DV es válida. MII_RXD [0] es el bit menos significativo, MII_RXD [3] es el bit más significativo. Cuando MII_RX_DV está deshabilitado y MII_RX_ER está habilitado, el valor MII_RXD [3: 0] específico se usa para transmitir información específica desde la PHY.

-

MII_RX_ER: Recibir señal de error. Esta señal debe mantenerse durante uno o más ciclos (MII_RX_CLK) para indicar a la subcapa MAC que se detectó un error en algún lugar de la trama. MII_RX_DV debe verificar esta condición de error.

-

MII_RX_DV: Recibir señal válida de datos. Esta señal indica que la PHY está recibiendo nibbles recuperados y decodificados para MII. Esta señal debe estar sincronizada con el primer nibble del cuadro de recuperación (MII_RX_CLK) y permanece sincronizada con el último nibble del cuadro de recuperación. Esta señal debe desactivarse antes del primer ciclo de reloj que sigue al último nibble. Para recibir la trama correctamente, la señal MII_RX_DV debe cubrir la trama a recibir en el rango de tiempo, y su hora de inicio no debe ser posterior a la hora en que aparece el campo SFD.

-

MII_CRS: señal de detección de portadora. Cuando el medio de transmisión o recepción está en un estado no inactivo, esta señal es habilitada por la PHY. Cuando los medios de transmisión y recepción están en un estado inactivo, la PHY prohíbe esta señal. La PHY debe garantizar que la señal MII_CS siga siendo válida en condiciones de conflicto. Esta señal no necesita estar sincronizada con los relojes TX y RX. En el modo full-duplex, esta señal no tiene sentido.

-

MII_COL: señal de detección de colisiones. Después de detectar un conflicto en el medio, la PHY debe habilitar inmediatamente la señal de detección de conflictos y, mientras exista una condición de conflicto, la señal de detección de conflictos debe seguir siendo válida. Esta señal no necesita estar sincronizada con los relojes TX y RX. En el modo full-duplex, esta señal no tiene sentido.

-

MDC: la señal MDC pertenece a la interfaz SMI; consulte " Interfaz SMI de la red STM32 " para obtener más detalles .

-

MDIO: la señal MDIO pertenece a la interfaz SMI; consulte " Interfaz SMI de la red STM32 " para obtener más detalles .

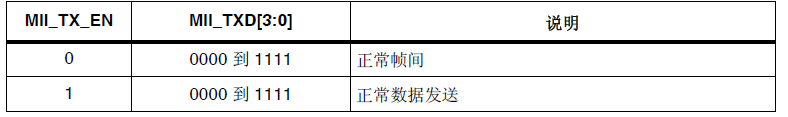

La siguiente figura codificación de la señal de la interfaz TX

La siguiente figura codificación de la señal de la interfaz RX

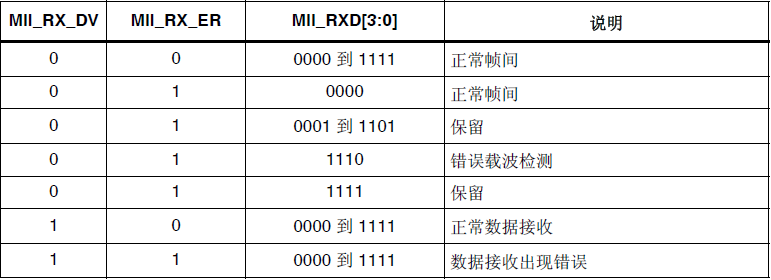

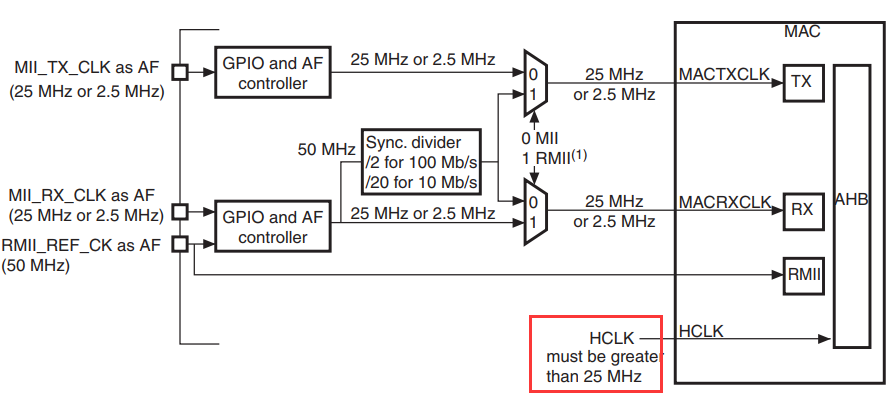

Fuente de reloj de la interfaz MII

Para generar las señales de reloj TX_CLK y RX_CLK, se debe proporcionar un reloj de 25MHz a la PHY externa como se muestra en la figura. Además de utilizar un cristal de cuarzo externo de 25 MHz para proporcionar este reloj, esta señal también se puede emitir a través del pin MCO del microcontrolador STM32F20xx. En este caso, la multiplicación de frecuencia PLL debe configurarse para obtener la frecuencia deseada en el pin MCO a través de un cristal de cuarzo externo de 25 MHz.

Código correspondiente

/* Enable GPIOs clocks */

RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOA,ENABLE);

/* Enable SYSCFG clock */

RCC_APB2PeriphClockCmd(RCC_APB2Periph_SYSCFG, ENABLE);

/* Configure MCO (PA8) */

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_8;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_100MHz;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF;

GPIO_InitStructure.GPIO_OType = GPIO_OType_PP;

GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_NOPULL ;

GPIO_Init(GPIOA, &GPIO_InitStructure);

/* Output HSE clock (25MHz) on MCO pin (PA8) to clock the PHY */

RCC_MCO1Config(RCC_MCO1Source_HSE, RCC_MCO1Div_1);2. Interfaz RMII

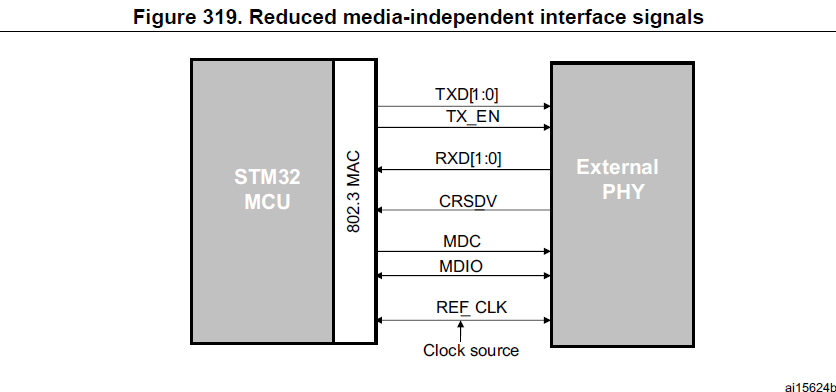

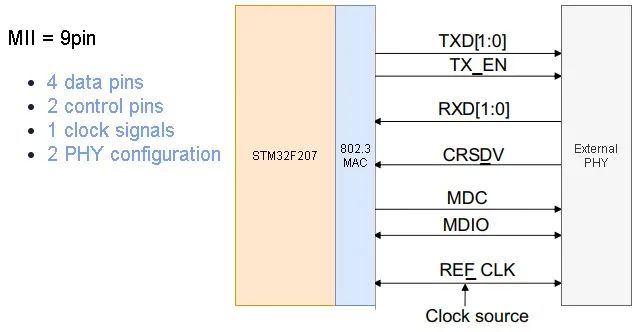

Interfaz independiente de medios reducida: RMII (interfaz independiente de medios refinada). Una breve introducción a la especificación Quality Independent Interface (RMII) reduce el número de pines entre el periférico Ethernet del microcontrolador y el PHY externo a 10/100 Mbit / s.

Según el estándar IEEE 802.3u, MII incluye 16 pines de señal de control y datos. La especificación RMII reduce el número de pines a 7 (el número de pines se reduce en un 62,5%). Consulte la interfaz MII para conocer el significado de los pines.

La interfaz RMII es un objeto instanciado entre MAC y PHY. Estos ayudan a que la interfaz MII de MAC se convierta a la interfaz RMII. La interfaz RMII tiene las siguientes características

-

Tasa de funcionamiento de 10 Mbit / sy 100 Mbit / s

-

El reloj de referencia debe ser de 50 MHz.

-

El mismo reloj de referencia debe proporcionarse externamente al MAC y al PHY Ethernet externo

-

Proporciona rutas de transmisión y recepción de datos independientes de 2 bits de ancho (doble bit)

Aquí hay menos pines de reloj que la interfaz MII, hay un punto muy importante, es decir, la fuente de reloj de la interfaz RMII debe ser 50MHZ

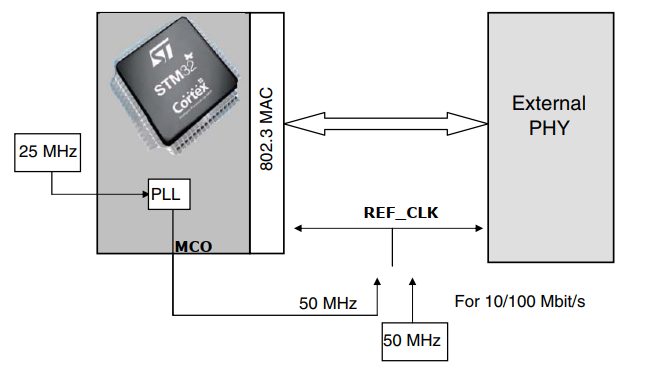

Fuente de reloj de interfaz RMII

El controlador STM32F207xx puede proporcionar una señal de reloj de 50 MHz desde el pin MCO. Por supuesto, el usuario debe configurar el PLL para generar este reloj.

Utilice un reloj externo de 50 MHz para controlar el PHY o utilice un PLL integrado para generar una señal de frecuencia de 50 MHz para controlar el PHY.

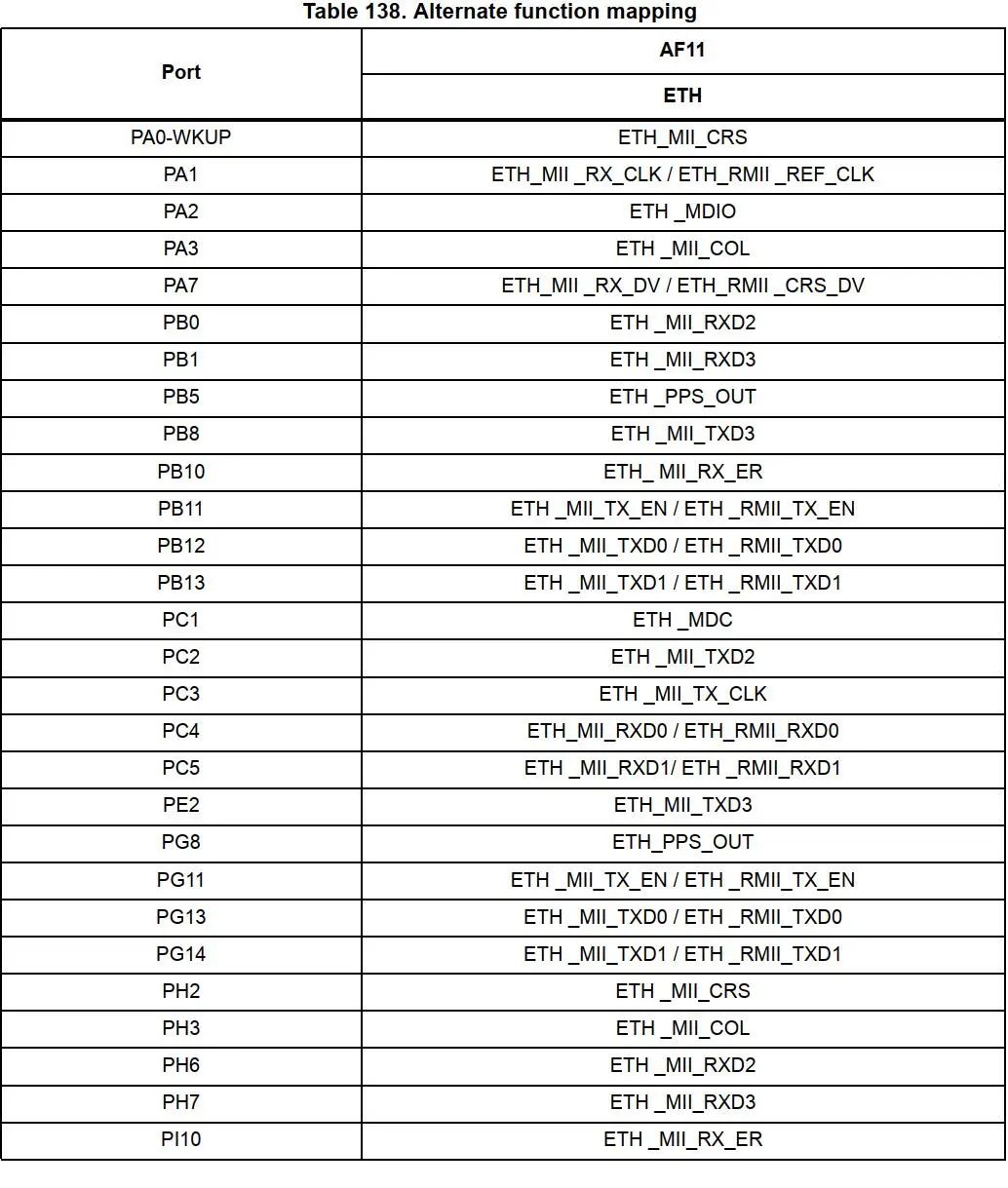

3. Los pines correspondientes de las dos interfaces.

Chip STM32F207VCT6 (100 pines)

Ethernet pins configuration

ETH_MDIO -------------------------> PA2 pin 25

ETH_MDC --------------------------> PC1 pin 16

ETH_PPS_OUT ----------------------> PB5 pin 91

ETH_MII_CRS ----------------------> PA0 pin 23

ETH_MII_COL ----------------------> PA3 pin 26

ETH_MII_RX_ER --------------------> PB10 pin 47

ETH_MII_RXD2 ---------------------> PB0 pin 35

ETH_MII_RXD3 ---------------------> PB1 pin 36

ETH_MII_TX_CLK -------------------> PC3 pin 18

ETH_MII_TXD2 ---------------------> PC2 pin 17

ETH_MII_TXD3 ---------------------> PB8 pin 95

ETH_MII_RX_CLK/ETH_RMII_REF_CLK---> PA1 pin 24

ETH_MII_RX_DV/ETH_RMII_CRS_DV ----> PA7 pin 32

ETH_MII_RXD0/ETH_RMII_RXD0 -------> PC4 pin 33

ETH_MII_RXD1/ETH_RMII_RXD1 -------> PC5 pin 34

ETH_MII_TX_EN/ETH_RMII_TX_EN -----> PB11 pin 48

ETH_MII_TXD0/ETH_RMII_TXD0 -------> PB12 pin 51

ETH_MII_TXD1/ETH_RMII_TXD1 -------> PB13 pin 52Entre ellos, el pin ETH_PPS_OUT está protegido por la demostración oficial de ST y no pertenece a la interfaz MII ni a la interfaz RMII. Las estadísticas no se ingresarán a continuación.

Hay un total de 15 interfaces MII más una interfaz SMI y un total de 17 pines. (Sin pines que contengan un reloj de 25 MHz)

RMII tiene un total de 7 interfaces más la interfaz SMI, un total de 9 pines.

Además del pin mencionado anteriormente correspondiente a la interfaz MII y la interfaz RMII que he contado por mí mismo, el funcionario de ST también da el diagrama correspondiente en el manual de referencia, de la siguiente manera:

4. Elección de MII y RMII

Utilice el bit de configuración 23 MII_RMII_SEL en el registro SYSCFG_PMC (nota: esto es diferente de F107, que es el registro AFIO_MAPR) para seleccionar el modo MII o RMII. Antes de que el controlador Ethernet esté en el modo de reinicio o el reloj esté habilitado, el programa de aplicación debe configurar el modo MII / RMII.

La función de biblioteca ST correspondiente es

//函数入参可选以下

//SYSCFG_ETH_MediaInterface_MII: MII mode selected

//SYSCFG_ETH_MediaInterface_RMII: RMII mode selected

void SYSCFG_ETH_MediaInterfaceConfig(uint32_t SYSCFG_ETH_MediaInterface) Esquema de reloj interno MII / RMII

Es compatible con MII y RMII y el esquema de reloj requerido para el funcionamiento de 10 y 100 Mbit / s, como se muestra en la figura siguiente.

Tenga en cuenta que el cuadro rojo en la figura anterior: HCLK debe ser superior a 25 MHz. Este problema se mencionó en el artículo anterior " Interfaz SMI para redes STM32 ". Aquí nuevamente, si no se cumple esta condición, pueden ocurrir rarezas. El problema es difícil de encontrar.

En el manual oficial, hay otra oración

![]()

Para guardar pines, dos señales de reloj de entrada, RMII_REF_CK y MII_RX_CLK, deben multiplexarse en el mismo pin GPIO.

Haga clic para ver el álbum donde se encuentra este artículo, desarrollo de la red STM32F207

Preste atención a la cuenta oficial y reciba actualizaciones de artículos lo antes posible .