1, the AHB system bus into APB1 (36MHz) and APB2 (72MHz), wherein 2> 1, meaning that high-speed devices connected APB2;

2, Stm32f10x.h corresponds reg52.h (which define the basic operation of the bit), the other is stm32f10x_conf.h specially configured control peripheral devices, i.e. the switching action of the first document;

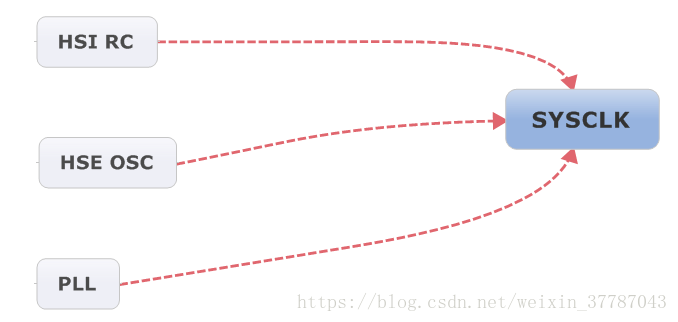

3, HSE Osc (High Speed External Oscillator) high-speed external crystal, typically 8MHz, HSI RC (High Speed InternalRC) high-speed internal RC, 8MHz;

4, LSE Osc (Low Speed External Oscillator) low external crystal, typically 32.768KHz, LSI RC (Low Speed InternalRC) low internal oscillator, probably about 40KHz, provides an automatic wakeup unit watchdog timer and clock source;

5, SYSCLK clock source from three sources: HSI RC, HSE OSC, PLL;

6, MCO [2: 0] may provide different clock synchronization signal source 4;

7, GPIO port looks like two anti-series diodes as clamping diode;

8, bus matrix using rotation algorithm and the system bus DMA arbitrating

9, ICode bus, the DCode bus, a system bus, the DMA bus, a bus matrix, AHB / APB bridge

10, prior to use in a peripheral, the register must be set to open the peripheral RCC_AHBENR clock

11, the data stored in the form of little-endian byte stored in a memory

12, the memory map is divided into eight chunks, each block is 512MB

13, FLASH page of 1K (small and medium capacity), a large capacity is 2K.

14, system memory area (SystemMemory) factory configured for the ST companies locked, users can not edit, used to reprogram the FLASH area. Be sure to select the programming process so we BOOT1 = 0, so for the FLASH programming via built-in bootstrap program, such as the interrupt vector table and code

15, STM32 core voltage of 1.8V

16, STM32 three Reset: reset, power-on reset, the backup area is reset. Wherein the system is reset in addition to the value of the reset flag and RCC_CSR BKP is not reset, all other registers are all reset. Trigger such as an external reset, watchdog reset, software reset; reset because the power supply of the external power / standby mode or power-down reset return. In addition to the BKP reset register value is not fixed, all of the other reset; reset trigger source region of the backup software reset or power down all the VDD and VBAT.

17, processor reset all I / O ports are floating input state

18, 68 maskable interrupt channels, 16 programmable priority interrupt core 16, a total of 68 + 16 = 84 interrupts. 103 series only 60 interrupts, 107 series have 68 interrupts

19, the system starts from the beginning of 0x00000004, 0x000 0000 reserved

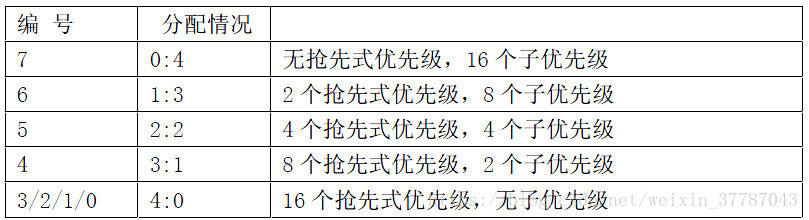

20, (NestedVectored Interrupt Controller) NVIC NVIC, divided into two types: preemptive priority (nestable) and interrupt priority (sub priority, not nested). Two kinds of priorities determined by the 4-bit binary digit. Allocation down sixteen kinds of situations: