In Cortex-R52: GIC, we briefly describe the GIC-related configuration registers and interrupt types. Next, we will talk about the configuration methods of SGI, SPI, and PPI.

According to the description in R52 TRM, an interrupt is represented by INTID, and the relevant settings for an interrupt are as follows:

- Enable: Only enabled interrupts will be sent to the core; but unenabled interrupts will be pending if they occur;

- Priority: 5-bit priority configuration, the smaller the value, the higher the priority

- Interrupt triggering behavior: level triggering or edge triggering

- Set Group: IRQ or FIQ

- Set routing target: target core or cores

1. Configuration of SPI, PPI and SGI interrupts

1.1 Configuration items

| Setting | Spis | SGIs & PPIs |

| Enable | GICD_ISENABLERn GICD_ICENABLERn |

GICR_ISENABLERn GICR_ICENABLERn |

| Priority | GICD_IPRIORITYn | GICR_IPRIORITYn |

| Configuration (level or edge) | GICD_ICFGRn | GICR_ICFGRn |

| Group | GICD_IGROUPn | GICR_IGROUPn |

| Routing (target core/cores) | GICD_IROUTERn | N/A |

PPI does not need to configure Route because it is private to the core.

1.2 Code examples

if(INT_IS_SPI(intID))

{

REG32_WRITE(gicd_base_addr, gicd_isenabler_offset_x, enable_mask)

REG32_WRITE(gicd_base_addr, gicd_irouter_offset_x, affinity_mask)

REG8_WRITE (gicd_base_addr, gicd_ipriorityr_offset_x, prio_mask)

REG32_WRITE(gicd_base_addr, gicd_icfgr_offset_x, cfg_mask)

}

else

{

REG32_WRITE(gicr_base_addr, gicr_isenabler0/1, enable_mask)

REG8_WRITE (gicr_base_addr, gicr_ipriorityr0/1, prio_mask)

if(INT_IS_PPI(intID))

{

REG32_WRITE(gicr_base_addr, gicr_icfgr1, cfg_mask)

}

}

What needs to be explained here is the router register IROUTER32-991. The bit field structure of this register is as follows:

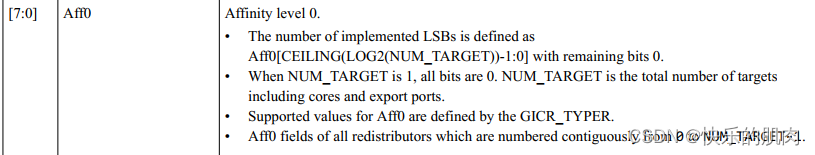

For R52, Aff3 only reads 0, and Aff2/1 is fixed according to the configuration of the chip design. In fact, for the single-core cluster R52, Aff2 and 1 are basically 0; then the only thing that can be changed is There is only Aff0. The detailed explanation of this bit field is as follows:

So where does this value come from? MPIDR (see Cortex-R52: affinity for details )

So where does this value come from? MPIDR (see Cortex-R52: affinity for details )

That is to say, now I want to route an SPI to core 2, then I must first obtain the affnity0 of the core (through MPIDR), and then write it to this register. And, note that this register is 64bit.

2. Precautions

2.1 Initialization of GIC module

GIC consists of three modules, so these three modules also need to be initialized.

| module | Register operations | explain |

| Distributor | 1. GICD_CTRL.EnableGrp0/1 setting 1 2. GICD_CTRL.ARE does not need to be set (enabled by default, RAO/WI (Read as one, write ignore)) |

The default value is 0, enabling IRQ and FIQ groups; Affinity routing is enabled by default |

| Redistributor | GICR_WAKER.ProcessorSleep set to 0 Tell the connected core that I'm going to wake up |

The default value is 1; The software must poll the ChildrenAsleep status to be 0 before jumping; This operation must be completed before configuring the CPU interface. |

| CPU interface | 1. Check whether ICC_SRE.SRE is 1 (RAO/WI) 2、ICC_IGRPEN0/1 3. ICC_PMR.Priority sets the priority mask 4. ICC_BRPn sets the preemption policy |

1. The hardware default is 1 2. Set Group0 and 1 to enable 3. Configure the priority mask sent to the CPU. Generally, the default is FF. |

2.2 Summary of interrupt configuration

| Interrupt type | Configuration items |

| SPI(32-991) | 1. Priority: GICD_IPRIORITYRn 2. Interrupt Group GICD_IGROUPRn 3. Trigger type GICD_ICFGRn 4. Routing purpose GICD_IROUTERn 5. Interrupt enable GICD_ISENABLERn |

| PPI(16-31) & SGI(0-15) |

1. Priority GICR_IRPIORITYRn(n= 0-7) 2. Interrupt Group GICR_IGROUPR0 3. Trigger type GICR_ICFGR0/1 4. Interrupt enable GICR_ISENABLER0 |