The most recently been doing uboot transplant-related work, we need to uboot-2016-7 ported to ARMv7 processor unit design. New Year's Day holiday for three days just nothing else to do, there was complete at the time the most recent results of the work to organize. Before learning uboot, read many articles on the Internet, many of which are based on the old version of uboot, and many are beginning analysis directly from the code, uboot does not combine with the ARM processor architecture. After all, a lot of time to do one thing, you know how to do it and you know it so why do two different concepts. Namely English often say: how do? And why do?

The new version of the July 2016 release of uboot transplanted to the board units and debugging, this will also share my learning outcomes for everyone. Paper, there are many places to join my own understanding, may not be accurate, I hope we propose amendments.

Before you start understanding the processor starts the process, please have two tools:

Source Package 1.uboot-2016-7

(Open source just download the official Download: ftp: //ftp.denx.de/pub/u-boot/ download u-boot-2016.07.tar.bz2)

2. Code reading software source insight

(Recommended! Uboot source package can imagine there are more than 10,000 files, each file has hundreds or even thousands of lines of code line. How no professional code reader to find the function prototypes. Of course, not all need to look at! According to their needs go to View)

Well simultaneous download these technical documentation

(I read in the learning uboot several documents can be read on demand to find absolutely no need to re-read head tail)

ARMv7-A architecture 1.arm company official offer document structure

《ARM® Architecture Reference Manual ARM®v7-A and ARM®v7-R 》

(Official quality assurance! If you think the English can look at hard to see Du Chunlei "ARM architecture and programming")

2. "Uboot in start.S source of detailed instruction-level analytical _v1.6.pdf" (Okay Chinese drop)

(Extremely helpful in understanding gnu arm compilation)

3. "ARM Instruction Set Quick Query Manual .pdf" (Chinese drops)

(Tool manuals, instructions quickly find all kinds of arm usage)

4. "ARM instruction Explanation [the ARM Standard] .pdf" (Chinese or drops)

(Arm some of the norms and common form of compilation of many useful examples: subroutine calls, bulk transfer, block replication of the program is helpful to write bare metal, is also of great help in understanding uboot kernel and boot code.)

5. "programmer's self-cultivation - link is loaded with the library .pdf" (all in Chinese drops)

(The most important part of the program which will introduce ELF file links course is to help understand the core uboot relocation! This is really important !!)

Well, now to business.

What is uboot?

In the embedded operating system, Boot Loader is run before the operating system kernel to run. Can initialize the hardware devices, the establishment of memory space map, the system hardware and software environment which will bring an appropriate state, in order for the final call to the operating system kernel ready for the right environment. In embedded systems, usually it does not like that kind of BIOS firmware (note, some embedded CPU will be built for a short startup program), so the whole system is fully loaded to start the task done by the Boot Loader. uboot bootloader is a kind of, the full name of Universal Boot Loader.

Goal: to start uboot ARMv7 processor unit design.

Question: How to start? What processes are started?

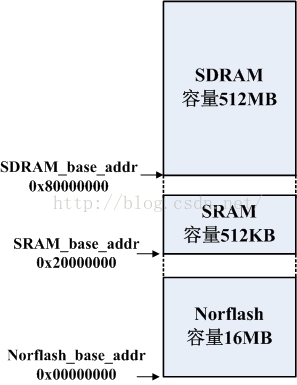

First of all, I would like to use to describe the memory on this board need of uboot transplant (processor architecture may temporarily not considered, I would go back uboot analyze the structure of the document processor initialization ARMv7-A architecture arm of the company official the assembly code. whether it is arm9 arm11 armv7 armv8 is the same routine, you first need based on memory resources to customize their startup process). The use of memory resources on this board in my hand: Norflash (16MB) SRAM (512KB) SDRAM (512MB).

See here should think of two questions:

What are the similarities and differences between them as 1. Norflash SRAM SDRAM memory?

2. How to start the arm processor through them? (Important things to say three times: first we must understand the process before you start to see the uboot source code or else can not understand looked embedded code is closely related with the hardware to go read the code to see the hardware multiplier)

I will resolve these problems in order to make the following:

A. Norflash SRAM SDRAM similarities and differences

norflash: norfalsh is a nonvolatile memory (data remains stored in norflash after losing power supply), NOR flash with SRAM interface, sufficient to address the address pins, it can easily be read every word in the inside thereof section (note that reading can be written to the flash is not random, usually write NOR flash process is:! unblocked -> erase -> write data because the flash feature is only flipped from 1-0, we can not flip from 0. 1. the erasure process is to a certain sector in the flash write 0xFFFFFFF full, then the write data), code instructions can be run directly on norflash. (Important! After power norfalsh data can be read in the write operation can not be performed directly in front of me have said very clearly)

SRAM: Static random access memory (Static Random Access Memory) which is a type of semiconductor memory. "Static" means that they do not power down, the data stored in the SRAM will not be lost. This dynamic RAM (DRAM) different, DRAM requires periodic refresh operation. Then, we will not SRAM read only memory (ROM) and confused Flash Memory, SRAM as a volatile memory, it is only holding case be able to maintain a continuous supply of data at the power supply. "Random access" refers to the contents of the memory can be accessed in any order, regardless of what previous visit a location. (Important! After power-on can read and write data in the SRAM without initialization)

SDRAM: synchronous dynamic random access memory (Synchronous Dynamic Random Access Memory) need to constantly refresh in order to save the data. And the ranks of address multiplexing, many with page mode. (Important! Ddr controller needs to be initialized to <configuration register>, to read and write data to the SDRAM)

Finally, under the table to summarize:

The memory

on the memory access state power

after power failure memory data state

NORFLASH

data can be read, can not write directly to human

data exist

SRAM

can write data directly read

data does not exist

SDRAM

not DDR controller after power initialization

data can not be read write

data does not exist

Introduced in front of Norflash SRAM SDRAM memory characteristics, following on to talk about their respective functions and tasks (important !! Norflash SRAM SDRAM completed the task in arm processor start-up phase, are based on their respective characteristics of storage. If for Norflash SRAM SDRAM memory characteristics I described earlier can not quite understand the students themselves Baidu further in-depth understanding.)

Norflash properties: Nonvolatile (after loss of supply data stored in norflash still exists), directly <reads> data, can not be directly <write> data.

Norflash arm processor as a program memory. You can imagine, if the program memory after power-down inside the data is gone. So how self-starting your computer, you do not have to re-program before each boot code once. Here you can think about a problem after power norflash can be seen as a read-only memory random read. But the program we run, .text segment in general (code segment) is read-only (ok) ,. rodata (read-only data segment) is read-only (also ok). Then the question is, for the .data segment (data segment) and .bss (uninitialized global and static variables) in the course of running the value of the variable (variable value change requires a change in the underlying hardware to complete operation <written in the corresponding address (physical address stored in the variable address) data>). Unfortunately Norflash can not directly read write directly. (Important! How to solve this problem? Then you need the power SRAM SRAM because after you can go directly to the reader, the following I will explain the function and role under the SRAM)

SRAM characteristics: volatile down (after loss of supply data stored in the SRAM does not exist), can freely <write> data. (Small capacity Important:! Fast running speed 512KB expensive!).

In actual operation, SRAM can be used as stack space c language runtime. The arm processor sp (stack pointer register) provided sram provided c language runtime environment. Questions about global variables, I mention alone, uboot before the relocation (uboot will be transported from the mirror to flash in front ddr continue to run), whether or c assembler program does not define global variables. Only defines a structure pointer gd_t * gd_ptr uboot length for storing mirrored address relocation information, will the r9, r9 address value stored in the address storage gd_ptr subtracting a top sram sizeof (gd_t). (Stored in the sram where you can freely read and write the thing behind when analyzing the code uboot I will explain in detail)

SDRAM features: power failure volatile (after the loss of supply data stored in the SDRAM does not exist), the DDR controller is not initialized after power, can not read and write data. (Important Mass:! 512MB to run faster price own guess <must be cheap>)

Since the need to use a large capacity SDRAM, the clock must be configured and registers ddr ddr controller. This step is where it completed? (think for a while)

Yes that is done in norflash and SRAM built a program operating environment. What to complete it?

1. complete the initialization of the processor clock

2. DDR initialization

3. Assignment to gd_t * gd_ptr (uboot length for storing mirrored address relocation, the relocation offset information)

In uboot minimal handling system is initialized before running to the DDR, after uboot will be carried to the running ddr.

(Important! At this point Norfalsh and SRAM task is complete (and maybe useless), uboot now on the run in the ddr)

Two. Arm processor boot process analysis

Front explain the role of each start-up phase in the processor memory, the following summarizes what the startup process.

Sometimes he could not describe, directly on the map. The following figure shows the hand piece ARM processor memory address space (including the address space and size of each of the memory capacity in the arm processor)

So start the process can be summarized as follows:

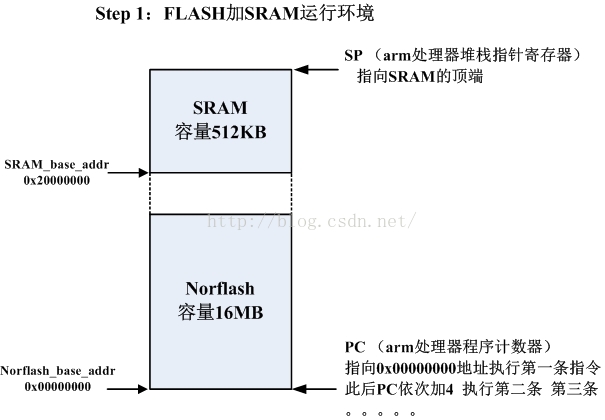

step1.uboot image (i.e. the bin important! elf file is not a bin file itself, and the similarities and differences Baidu elf file) stored in the norflash, after power ARM default first instruction is fetched from the address 0x00000000. When running the process C, the parameter stack and local variables need, the stack is provided to the top of the SRAM, provides a C program execution environment. Gd_t * gd_ptr assignment complete (image information storing uboot length relocation address, etc.).

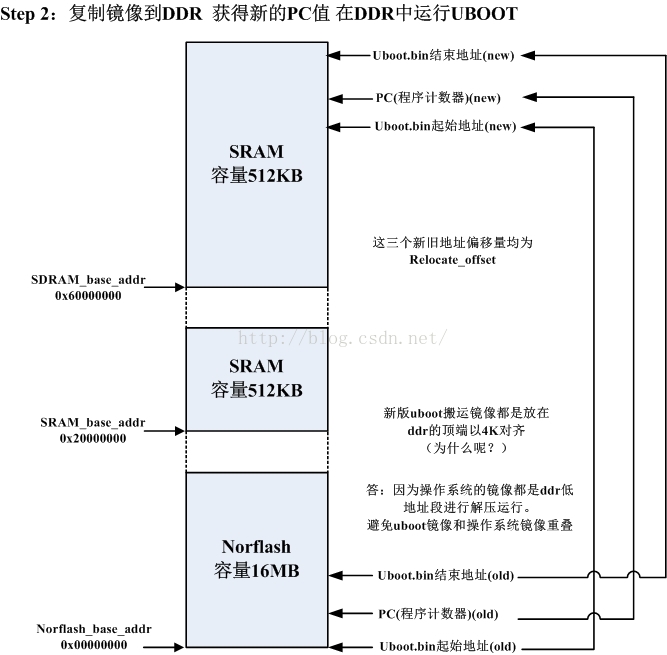

Step2. In the first stage will complete the configuration and DDR clock as well as the arm processor assignment gd_t * gd_ptr (uboot length for storing mirrored, relocation information, address, etc.). At this time, SDRAM can read and write data normally. Copied into the SDRAM (relocation addresses are provided by gd_t * gd_ptr) uboot image, obtained in accordance with the new pointer value PC relocation offset and continue uboot in the DDR.

Here I would like to mention that address the uboot run in ddr with its link address inconsistencies (original norflash in text_base = 0x0 runs after ddr in text_base = 0x70453670), the compiler will determine which variables and function when linked absolute address, link address load address to run address should be the same (in most cases just write bare metal program).

(1) How to addressing function calls (during the execution of the function is to jump to an address up implementation of a code)

(2) How to global variables in an addressing operation (the address of the global variable becomes how to find the read and write)

After how (3) for the global pointer stored in the variable or functions of other variables to address in the DDR relocation?

First on this issue later I will write a blog dedicated to an executable statically linked with the process of dynamic linking process uboot relocation process together more interested can go directly to reading this blog.

Step3. continues to run in the DDR ARM processor uboot complete the initialization of each peripheral hardware, such as SPI, I2C, network cards and the like. Uboot into the final main_loop, terminal block waiting for serial input or a command to start the kernel. The main role has always been to make one thing clear uboot is initialized by Flash and Sram clock and DDR (arm minimal system), the final uboot is required to run bare-metal debug ddr or to boot the operating system kernel.

(How to write commands uboot uboot bare-metal debug and how to boot the operating system behind me in turn introduced)

Finally, figure or the <Start flowchart>:

After power arm default first instruction is fetched from the address 0x00000000. SP points to the top of the SRAM, when running the program C, the parameter stack and local variables need, SP minus 4 sequentially stack. In this part of the program operation to complete the configuration of the clock and ddr (ARM minimum system) as well as the assignment of gd_t * gd_ptr (uboot length for storing mirrored address relocation, the relocation information such as offset). At this time, ddr been successfully read and write data, the image is copied from flash to uboot DDR, obtaining a new position based PC relocation offset uboot continue to run.

step3

uboot has been running in the ddr, there would be no restrictions on any hardware. step3 ARM processor complete the initialization of each peripheral hardware, such as SPI, I2C, network cards and the like. Uboot into the final main_loop, terminal block waiting for serial input or a command to start the kernel.

These are the startup process arm processor, whether it figured out?

Next I will take the Samsung S3C2410 produced and S5PV210 as an example, explain that they start from nandflash. For now on mobile phones and tablets widely used eMCC (internal nandflash is just a change of read-write interface) is the same routine (remember that all things were separated from their maintaining the status quo).