Comme on peut le voir sur le schéma fonctionnel de FlexSPI dans la section précédente, SEQ_CTLle contrôle de la synchronisation de la mémoire externe est réalisé. Différentes mémoires ont des temporisations différentes, et cette temporisation est spécifiée par LUT( ). Il possède son propre registre, lors de sa mise en place, les opérations de lecture, d'écriture et d'effacement de la mémoire externe seront effectuées en fonction de la configuration dans le registre. En plus du tableau de configuration, certains paramètres de FlexSPI doivent être configurés pour s'adapter à différentes conceptions matérielles et différentes mémoires externes.Look Up TableLUTLUTLUT

Annuaire d'articles

1 Composition du tableau LUT

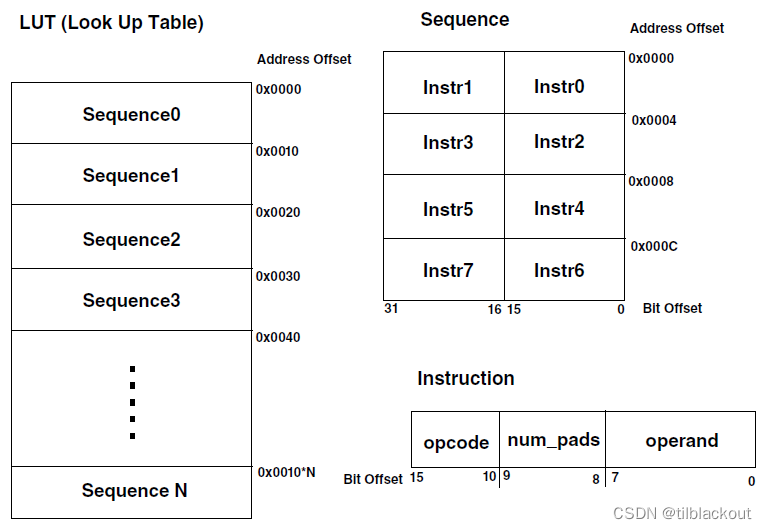

LUTLa composition de la table est illustrée dans la figure ci-dessous. Une table contient plusieurs champs Sequence, une Sequencecontient 8 champs Instructionet Instructionelle se compose de trois champs opcode: , , num_padset operand.

(1)opcode

Il s'agit de certains opcodes fixes définis par le matériel FlexSPI, tels que les opérations de lecture de données, les instructions vides, les instructions d'arrêt, etc. ont leurs opcodes correspondants.

| Nom | Code d'opération | but | Transmettre des données | Bits/octets/numéro de cycle |

|---|---|---|---|---|

| CMD_SDR/CMD_DDR | 0x01/0x21 | code de commande | Opérande[7:0] | 8 bits |

| RADDR_SDR/RADDR_DDR | 0x02/0x22 | adresse de ligne | Adresse_ligne[31:0] | Les bits de l'adresse de ligne sont spécifiés par operand[7:0] |

| CADDR_SDR/CADDR_DDR | 0x03/0x23 | adresse de colonne | Adresse_colonne[31:0] | Les bits de l'adresse de colonne sont spécifiés par operand[7:0] |

| MODE1_SDR/MODE1_DDR | 0x04/0x24 | séquence de motifs | Opérande[0] | 1 bit |

| MODE2_SDR/MODE2_DDR | 0x05/0x25 | séquence de motifs | Opérande[1:0] | 2 bits |

| MODE4_SDR/MODE4_DDR | 0x06/0x26 | séquence de motifs | Opérande[3:0] | 4 bits |

| MODE8_SDR/MODE8_DDR | 0x07/0x27 | séquence de motifs | Opérande[7:0] | 8 bits |

| WRITE_SDR/WRITE_DDR | 0x08/0x28 | écrire des données | IP TX FIFO ou AHB_TX_BUF | Taille de rafale AHB ou IPCR1[IDATSZ] |

| READ_SDR/READ_DDR | 0x09/0x29 | lire des données | - | Taille de rafale AHB ou IPCR1[IDATSZ] |

| LEARN_SDR/LEARN_DDR | 0x0A/0x2A | Lire les données/bit de guidage (synchronisation d'apprentissage) | - | Déterminé par l'opérande[7:0] |

| DATSZ_SDR/DATSZ_DDR | 0x0B/0x2B | Longueur des données de lecture/écriture de la séquence actuelle | Principalement utilisé dans FPGA, dépend de sa logique interne | Déterminé par l'opérande[7:0] |

| DUMMY_SDR/DUMMY_DDR | 0x0C/0x2C | retarder l'attente | - | Le cycle du mannequin (SCLK) est déterminé par l'opérande[7:0] |

| DUMMY_RWDS_SDR/DUMMY_RWDS_DDR | 0x0D/0x2D | Synchronisation d'horloge pour les données et les commandes dans les appareils HyperBus | - | Lié à l'opérande [7: 0] et à la broche DQS |

| JMP_ON_CS | 0x1F | saut de séquence | - | - |

| ARRÊT | 0x00 | séquence d'arrêt | - | - |

- Pour

JMP_ON_CSetSTOP, leursnum_padsseront ignorées ; tandis que d'autres directives sont spécifiées selon différentes directivesnum_pads

(2)num_pads

Le nombre de lignes de données utilisées pour communiquer avec la mémoire externe, les valeurs sont les suivantes :

#define FLEXSPI_1PAD 0

#define FLEXSPI_2PAD 1

#define FLEXSPI_4PAD 2

#define FLEXSPI_8PAD 3

Par exemple, pour une HyperRAM à huit fils, ce paramètre est lors de la transmission de données FLEXSPI_8PAD , c'est-à-dire que les données sont transmises sur toutes les lignes connectées au matériel. Mais pour certaines instructions, num_padsil suffit de le définir sur FLEXSPI_1PAD, comme l'instruction d'arrêt, qui n'a besoin que d'un bit de données.

(3)operand

C'est-à-dire le paramètre correspondant à l'opcode précédent.

2 Configuration de la structure FlexSPI

Pour différentes mémoires externes, il existe différentes largeurs d'adressage de ligne/colonne, différentes tailles de mémoire et d'autres paramètres, et ces paramètres sont configurés dans la structure liée à FlexSPI. Prenons d'abord le code d'initialisation d'HyperRAM comme exemple, et regardons le code d'initialisation de FlexSPI :

flexspi_device_config_t deviceconfig = {

.flexspiRootClk = 332000000,

......//略

};

flexspi_config_t config;

/* Get FLEXSPI default settings and configure the flexspi. */

FLEXSPI_GetDefaultConfig(&config);

FLEXSPI_Init(EXAMPLE_FLEXSPI, &config);

/* Configure RAM settings according to serial RAM feature. */

FLEXSPI_SetFlashConfig(EXAMPLE_FLEXSPI, &deviceconfig, kFLEXSPI_PortA1);

/* Update LUT table. */

FLEXSPI_UpdateLUT(EXAMPLE_FLEXSPI, 0, customLUT, ARRAY_SIZE(customLUT));

/* Do software reset. */

FLEXSPI_SoftwareReset(EXAMPLE_FLEXSPI);

D'après le code ci-dessus, nous pouvons savoir que pendant le processus d'initialisation, flexspi_config_tces flexspi_device_config_tdeux structures doivent être remplies par nous. Les flexspi_config_tprincipaux sont la configuration de certaines fonctions de FlexSPI, et flexspi_device_config_tcertaines configurations de synchronisation et de paramètres de mémoires spécifiques.

2.1 flexspi_config_t

flexspi_config_tLa définition de la structure est la suivante, et l'explication détaillée de chaque paramètre est écrite dans les commentaires.

typedef struct _flexspi_config

{

/* 读数据使用的时钟源 */

flexspi_read_sample_clock_t rxSampleClock;

/* 在没有外部驱动时,SCK将以固定频率产生脉冲 */

bool enableSckFreeRunning;

/* 使能PORTA和PORTB的数组组合来支持8位访问 */

bool enableCombination;

/* 是否使能低功耗Dozeoze模式 */

bool enableDoze;

/* 将时钟速率减缓一半,减慢传输速度但增大容错率 */

bool enableHalfSpeedAccess;

/* 使能SCKB作为SCKA的差分时钟,若使能PORTB的设备无法访问 */

bool enableSckBDiffOpt;

/* 若使能FLASHA1CRx寄存器的配置会共享给其它的设备 */

bool enableSameConfigForAll;

/* 命令执行的超时周期,防止系统卡在等待某个状态上,系统将在ahbGrantTimeoutCyle*1024个串行时钟周期后返回超时 */

uint16_t seqTimeoutCycle;

/* IP命令执行的超时周期,系统将在ipGrantTimeoutCycle*1024个AHB时钟周期后返回超时 */

uint8_t ipGrantTimeoutCycle;

/* IP发送FIFO大小,与串口watermark类似,只有满了才发 */

uint8_t txWatermark;

/* 接收FIFO大小,只有满了才收 */

uint8_t rxWatermark;

struct

{

/* FlexSPI从AHB总线获取执行命令的访问权限的超时时间 */

uint8_t ahbGrantTimeoutCycle;

/* AHB读写访问超时周期 */

uint16_t ahbBusTimeoutCycle;

/* FlexSPI支持暂停当前命令序列而稍后执行,该值表示在后续恢复命令前等待的空闲周期数 */

uint8_t resumeWaitCycle;

/* 使能在每次数据传输完成后清除RX/TX的buffer */

bool enableClearAHBBufferOpt;

/* 控制是否移除AHB读取突发起始地址对齐限制,若使能,突发读取地址没有字节对齐限制 */

bool enableReadAddressOpt;

/* 使能AHB读取预取功能:在完成当前AHB突发读取后,预先读取一些额外的数据到缓冲区中以加快后续读取,但这会增加功耗 */

bool enableAHBPrefetch;

/* 是否开启AHB写缓冲访问:在执行写命令后,不等待其执行完毕就返回,允许后续指令继续执行,提高系统的并发性 */

bool enableAHBBufferable;

/* 使能AHB总线缓存读取,若命中则从缓存中读取,但要确保数据的一致性 */

bool enableAHBCachable; /*!< Enable AHB bus cachable read access support. */

} ahbConfig;

} flexspi_config_t;

2.2 flexspi_device_config_t

flexspi_device_config_tLa structure est définie comme suit :

typedef struct _flexspi_device_config

{

/* FLEXSPI串行根时钟频率 */

uint32_t flexspiRootClk;

/* 是否启用第二个串行时钟线:硬件上连了两个时钟线 */

bool isSck2Enabled;

/* 外部存储设备的大小,以KB为单位 */

uint32_t flashSize;

/* 定义在连续的CS信号之间的时间间隔单位:1或256个串行时钟周期 */

flexspi_cs_interval_cycle_unit_t CSIntervalUnit;

/* CS线的保持时间,单位为CSIntervalUnit */

uint16_t CSInterval;

/* CS线的保持时间 */

uint8_t CSHoldTime;

/* CS线设置时间,即在发送片选信号之前需要等待的时间 */

uint8_t CSSetupTime;

/* 在读取数据之后,数据保持有效的时间 */

uint8_t dataValidTime;

/* 列地址宽度 */

uint8_t columnspace;

/* 是否使用字地址来访问外部设备,有的存储设备支持按字传输 */

bool enableWordAddress;

/* AHB写命令的序列ID:对应LUT表格中的顺序 */

uint8_t AWRSeqIndex;

/* AHB写命令的数量 */

uint8_t AWRSeqNumber;

/* AHB读命令的序列ID:对应LUT表格中的顺序 */

uint8_t ARDSeqIndex;

/* AHB读命令的数量 */

uint8_t ARDSeqNumber;

/* AHB写等待单位 */

flexspi_ahb_write_wait_unit_t AHBWriteWaitUnit;

/* AHB写等待间隔,乘以AHB写等待单位得到AHB写等待周期数,即写完后等待外部存储器处理完数据的时间 */

uint16_t AHBWriteWaitInterval;

/* 是否启用写入屏蔽。指示在向外部设备写入数据时是否将FLEXSPI的DQS引脚用作写入屏蔽 */

bool enableWriteMask;

} flexspi_device_config_t;

Nombre de commandes de lecture/écriture AHB ?

Prenons le nombre de commandes d'écriture AWRSeqNumbercomme exemple : pour certains périphériques de stockage (tels que HyperFlash/HyperRam/Serial NAND), l'accès à la programmation Flash est complété par plusieurs séquences de commandes, ce qui signifie que la commande d'écriture AHB déclenchera la première séquence de commandes dans le AWRSeqIndexLUT AWRSeqNumber.

3 Résumé

Cette section présente la composition de la table LUT et la signification de chaque paramètre de la structure de configuration FlexSPI.Avec ces connaissances de base, nous pouvons initialiser différents dispositifs de mémoire externe. La section suivante donnera un exemple pour voir comment ces paramètres sont initialisés à travers le schéma de principe de la connexion entre la mémoire externe et le FlexSPI et le manuel de synchronisation de la mémoire externe.