FPGA ISP Xilinx MIPI

Eu prefiro coisas Xilinx em casa, aqui para falar sobre Xilinx programa de casa MIPI. Aqui comuns 7 séries como objeto de discussão, casa X high-end KU + / MPSoC + tem sido apoiar diretamente a interface MIPI IO.

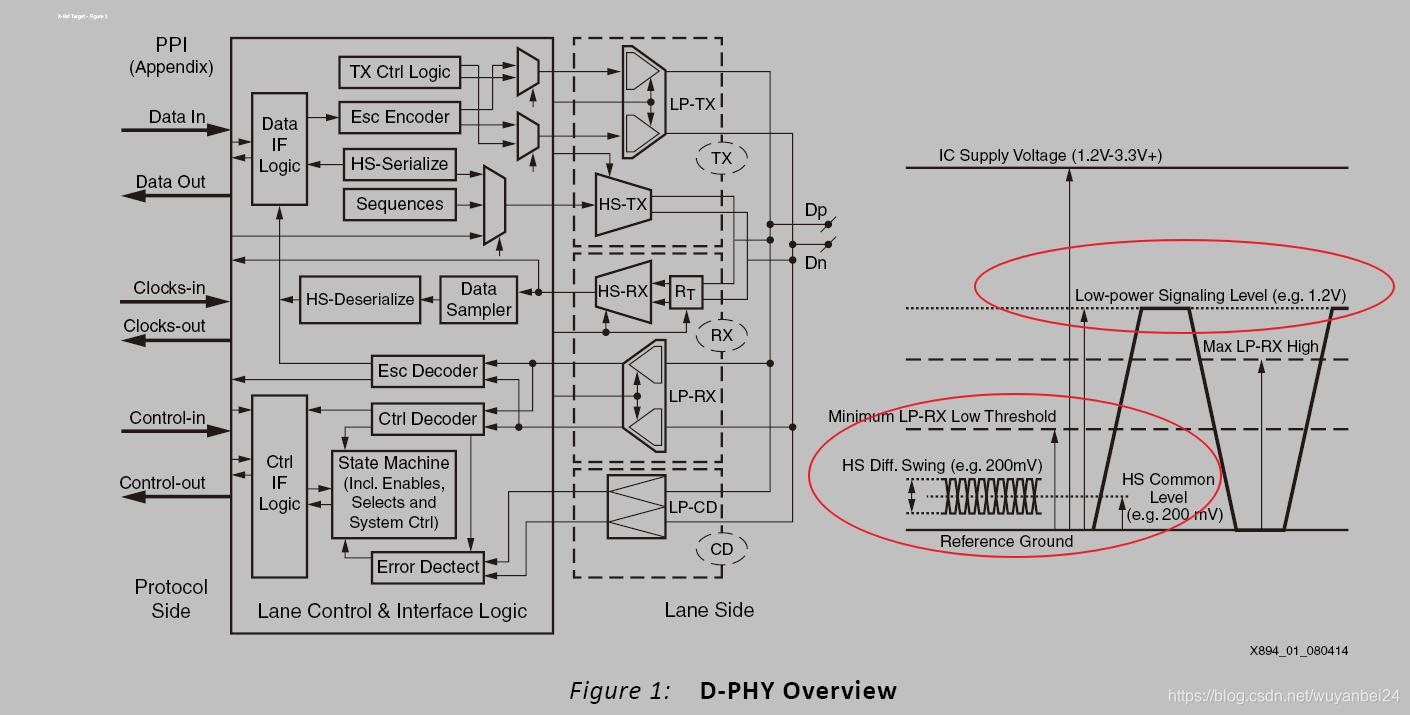

Por causa do sinal bastante especial MIPI, no início do projeto deve ter plenamente em conta o baixo consumo de energia, o nível do sinal de MIPI suporte nativo HS e LP modos de trabalho em diferentes níveis de critérios:

Pode ser claramente visto na figura, existem simultaneamente presentes o modo de dois níveis sinal elétrico MIPI, se forem recebidas nos pinos de FPGA, obviamente não pode ser suportado pelo FPGA.

Enquanto isso, o modo HS do nível FPGA padrão não é suportado. Portanto, dada a casa Xilinx dois tipos de programas, implementar conversão de nível de sinal MIPI, é descrito em detalhes neste XAPP894 documento, a parte seguinte é dada apenas MIPI DPHY Rx

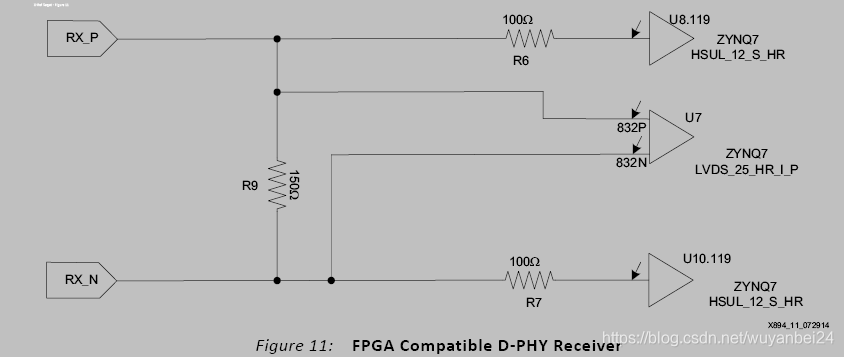

Uma rede resistor

Na maior MIPI velocidade da linha não é aconselhável usar este modo.

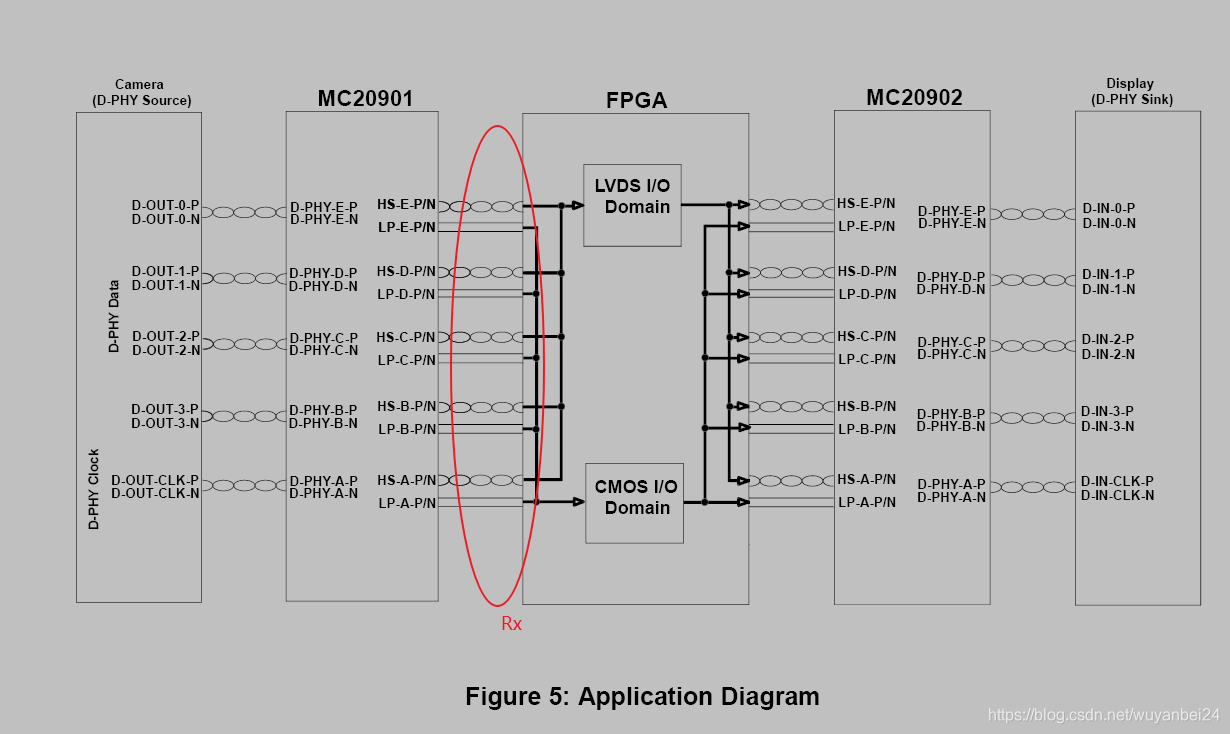

2 MC20901 chip externo

Ao receber uma câmera, só precisa usar o MC20901

Sobre o debug MIPI

MIPI depuração premissa é que você configuração do sensor corretamente completa é recomendada a partir da Internet ou FAE obter um conjunto de configuração tem sido comprovada para dirigir o sensor. O próximo foco deste depuração pode ser colocado MIPI parte. (Digamos Suplementar, biologia do ensino médio que mais me lembro é um conceito: fazer experimentos com controle variável, testes comparativos a fim de atender a descrição repetida de uma única variável, no entanto, solicitar mencionar o trabalho, muitas vezes fora de questão levantada é posicionado palpite)

Como os quatro Xilinx utilizado solução MIPI RX Subsystem IP, por isso alguns usuários podem configurar não é muito. Mas esta é, na verdade, dois internos configuração do subsistema IP, um MIPI-DPHY, MIPI-CSI2 é uma interface ainda mais, e em seguida, usando a interface do PPI entre duas redes IP.

MIPI DPHY por receber os dados de fluxo de bits, de acordo com o formato de quadro e, em seguida, recuperar o pacote. protocolo de pacotes para verificação ECC realizados, têm uma certa capacidade de identificar e corrigir erros. Mas se a qualidade do sinal não é bom, mais erros ocorrem, um erro é irrecuperável, a imagem é exibida nas ligações certas para a linha de horas mosca, e até mesmo vídeo.

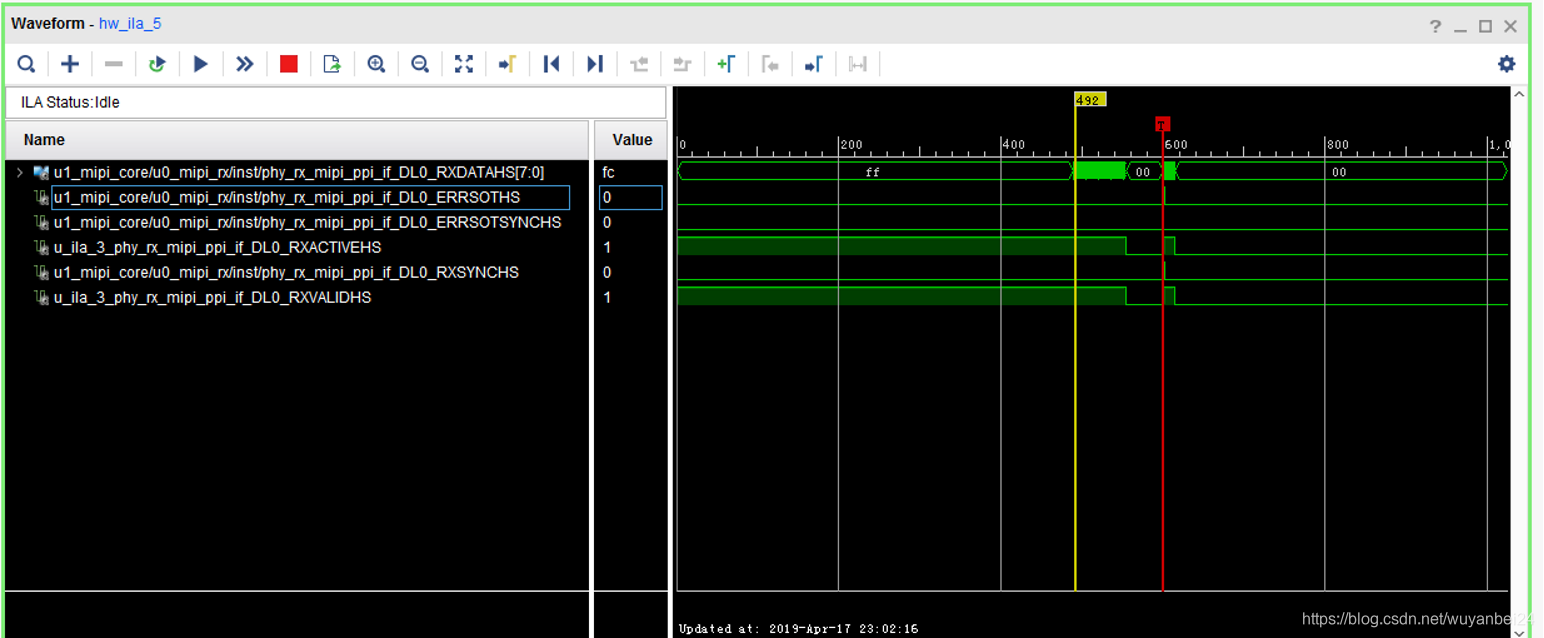

Após a conclusão de uma visão abrangente e integrada do princípio da aberto, entrar na parte MIPI DPHY, ser sinal de camada física mark_debug err sufixo, e depois salvos em um arquivo para depuração XDC mais tarde

Pode ser visto a partir da figura Xilinx de errorths de interface MIPI IP PPI sinal de alta, indicando a presença de perda de linhas, a situação ocorreu, se o sinal de erro de camada física constantemente, e então verificado o projeto FPGA si não é problema, é possível do lado do hardware considerar se há um problema.

Como um sinal de alta velocidade MIPI, infelizmente, osciloscópio de alta velocidade e sonda nem toda empresa tem a ...

Então, parafraseando a frase total de gengibre amada: hardware não é forte, a Terra estava se movendo ...