シミュレーション後に問題を解決する方法

ICCのレイアウトはPT、STA解析された後、彼らは[OK]を表示したときに、我々は最後のステップ---ポストシミュレーションで残っています。

何かがうまくいかないときの一般的な、基本的な無問題では、そう、私は無知です。マスターを離れる前に、私が行うことになって、このような状況が発生しないことがありますか?

まあ、私の探査の後、私が今知っている、ノートや知識の共有と、それを書き留めます。

エラーは違反が1つまたはいくつかのレジスタに集中発生した場合に、慌てる必要はありません

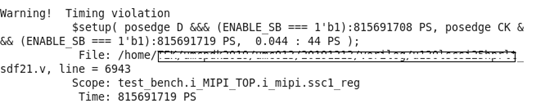

たとえば、次のコーナーへのTbの結果、

一般的に、次の図に与えられた報告された問題のうち:

マップ上の同様の違反によると、私たちは、その情報が、それができ得ることができますか?

- まず、セットアップ違反を参照してください

- 違反には時間が発生815xxxxxPSと81569xxxxPSです

- SETUP時間レジスタDは、エンド端子CKの問題発生を満たしていません

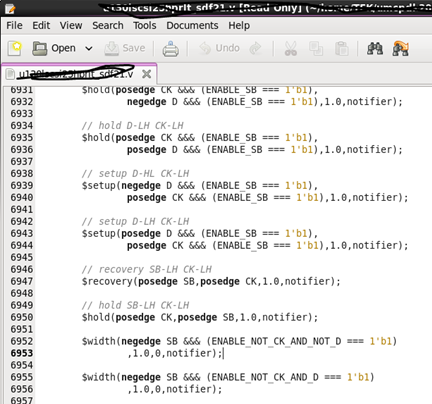

- 6943行verilog.v観察に対応するファイルを開く(以下コンテンツが、情報のない量は、このソースファイルに述べられていないことができます)

非常に重要なポイント:そこに問題があるとi_mipi / ssc1_regモジュール名を登録します

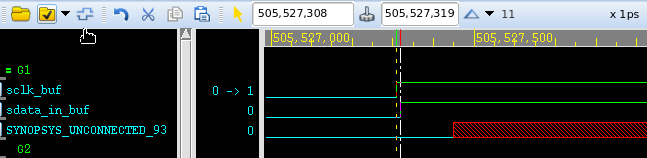

すべての情報についてlは、我々はドビュッシー&を開き、次のステップを解析しました。波形を表示します。

波形どのように問題のデバッグについて。以下は、独自の方法です。ギャングや善意の人々がより良いポインティングがそれを行使したいです。

- post_layout.vファイルのオープンicc_layoutとssc1_reg(すなわち、壊れたレジスタ名)を見つけます。我々は、デバイスの使用がDFSM2で見ることができます。nWaveビューに対応する追加の相関信号、すなわちSYNOPSYS _ ** 93、sdata_buf、sclk_buf。

2.観測時間クロックCKと差のD入力端子。のみ11PS

3.方法1:

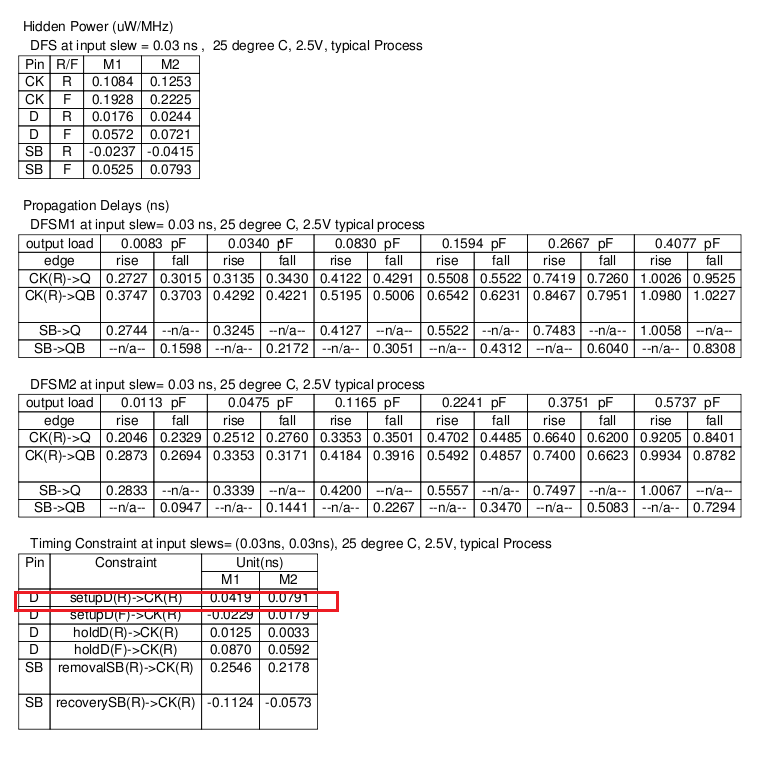

a)は、デバイスのマニュアルデータブックで見つけDFM2上Foundryのstdcell命令を提供し、私は時間がCKにDの0.0791nsを必要と赤い部分ショーをしたいです。(モジュール内で自分自身を見つけるために、ニーズを立ち上がりまたは立ち下がりするように)。セットアップ時間を増やすためにBUFを追加するために必要と判断されます

継続するには