新しい STM32 学習 25 - USART レジスタの概要

STM32–USART レジスタ導入 (F1)

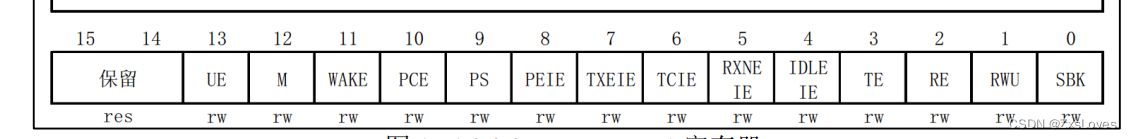

制御レジスタ 1 (CR1)

ビット 13: USART UE を有効にする

0: USART 分周器と出力は無効

1: USART モジュールは有効

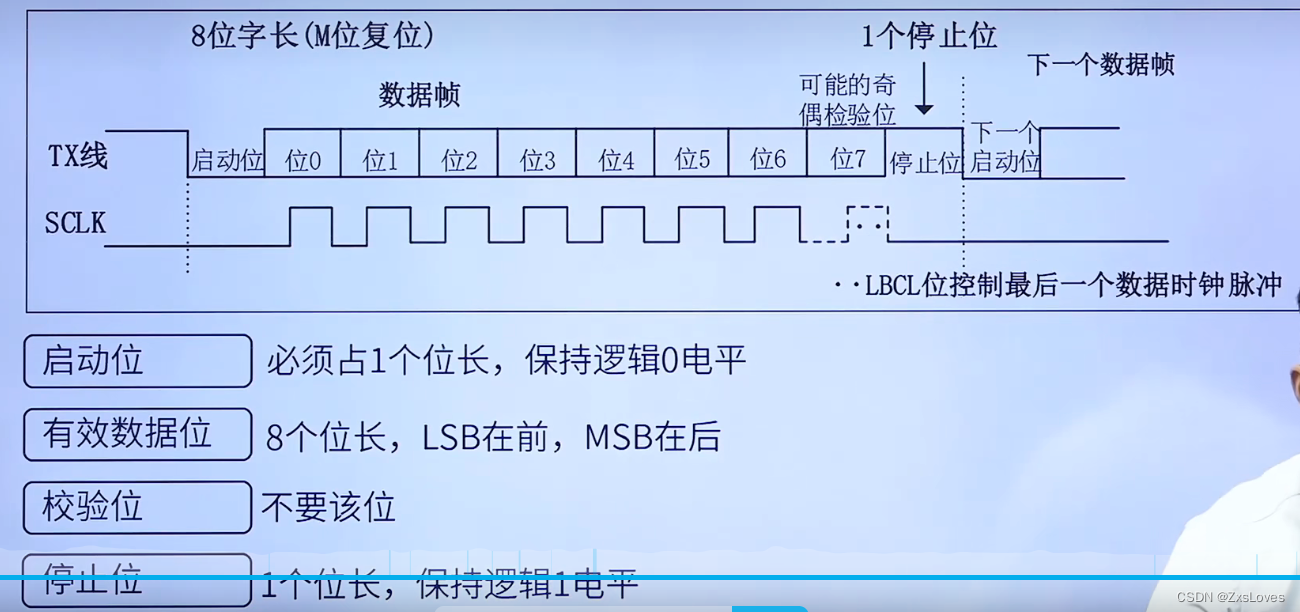

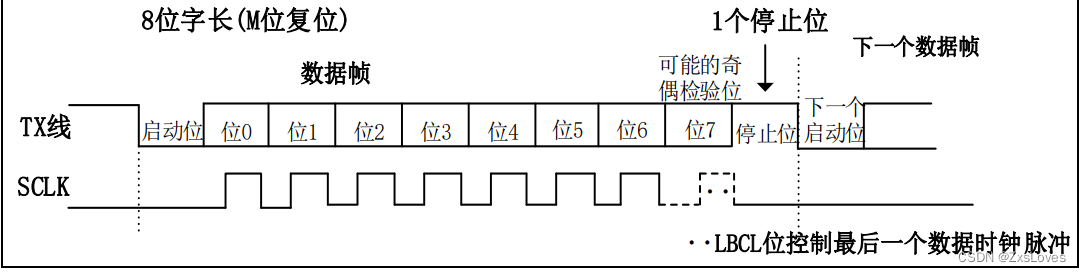

ビット 12: 8 データ ビット M を設定します。

このビットはデータ ワードの長さを定義し、ソフトウェアによって設定およびクリアされます。

0: スタート ビット、8 データ ビット、n ストップ ビット

1: 1 スタート ビット、9 データ ビット、n ストップ ビット。

一般的に、有効データビットには 8 ビットが使用されます。

ビット 10: チェック制御 PCE を無効にする

0: 検証制御を無効にする

1: 検証制御を有効にする

ビット 5: RXNEIE は受信バッファが空でない割り込みを有効にします

0: 割り込み発生禁止

1: USART_SR の ORE または RXNE が 1 のとき、USART 割り込みを発生

ビット 3: TE は送信を有効にする

0: 送信を無効にする

1: 送信を有効にする

ビット 2: 受信を有効にする

0: 受信を無効にする

1: 受信を有効にし、RX ピンのスタート ビットの検索を開始する

UE はシリアルポートイネーブルビットで、このビットを 1 にセットするとシリアルポートが有効になります。

M はワード長です。このビットが 0 の場合、シリアル ポートを 8 ワード長と n ストップ ビットに設定します。ストップ ビットの数 (n) は、USART_CR2 の [13:12] ビット設定に従って決定されます。デフォルトはは0です。

PCE

は検証イネーブル ビットで、0 に設定すると検証が無効になり、それ以外の場合は有効になります。

PS はパリティ ビットの選択で、偶数パリティの場合は 0 に設定され、

それ以外の場合は奇数パリティです。TXIE は送信バッファエンプティ割り込み許可ビットで、このビットを 1 に設定すると、USART_SR の TXE ビットが 1 のとき

、シリアルポート割り込みが発生します。TCIE は送信完了割り込み許可ビットで、このビットを 1 に設定するとUSART_SR のTC

ビットが 1 のときシリアルポート割り込みが発生します。RXNEIE は受信バッファ非空割り込みイネーブルです。このビットを 1 に設定します。USART_SR

の ORE または RXNE ビットが 1 の場合、シリアル ポート割り込みが生成されます。TE は送信許可ビットで、1 に設定すると

シリアルポートの送信機能が有効になります。RE は受信イネーブルビットで、使い方は TE と同じです。、

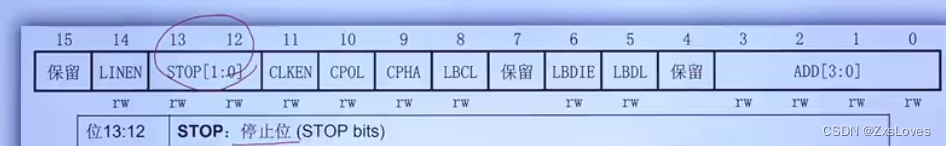

別の制御レジスタ 2 CR2 では、

ビット 13 と 12 のみを使用します

ビット 13: 12 は

STOP ストップ ビットです

これら 2 つのビットを使用してストップ ビットの数を設定します

00: 1 ストップ ビット

01: 0.5 ストップ ビット

10: 2 ストップ ビット

11: 1.5 ストップ ビット

このレジスタが完了する必要がある設定は次のとおりです。 1 ストップ ビットの設定

注: UART4 および UART5 は 0.5 ストップ ビットと 1.5 ストップ ビットを使用できません。

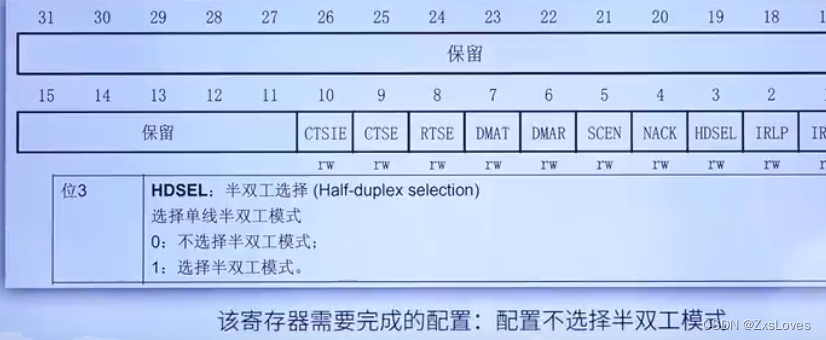

制御レジスタ CR3

はそのビット 3 のみを使用します

HDSEL 構成の半二重選択を選択します

0: 半二重モードを選択しません

1: 半二重モードを選択します

ここには 9 ビットがあります

。CR1 が次のように示す場合、上記の CR1 の配置に従います。 8 次に、[7;0] を使用します。

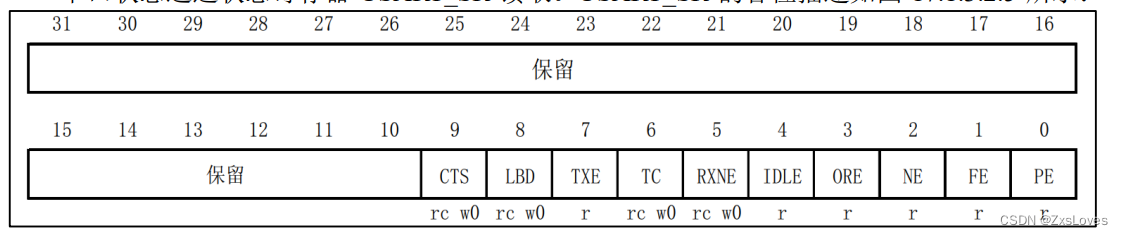

ステータス レジスタ SR

ビット 5: RXNE (読み取りデータ レジスタが空ではない)

このビットが 1 に設定されている場合、データが受信され、読み出すことができることを示します。このとき、できるだけ早く USART_DR を読み出す必要があり、USART_DR を読み出すことでこのビットをクリアしたり、このビットに 0 を書き込んで直接クリアしたりすることができます。

平たく言えば、このビットが 1 の場合は、読み出しデータ レジスタが空ではない、つまり DR 上に何かがあり、すぐに読み出すことができることを意味します 0: データが受信されていない

1

:データは受信されており、読み出すことができます。

ビット 6: TC (送信完了)

このビットがセットされると、USART_DR 内のデータが送信されたことを示します。このビットの割り込みが設定されている場合、割り込みが生成されます。このビットをクリアするには 2 つの方法もあります。1

) USART_SR を読み出し、USART_DR に書き込む。

2) このビットに直接 0 を書き込む

0: 送信がまだ完了していない

1: 送信が完了している

TC ビットによりデータの送信が可能かどうかがわかり、

RXNE ビットによりデータの受信ができたかどうかがわかります。