1.ソフトウェア設定インターフェース

FIFO (First In First Out) は、データを先入れ先出しで読み書きするために使用されるデータ バッファです。ROM や RAM のアドレスベースの読み書き方法とは異なり、FIFO の読み書きは「先入れ先出し」の原則に従います。つまり、データは FIFO に順番に書き込まれ、最初に書き込まれたデータが順番に書き込まれます。読み出し時にも最初に読み出されるため、FIFO メモリにはアドレス ラインがありません。FIFO には書き込みポートと読み取りポートがあり、ユーザーが外部からアドレスを制御する必要がないため、使いやすいです。

FIFO メモリは主にキャッシュとして使用され、同期クロック システムと非同期クロック システムで使用され、次のような多くの設計で使用されます: マルチビット データはクロス クロック ドメイン変換に使用され、フロントおよびリアの帯域幅は非同期FIFOを使用しており、概略図は以下の通りです。FIFO は、読み取りと書き込みのクロックが同じかどうかにより、SCFIFO (同期 FIFO) と DCFIFO (非同期 FIFO) に分けられます。SCFIFO は同じクロックで読み取りと書き込みを行い、同期クロック システムに適用されます。DCFIFO は読み取りと書き込みが異なります。クロックであり、非同期クロック システムに適用されます。

Yilinx fpga の FIFO を使用する際に特に注意する点はなく、ビジュアルインターフェイスでもありますので、インターフェイスの定義に従って通常通り設定して FIFO を生成することができます。

FIFO 生成の手順については、以下で詳しく説明します。

任意のプロジェクトを開き、IPM メニュー バーで [FIFO IP] をダブルクリックします。

IP を生成するには、モジュール名で IP に名前を付け、

必要に応じて構成インターフェイスでいくつかの指示信号を有効にする必要があります。

右下隅の「生成」をクリックして生成します。

二。

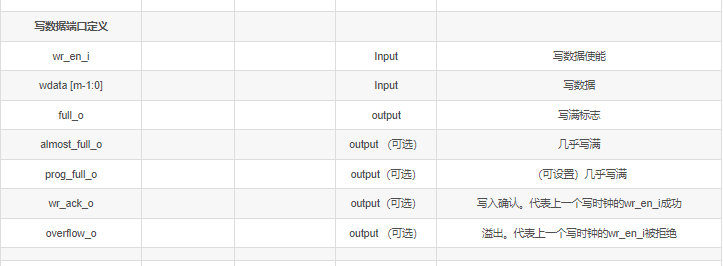

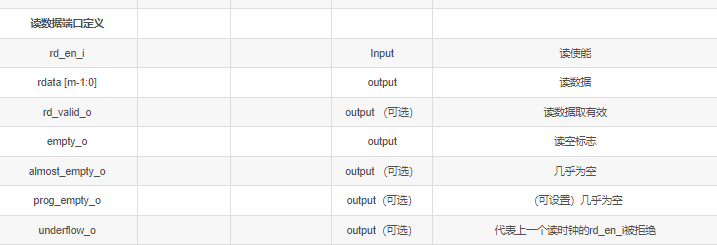

FIFOポート定義

三つ。

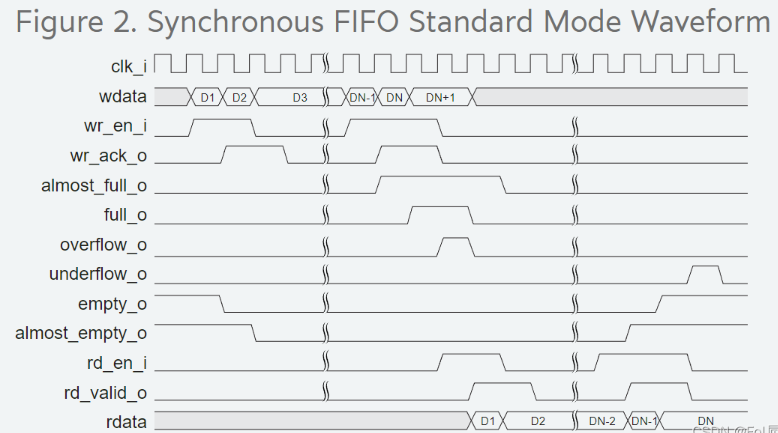

FIFO タイミング

同期FIFO標準モード

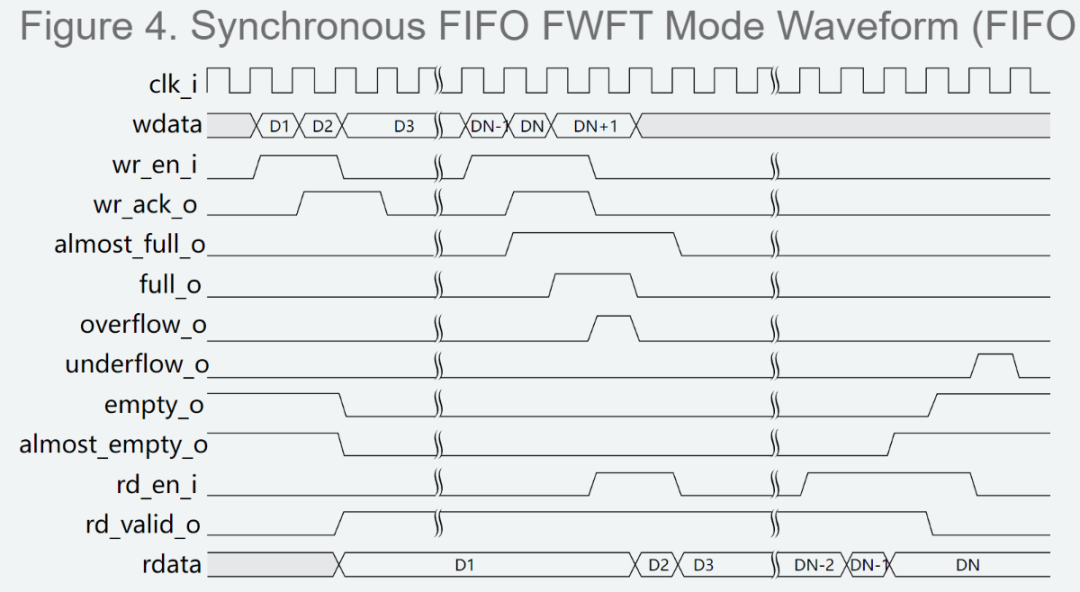

同期FIFO FWFTモード

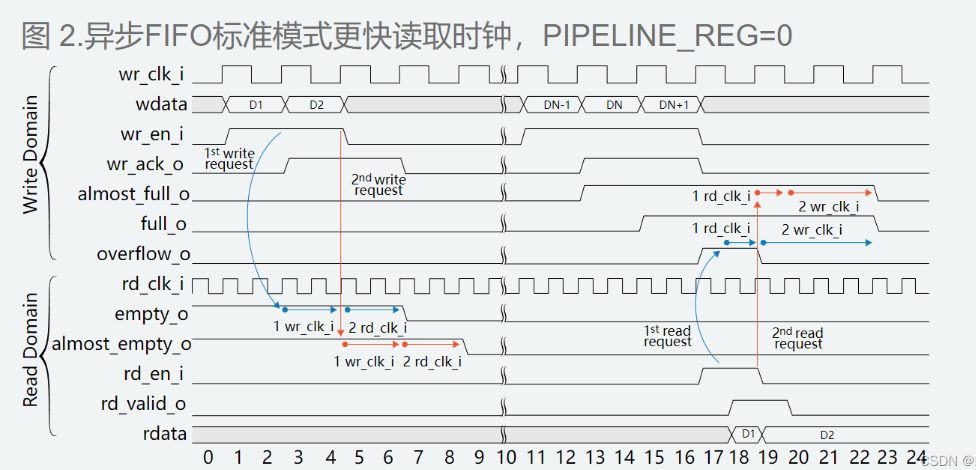

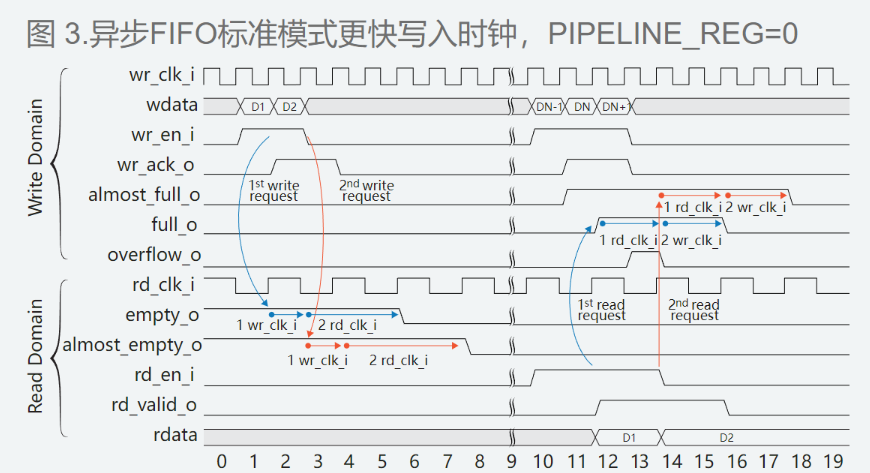

非同期FIFO標準モード

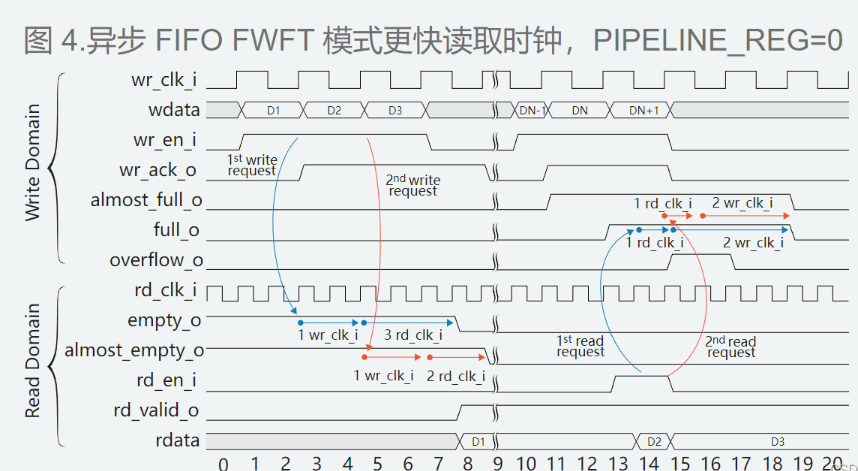

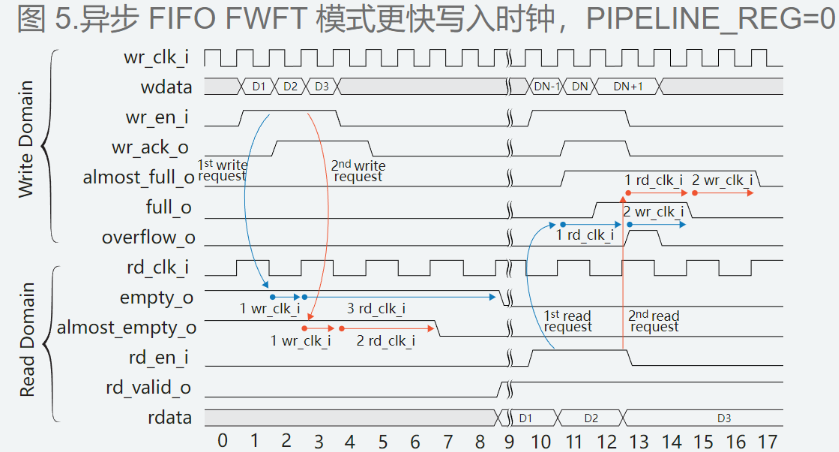

非同期FIFO FWFTモード

Yilinx FPGA のアプリケーションの詳細については、以下のリンクを参照してください。

Yilinsi FPGA --- ローカリゼーションの代替選択戦略