Chapitre deux

80386 système d'adressage

-

Cas sans pagination

Etapes de calcul : obtenir d'abord le sélecteur de segment du programme, trouver l' adresse de base du segment (32 bits) en fonction du contenu du sélecteur de segment, puis obtenir l'adresse de décalage utilisée par l'instruction courante.

Adresse linéaire 32 bits = adresse de base du segment (32 bits) + décalage intra-segment (16 bits) + décalage logique (32 bits)

En l'absence de radiomessagerie, une adresse linéaire n'est qu'une adresse physique.

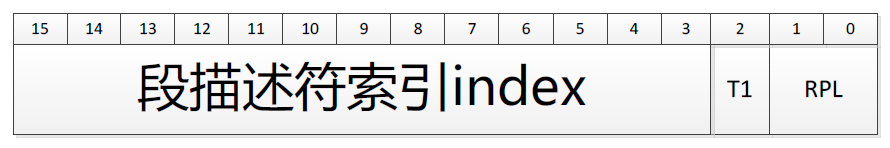

Les 13 bits supérieurs sont l'index du descripteur, et trois 0 sont ajoutés à la fin pour indiquer le décalage du descripteur de segment par rapport à l'adresse de base (équivalent aux treize premiers bits multipliés par 8H et décalés vers la gauche de trois bits, et les trois derniers bits sont mis à zéro dans leur ensemble)

Le bit 2 est le bit indicateur de la table des descripteurs de référence

TI=0: Lit les descripteurs de la table de descripteurs globale GDTTI=1: Lire le descripteur de la table de descripteurs locaux LDT

Les bits 1 et 0 sont le niveau de privilège de la demande RPL

-

例:L'adresse de base de LDT est00120000H, l'adresse de base de GDT est0010 0000H,CS=1007Het trouvez l'adresse du descripteur de segment解:CS = 0001 0000 0000 0111BIl y a donc

TI=1,RPL=11B=3etOFFSET(偏移地址) = 0001 0000 0000 0000H = 1000HAlors l'adresse du descripteur de segment est

0012 0000H + 1000H = 0012 1000H -

例: L'adresse de base de LDT est0060 2000H, l'adresse de base de GDT est0050 1000H,CS=2006H,EIP=0200Htrouver l'adresse linéaire du segment de code en mémoire.解:Le titreEIPfait référence à l'adresse offsetCalculez donc d'abord l'adresse du descripteur de segment,

CS = 0010 0000 0000 0110Bc'est-à-direTI=1,RPL=10B=2ont aussi

LD = 2000H + 0060 2000H = 0060 4000Hdonc

线性地址 = LD + EIP = 0200H + 0060 4000H = 0060 4200H -

Il y a un cas de pagination

Répondez au processus spécifique de traduction d'adresse logique en adresse physique dans le système de processeur 80386.

1. La CPU obtient d'abord le sélecteur de segment et l'adresse de décalage dans le segment à partir de l'instruction d'accès à la mémoire

2. Interrogez le descripteur de segment correspondant dans la table des segments (GDT ou LDT) en fonction du sélecteur de segment

3. Générer une adresse linéaire 32 bits (adresse virtuelle sous le mécanisme de page) basée sur l'adresse de base du segment dans le descripteur de segment et l'adresse de décalage du segment dans l'instruction

4. L'adresse linéaire 32 bits est divisée en trois parties selon la conception de la table de pages secondaire 80386 : les 10 bits supérieurs sont utilisés comme index d'entrée de répertoire de page, les 10 bits les plus élevés au milieu sont utilisés comme page index d'entrée de table et les 12 bits inférieurs sont utilisés comme adresse de décalage de page.

5. Obtenez l'adresse de page physique de la table de pages de deuxième niveau à partir de la table de répertoires de pages de premier niveau via l'index d'entrée de répertoire de pages 10 bits élevé (obtenable via le numéro de cadre de page physique), puis recherchez l'entrée de table de pages correspondante. index en fonction de l'index d'entrée de table de page 10 bits du milieu Cadre de page physique. Selon le numéro de cadre de page physique et l'adresse de décalage dans la page, l'adresse physique finale est générée conjointement pour accéder à la mémoire physique.

Améliorations de l'architecture du microprocesseur

-

Superposition de sous-systèmes de stockage

L'enjeu clé est le suivant : pour construire un système de stockage qui réponde aux exigences de capacité et de rapidité à un prix raisonnable, il est fondamentalement nécessaire de coordonner la contradiction entre rapidité, capacité et coût

-

Structure secondaire : mémoire (pour résoudre la vitesse de lecture et d'écriture) + mémoire externe (pour résoudre la capacité de stockage)

-

Structure à quatre niveaux : registre + cache + mémoire principale (adressage des octets) + stockage auxiliaire

La structure de mémoire cache-principale résout la contradiction entre haute vitesse et faible coût

La structure de la mémoire principale et de la mémoire auxiliaire utilise la mémoire virtuelle pour résoudre la contradiction entre grande capacité et faible coût

-

Pipeline : Il divise le processus de traitement des instructions informatiques en plusieurs étapes et exécute les instructions en parallèle via plusieurs unités de traitement matérielles pour accélérer l'exécution des instructions.

-

Superscalaire : Un processeur avec une architecture superscalaire peut envoyer simultanément plusieurs instructions à exécuter dans différentes unités d'exécution en un cycle d'horloge, ce qui réalise le parallélisme du jeu d'instructions.

-

Problèmes de pipeline : ce n'est qu'à pleine charge que la meilleure efficacité peut être exercée ; le nombre d'étages de pipeline ne peut pas être augmenté indéfiniment ; les coûts de matériel seront augmentés ; des retards et des frais généraux supplémentaires seront introduits, limitant la profondeur du pipeline ; Pipeline interrompu.

mode d'adressage

-

Adressage immédiat : les opérandes font partie de l'instruction

MOV AX,1234H ;小端序:高位:12->AH 低位:34->AL -

Adressage direct : L'opérande requis par l'instruction est stocké dans la mémoire, et l'adresse effective de l'opérande est directement donnée dans l'instruction.

MOV AX,[1234H] ;MOV 不能直接进行两地址之间的内存交换 -

Adressage de registre : l'opérande est stocké dans le registre et les données sont obtenues en spécifiant le registre

MOV AX,BX -

Registre d'adressage indirect : l'adresse effective de l'opérande n'est que dans un des quatre registres

SI,DI,BX,BPMOV AX,[DI] ;[]取内存单元 -

Adressage relatif au registre : l'adresse effective de l'opérande est la somme de la valeur d'un registre de base ( ,

BX)BPou d'un registre d'index (SI,DI) plus le décalage de 8 ou 16 bits donné dans l'instructionMOV AX, [BX + 1234H] ;或者 MOV 1234H[BX] -

Adressage indexé de base : L'adresse effective de l'opérande est obtenue en ajoutant la valeur d'un des registres de base (

BX,BP) à la valeur d'un des registres d'index (SI, )DIMOV AX, [BX + DI] ;MOV AX, [BX][SI] -

Adressage indexé relatif à la base : ajoute un décalage par rapport à l'adressage indexé à la base

MOV AX, 1234H[BX + DI]

exercer

-

Le 8086CPU divise l'espace de 1 Mo en plusieurs segments logiques, et chaque segment peut contenir jusqu'à 64 Ko d'unités de stockage.

-

L'espace d'E/S adressable maximal du 8086CPU est de 64 Ko

-

L'espace d'adressage de la mémoire interne dans le système 8086 est de 1 Mo, et lors de la lecture et de l'écriture d'E/S, la ligne d'adresse effective est constituée des 16 bits inférieurs .

-

Si la fréquence principale du 8086CPU est de 8 MHz, son cycle de bus de base est de 500 ns

-

L'adresse d'octet virtuel 7FFFH-8000H peut ne pas être continue dans l'espace d'adressage physique

-

? 8086 a 2 broches d'interruption matérielle CPU , INTR/NMI est un signal d'interruption masquable et le signal d'interruption non masquable INTA est une réponse d'interruption

-

Le processeur 8086 lit/écrit la mémoire, et l'opération qui nécessite deux cycles de bus consiste à lire/écrire un mot à partir d'une adresse impaire (ligne de données 16 bits, lire à partir d'une adresse impaire n'est pas la façon de le faire)

-

Dans les méthodes de gestion de segmentation et de pagination de la mémoire informatique, les segments peuvent se chevaucher et les pages ne peuvent pas se chevaucher

-

La classe de file d'attente d'instructions dans le processeur 8086 peut stocker 6 octets de codes d'instruction

-

Dans le procédé de gestion de pagination de stockage, le but de la construction d'une table de pages à plusieurs niveaux est de réduire le nombre d'entrées de table de pages

L'utilisation de tables de pages à plusieurs niveaux peut économiser la mémoire de la table de pages. L'utilisation d'une table de pages de premier niveau nécessite un espace mémoire continu pour stocker toutes les entrées de la table de pages. Les tables de pages à plusieurs niveaux réduisent l'utilisation de la mémoire en demandant des tables de pages uniquement pour les régions de mémoire des adresses virtuelles réellement utilisées par le processus

-

8086 et 80386 ont des files d'attente de flux d'instructions à l'intérieur

-

En mode protégé, le registre de segment du processeur Pentium est utilisé pour sélectionner le descripteur de segment

-

Lorsque le signal 8086 broches M/IO=1, RD=0, WR=1, l'opération effectuée par le CPU est la lecture de la mémoire (la lecture et l'écriture sont actives au niveau bas, M signifie mémoire)

-

Dans le système 8086, un cycle de bus complète une lecture et une écriture de la mémoire

-

Fonctionnement du processeur pipeline en quatre étapes : récupération, décodage, exécution, réécriture

-

Le processeur 16 bits 8086 lit et écrit des données continues sur deux octets, et le nombre de cycles de bus peut être de un ou deux (lorsqu'il est aligné, un cycle ; lorsqu'il n'est pas aligné, deux cycles)

-

Lorsque le CPU appelle un sous-programme, l'adresse de retour est poussée sur la pile

-

Les processeurs d' Intel X86 et d'AMD ont une compatibilité de jeu d'instructions, et le jeu d'instructions est le même.

-

Les programmes conçus pour le mode de protection X86 ne peuvent pas s'exécuter dans le 8086 car les modes d'adressage ne sont pas compatibles

-

La différence essentielle entre le mode réel et le mode de protection des processeurs Intel réside dans les différents mécanismes de gestion des tâches

-

Lorsque le CPU appelle un sous-programme, l'adresse de retour est poussée sur la pile

-

Les processeurs d' Intel X86 et d'AMD ont une compatibilité de jeu d'instructions, et le jeu d'instructions est le même.

-

Les programmes conçus pour le mode de protection X86 ne peuvent pas s'exécuter dans le 8086 car les modes d'adressage ne sont pas compatibles

-

La différence essentielle entre le mode réel et le mode de protection des processeurs Intel réside dans les différents mécanismes de gestion des tâches