Vivado IP core proporciona un potente generador FIFO que puede generar rápidamente un núcleo FIFO IP a través de una configuración gráfica.

Este artículo presentará en detalle cómo configurar un núcleo IP FIFO en Vivado y cómo llamar a este núcleo IP FIFO.

1. Configuración del núcleo IP FIFO

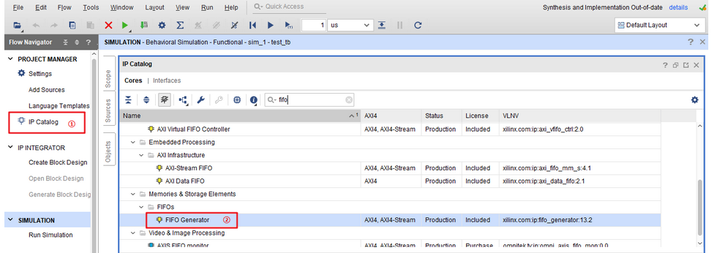

1. Cree una nueva IP FIFO

Busque el núcleo IP del generador FIFO en el catálogo de IP de Vivado y haga doble clic para abrir la interfaz de configuración de parámetros.

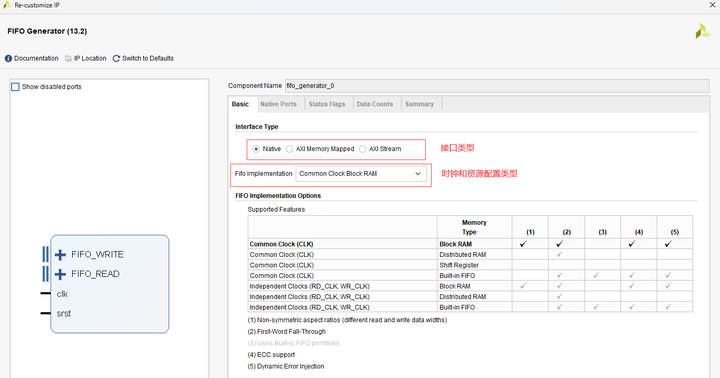

2. Configurar los parámetros básicos de FIFO

(1) Tipo de interfaz

FIFO de interfaz nativa:

Esta es la interfaz FIFO más básica, que incluye entrada de datos, puerto de salida, habilitación de escritura, habilitación de lectura y otras señales.

FIFO de interfaz asignada de memoria AXI:

Esta interfaz encapsula el FIFO en un núcleo IP mapeado en memoria AXI al que se puede acceder a través del bus AXI.

FIFO de interfaz AXI4-Stream:

Esta interfaz es compatible con el protocolo AXI4-Stream y es adecuada para su uso en escenarios de transmisión de datos en streaming.

(2) Tipo de reloj y tipo de recurso

Reloj: reloj síncrono (reloj común) y reloj asíncrono (reloj independiente)

Funciones: bloquear RAM, RAM distribuida, registro de desplazamiento, FIFO integrado

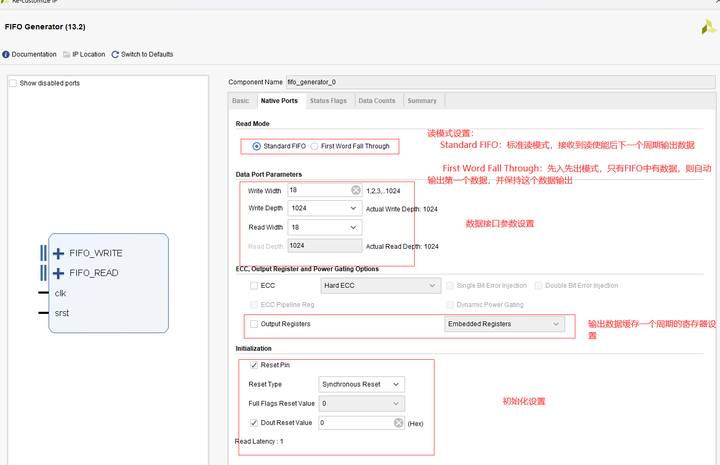

3. Configurar los parámetros de la interfaz quince

(1) Configuración del modo de lectura

FIFO estándar: modo de lectura estándar, datos de salida en el siguiente ciclo después de recibir la habilitación de lectura

Fallo de primera palabra: modo primero en entrar, primero en salir. Mientras haya datos en el FIFO, los primeros datos se generarán automáticamente y esta salida de datos se mantendrá.

(2) Configuración de parámetros de la interfaz de datos

El ancho y la profundidad de bits de la interfaz de lectura de datos FIFO, el ancho y la profundidad de bits de la interfaz de datos de escritura FIFO

(3) Configuración del registro de salida y ECC

(4) Configuración de inicialización

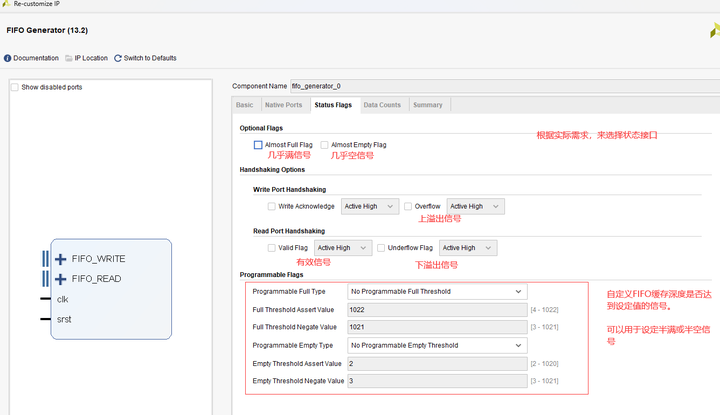

4. Configuración de la interfaz de señal de estado

Según las necesidades reales, simplemente seleccione la señal de estado correspondiente.

Nota (banderas programables): personalice la señal de si la profundidad del búfer FIFO alcanza el valor establecido. Se puede usar para configurar la señal medio llena o medio vacía.

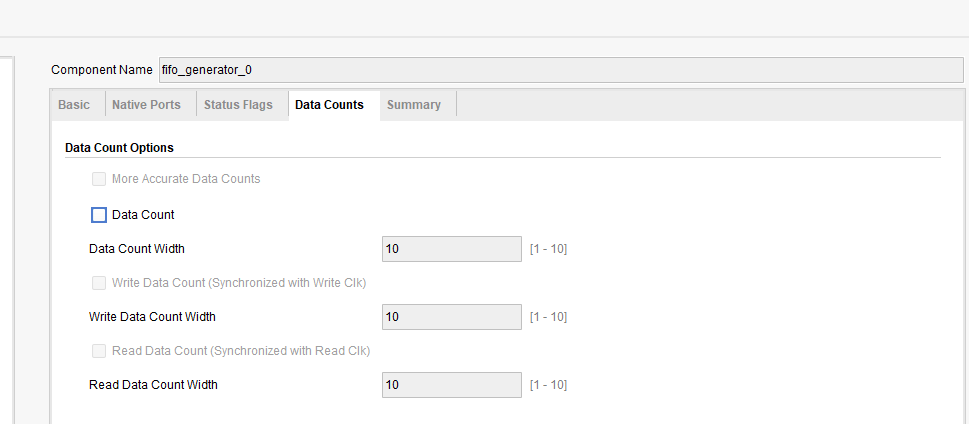

5. Contando la configuración del puerto

El recuento de profundidad de datos de la caché quince, opcional.

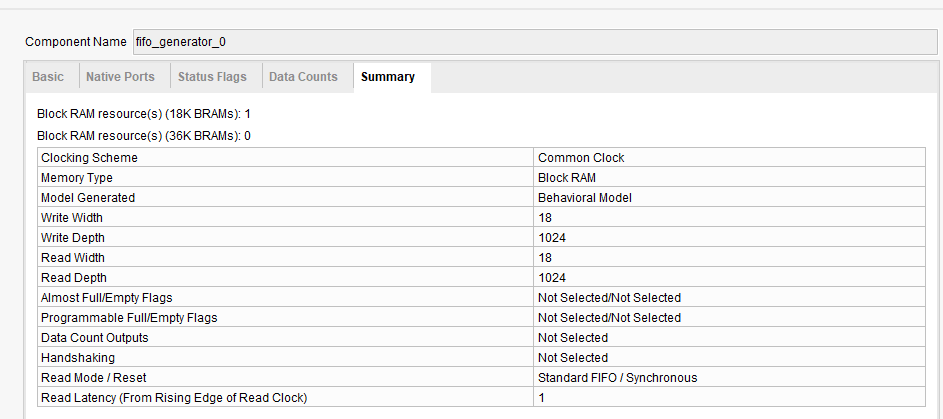

6. Descripción general de los parámetros de configuración FIFO

Esta es una descripción general de los parámetros de configuración de FIFO IP. Puede ver el consumo de recursos, el ancho, la profundidad, la latencia de lectura y otra información.

7. Haga clic en Aceptar para generar el núcleo IP FIFO.

2. Interfaz del núcleo IP FIFO

El núcleo IP FIFO generado proporciona las siguientes interfaces:

wr_clk escribir reloj

rd_clk leer reloj

puerto de entrada de datos din, el ancho es el ancho de datos configurado;

wr_en señal de habilitación de escritura;

rd_en señal de habilitación de lectura;

puerto de salida de datos;

bandera llena, el nivel alto indica que el FIFO está lleno;

bandera vacía vacía, el nivel alto indica que el FIFO está vacío;

casi_full bandera casi llena;

casi_empty bandera casi vacía;

bandera de datos válida válida

rd_data_count recuento de lecturas

wr_data_count recuento de escrituras

desbordamiento escribe marca de desbordamiento

el desbordamiento inferior lee la marca de desbordamiento

3. Llamada del núcleo IP FIFO

La llamada al núcleo IP FIFO es muy simple: solo necesita conectar la interfaz adecuadamente y controlar las señales de habilitación de lectura y escritura de acuerdo con los indicadores Lleno y Vacío. A continuación se proporciona un ejemplo de llamada simple:

module fifo_test(

input clk,

input [17:0] din,

input wr_en, rd_en,

output valid,

output [17:0] dout,

output full, empty, overflow, underflow

);

fifo_generator_0 fifo_inst(

.clk(clk),

.din(din),

.wr_en(wr_en),

.rd_en(rd_en),

.dout(dout),

.full(full),

.empty(empty),

.overflow(overflow),

.valid(valid),

.underflow(underflow)

);

endmodule

En este ejemplo, din y wr_en están conectados a los puertos de entrada del FIFO, y dout y vacío están conectados a los puertos de salida. Es necesario verificar la señal completa al escribir datos y la señal vacía al leer datos para evitar desbordamientos y subdesbordamientos.

El siguiente es un banco de pruebas simple del núcleo IP FIFO:

`timescale 1ns / 1ps

module fifo_testbench();

reg clk;

reg [17:0] din;

reg wr_en;

reg rd_en;

wire valid;

wire [17:0] dout;

wire full, empty, overflow, underflow;

fifo_test dut(

.clk(clk),

.din(din),

.wr_en(wr_en),

.rd_en(rd_en),

.dout(dout),

.full(full),

.empty(empty),

.overflow(overflow),

.valid(valid),

.underflow(underflow)

);

always #5 clk = ~clk;

initial begin

clk = 0;

wr_en = 0; rd_en = 0;

#10;

wr_en = 1; din = 18'd1;

#10;

wr_en = 1; din = 18'd2;

#10;

wr_en = 1; din = 18'd3;

#10;

wr_en = 0; rd_en = 1;

#10;

wr_en = 0; rd_en = 1;

#10;

wr_en = 1; din = 18'd4;

wr_en = 1; din = 18'd5;

#10;

wr_en = 0; rd_en = 1;

#10

wr_en = 0; rd_en = 1;

#10;

$finish;

end

endmodule

Este banco de pruebas prueba las funciones de escritura y lectura del FIFO aplicando diferentes señales de habilitación de lectura y escritura.

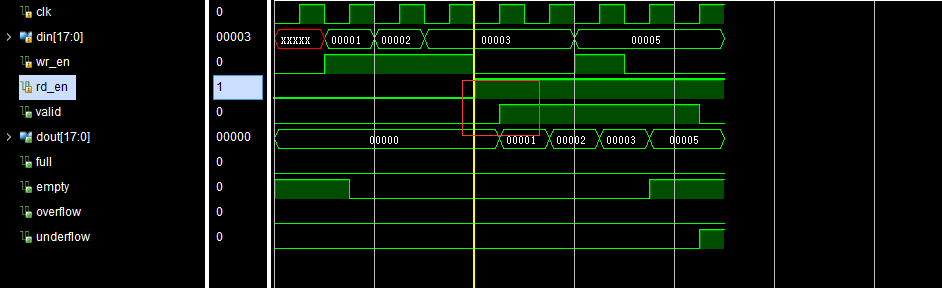

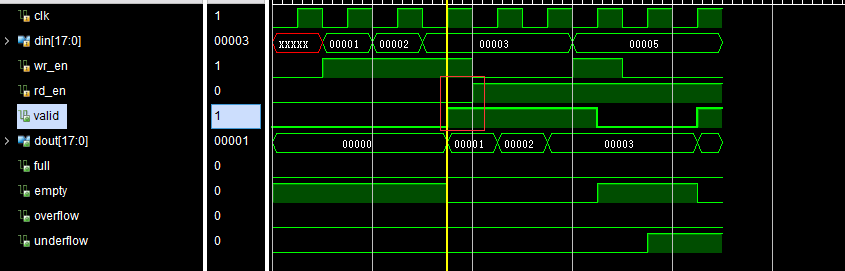

Gráfico de prueba de simulación:

(1) El modo de lectura FIFO está configurado en "FIFO estándar"

La señal válida está completamente controlada por rd_en.

(2) El modo de lectura FIFO está configurado en "Primera palabra fallida"

Después de almacenar en caché una cierta longitud de datos, los primeros datos se leen automáticamente y se retienen hasta que llega la siguiente señal rd_en.

4. Resumen

A través de la descripción anterior, hemos introducido en detalle cómo configurar el núcleo IP FIFO en Vivado, las señales de interfaz de FIFO y un ejemplo simple de cómo llamar al núcleo IP FIFO. FIFO es un núcleo IP muy utilizado. El generador FIFO de Vivado puede simplificar enormemente el proceso de configuración y uso de FIFO.

Manual oficial de Xilinx:

Portal de documentación de computación adaptativa de AMD

Este artículo se actualizará periódicamente, las palabras clave no son fáciles, haga clic en ⭐️ Me gusta, recopile ⭐️ y escóndalo, no se pierda.

Este artículo fue creado originalmente por FPGA Hurricane, si tienes alguna pregunta, puedes comunicarte conmigo en el área de comentarios.

Obtenga materiales de aprendizaje gratuitos, código fuente abierto de github: " Base de conocimientos FPGA "

¡Tu apoyo es mi mayor motivación para seguir creando! Si este artículo te resultó útil, dale una palmadita en la espalda, gracias.