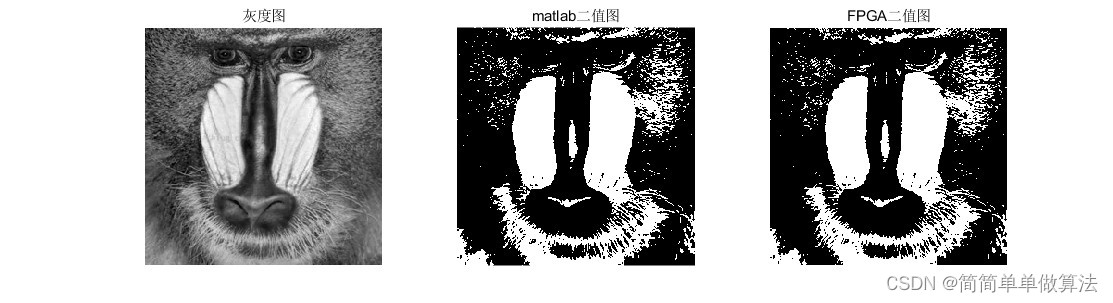

1. 알고리즘 연산 렌더링 미리보기

디스플레이를 위해 FPGA 데이터를 MATLAB으로 가져오기

2. 알고리즘 실행 소프트웨어 버전

비바도2019.2

matlab2022a

3. 일부 핵심 프로그램

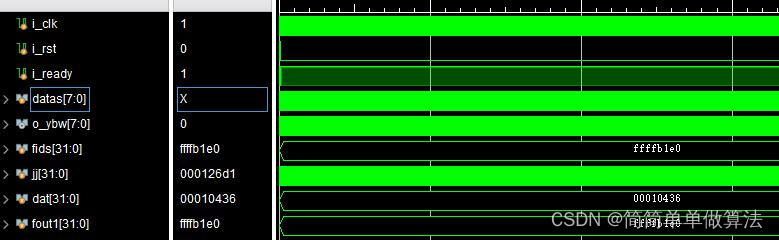

`timescale 1ns / 1ps

.............................................................................

module test_image;

reg i_clk;

reg i_rst;

reg i_ready;

reg [7:0] Tmp[0:100000];

reg [7:0] datas;

wire [7:0] o_ybw;

integer fids,jj=0,dat;

//D:\FPGA_Proj\FPGAtest\code2

initial

begin

fids = $fopen("D:\\FPGA_Proj\\FPGAtest\\code2\\data.bmp","rb");

dat = $fread(Tmp,fids);

$fclose(fids);

end

initial

begin

i_clk=1;

i_rst=1;

i_ready=0;

#1000;

i_ready=1;

i_rst=0;

end

always #5 i_clk=~i_clk;

always@(posedge i_clk)

begin

datas<=Tmp[jj];

jj<=jj+1;

end

im2bw im2bw_u(

.i_clk (i_clk),

.i_rst (i_rst),

.i_ready (i_ready),

.i_xin (datas),

.o_ybw (o_ybw)

);

integer fout1;

initial begin

fout1 = $fopen("result.txt","w");

end

always @ (posedge i_clk)

begin

$fwrite(fout1,"%d\n",o_ybw);

end

endmodule

0X_005m4. 알고리즘 이론의 개요

FPGA(Field Programmable Gate Array) 기반의 이미지 이진화 처리는 주로 디지털 이미지 처리 기술에 의존합니다. 원리는 회색조 이미지를 이진 이미지로 변환하여 이미지에 흑백만 남겨 이미지 데이터를 단순화하고 이미지의 추가 분석 및 처리를 용이하게 하는 것입니다.

이미지 이진화 처리에서 가장 일반적으로 사용되는 방법은 임계값 방법입니다. 이는 임계값을 설정한 다음 이 임계값을 기준으로 이미지의 픽셀을 두 가지 범주로 나누는 것을 의미합니다. 구체적으로, 이미지 내 특정 픽셀의 회색조 값이 이 임계값보다 크거나 같으면 흰색(또는 검정색)으로 설정되고, 그렇지 않으면 검정색(또는 흰색)으로 설정됩니다.

임계값 방법의 수학적 공식은 다음과 같습니다.

이진화된 이미지 픽셀 포인트 P(x,y) = { 1, 원본 이미지 픽셀 포인트의 회색 값인 경우 P(x,y) >= 임계값, 0, 원본 이미지 픽셀 포인트인 경우 P(x,y) 회색 값 < 임계값. }

그 중 P(x,y)는 (x,y) 위치에 있는 이미지의 픽셀 포인트입니다.

FPGA 기반 이미지 이진화 처리에는 일반적으로 다음 단계가 포함됩니다.

- 이미지 획득: 카메라나 기타 이미지 입력 장치를 통해 이미지 데이터를 얻습니다.

- 전처리: 수집된 이미지를 노이즈 감소, 정규화 등 전처리하여 이미지 품질을 개선하고 후속 처리의 복잡성을 줄입니다.

- 이진화: 전처리된 이미지를 이진화합니다. 일반적으로 사용되는 방법에는 전역 임계값, 로컬 임계값 등이 있습니다.

- 후처리: 이진화 효과를 개선하기 위해 노이즈 제거, 채우기 등 이진화된 이미지를 추가로 처리합니다.

- 출력: 처리된 이미지 데이터를 디스플레이 장치 또는 기타 장치로 출력합니다.

이 단계에서 FPGA의 역할은 주로 이러한 알고리즘을 구현하고 이미지 데이터를 실시간으로 처리하는 것입니다. FPGA는 병렬 처리 기능과 구성 가능성을 갖추고 있기 때문에 효율적인 실시간 처리가 필요한 이미지 처리 작업을 구현하는 데 매우 적합합니다.

FPGA를 기반으로 한 이미지 이진화 처리의 구체적인 구현은 FPGA 모델, 이미지 처리 알고리즘, 하드웨어 환경 및 기타 요인에 따라 달라집니다. 예를 들어, 다양한 FPGA 모델에는 서로 다른 하드웨어 리소스(예: 로직 유닛, 메모리 크기 등)가 있을 수 있으므로 이미지 처리 알고리즘을 구현할 때 하드웨어 리소스를 기반으로 일부 최적화가 필요할 수 있습니다. 동시에, 다양한 이미지 처리 알고리즘은 컴퓨팅 성능에 대한 요구 사항이 다르므로 알고리즘 요구 사항에 따라 적합한 FPGA 모델을 선택해야 할 수도 있습니다.

일반적으로 FPGA 기반 영상 이진화 처리는 효율적인 실시간 영상 처리 기술로, FPGA의 병렬 처리 능력과 구성 가능성을 활용해 영상 처리 알고리즘을 구현함으로써 영상 데이터의 실시간 처리 및 처리를 구현한다.

5. 알고리즘 전체 프로그램 엔지니어링

오오오오

OO야

영형