1. Introducción básica de la actualización de configuración de FPGA

1.1 Modo de operación de FPGA

Hay dos formas de ejecutar programas FPGA:

(1) Cargar en RAM local (no se guarda cuando se apaga)

(2) Consolide el programa en FLASH (guárdelo después del apagado) y cargue automáticamente el firmware desde la dirección 0 después de que se encienda la FPGA

1.2 Introducción al arranque múltiple de FPGA

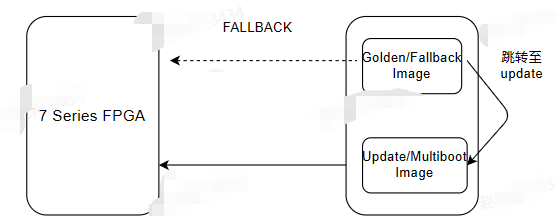

La serie Xilinx 7 tiene un diseño de arranque múltiple, que permite que la FPGA cargue una variedad de aplicaciones diferentes en línea en el sitio de la aplicación y admite respaldo. Pero debe tenerse en cuenta que los FPGA Virtex®-7 HT no admiten el respaldo. Cuando ocurre un error en el proceso de configuración del diseño de arranque múltiple, la FPGA activa una reversión para garantizar que la FPGA permanezca sin cambios.

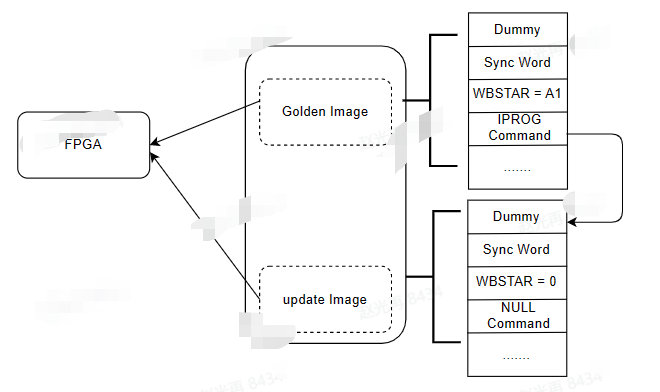

El diseño Multiboot admite FPGA para descargar el archivo de flujo de bits a la dirección especificada. La lógica de salto se inicializa mediante una señal de pulso generada internamente (IPROGRM), cuya dirección está en el registro Golden bitstream WBSTAR. Si la configuración es incorrecta, recurra a la carga de Golden Image.

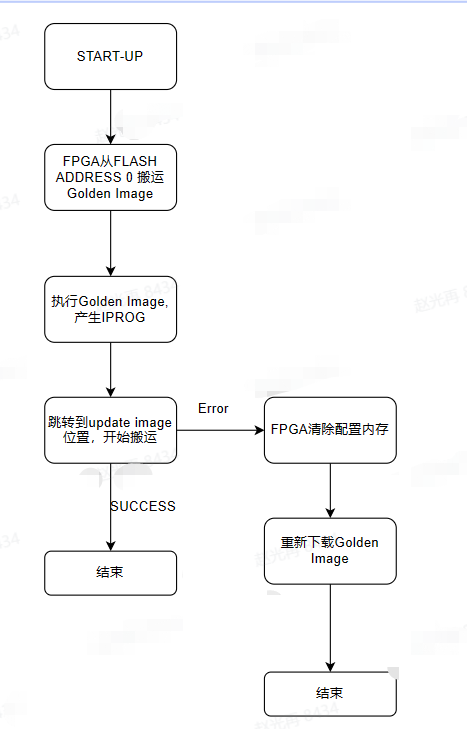

La lógica de implementación detallada de Mulitboot es la siguiente:

1.3 Proceso del cargador FPGA

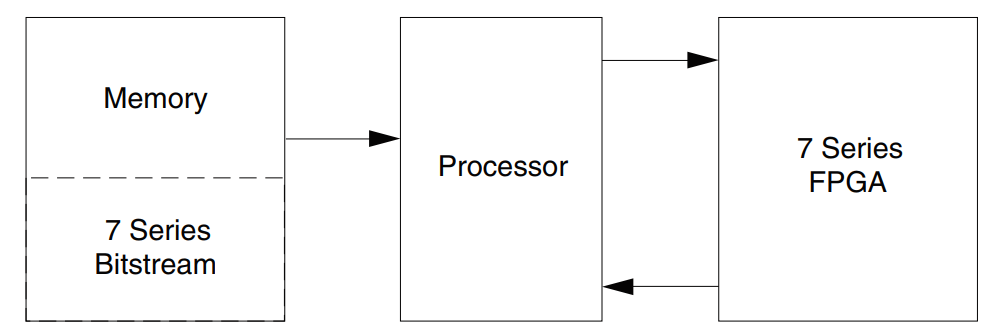

(1) Configure el FPGA a través de la MCU, entendemos el proceso de configuración del FPGA

Como se muestra en la siguiente figura, es un diagrama esquemático de la MCU que configura la FPGA, y el programa se descarga a la FPGA a través de la MCU.

(2) Proceso de configuración

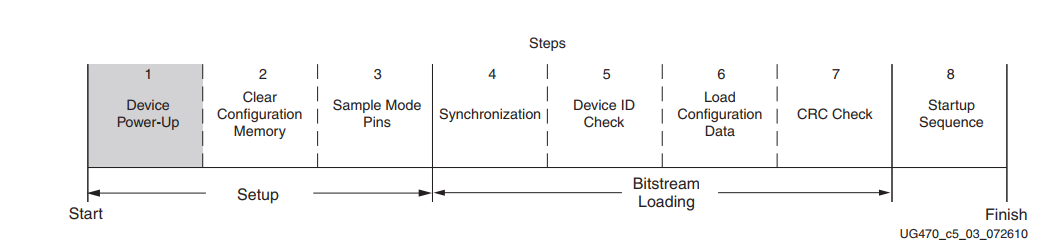

① Encendido o reinicio de configuración

Restablecimiento de configuración: el pin PROGRAM_B tiene efecto

② Inicialización del dispositivo

El encendido o el restablecimiento de la configuración desencadenan la inicialización de la memoria de configuración. En la fase de inicialización, la FPGA bajará INIT_B, restablecerá la máquina de estado de configuración interna y borrará la memoria de configuración. Cuando se complete la inicialización, la FPGA liberará INIT_B e INIT_B se convertirá en una configuración alta. estado de impedancia Cuando INIT_B se libera en un estado de alta impedancia, la resistencia externa eleva INIT_B. Cuando INIT_B se vuelve alto, la FPGA adopta el estado del pin M[2:0] del modo de configuración y el pin de configuración determina el modo de configuración de la FPGA.

Cuando M[2:0] = 111, la FPGA se establece en modo esclavo; cuando M[2:0] = 110, la FPGA se establece en modo SLAVE SelectMAP. Después de muestrear el modo del pin, la FPGA está lista para recibir datos de configuración (bitstream)

③ 配置下载:如果FPGA是配置成Slave Mode时,外部MCU能够将bitstream下载到FPGA。 对于Slave串行模式来说,通过FPGA_D01_DIN 引脚将bitstream下载进去,每个CCLK上升沿下载一个bit。

如果是Slave SelectMAP模式,当FPGA_CSI_B和RDWR_B管脚为低时,数据通过FPGA D[31:0]在CCLK上升沿下载

1.4 FPGA配置bitstream文件的组成

bitstream文件分为两部分,一部分是将基础版本,为Gold image;另一部分是更新程序,为最新程序版本update image。

FLASH的大小,FLASH大小必须是bitstream文件的两倍以上。目前开发板采用的是Artix-7系列的7A35T,bitstreams长度是17536096bits约等于16Mb,那么FLASH最小大小为32Mb.具体怎么计算,可以按照下列的流程进行。

FPGA配置文件称为“Bitstream”,FPGA的“Bitstream”长度是一定的,它的组成如下:

Sync Word: 0xAA995566 (32bit)

Device Identification: A device ID for checking the appropriate device is receiving the bitstream

CRC check: 数据校验

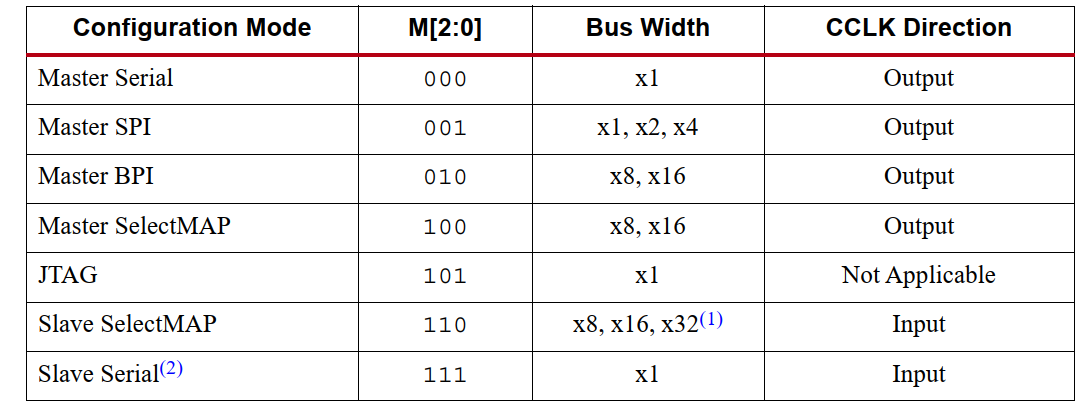

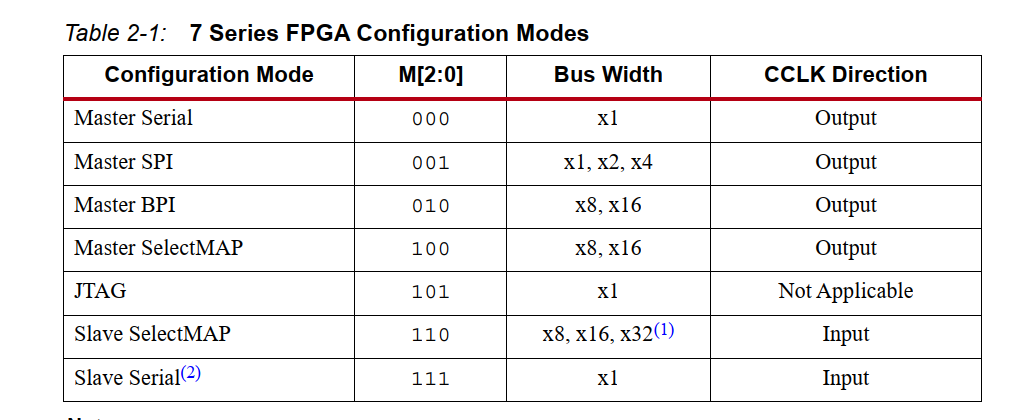

1.5 FPGA配置模式

FPGA配置模式如下,其中主从模式的区别主要是时钟的来源。主模式的时候,来源于FPGA。

其中,Slave SelectMAP x16和x32 bus Widths不支持AES-encrypted bitstreams;

当管脚悬空的时候,默认模式时Slave Serial,因为FPGA内部有上拉电阻。

2 FPGA OTA方案实施

2.1 FPGA在线配置的实施架构

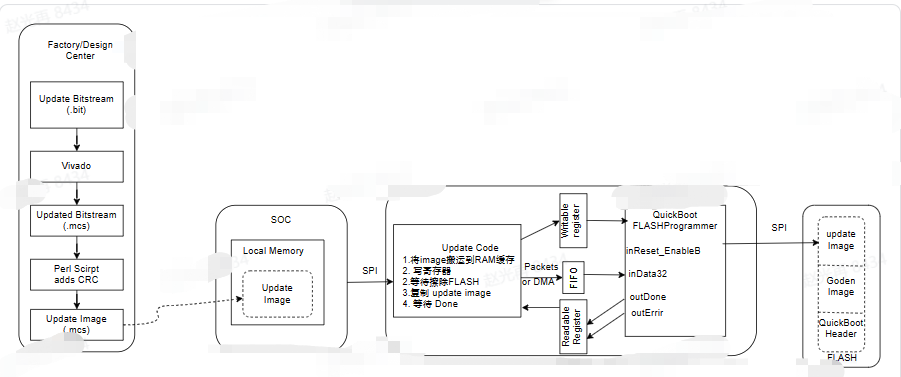

如下图所示,云端FPGA的bitstream文件通过SOC获取,SOC通过SPI将bitstream文件传给FPGA,FPGA通过SPI将bitstream文件写入FLASH。更新完后,SOC可以复位FPGA,FPGA重新加载程序即可。

2.2 FPGA在线配置的硬件需求

2.2.1 BOOT 模式的选择

根据官方Datasheet的建议,选择主模式,CLK由FPGA产生,接口两种形式,分别为“SPI接口”和“BPI接口”,我们选择SPI接口,硬件配置如下图所示。

几点说明如下:

DONE是开漏,接上拉电阻;

INIT_B是开漏,支持双向,需要上拉

Bitstream启动时钟一定需要配置为SPI的CLOCK

CCLK的信号完整性非常关键,需要终端匹配。

DOUT不支持菊花链

FPGA和FLASH的数据线有必要加上串联电阻,减少过冲

7系列的FPGA的VCCO_0的供电需要与SPI的I/o的VCC吻合

为确保FPGA复位的时候,FLASH也复位,FLASH的复位信号应该连接到FLASH的复位信号(防止FLASH正在擦写时候FPGA复位,导致FPGA配置失败)

2.3 FPGA在线配置功能模块详解

要实现FPGA在线配置的功能,首先需要FPGA举要BootLoader模块,这个模块就是Golden Image;其次就是应用程序,即Update Image。当然需要说明的一点就是,Golden Image是通过JTAG下载到FLASH里面,是初始化的第一步。

2.3.1 Golden Image模块的功能拆解

(1)SPI接口通信功能:SOC与FPGA的通信

(2)搬运功能的使能和关闭:SPI接收SOC的指令启动搬运功能,将update image搬运到FPGA的RAM中

(3)FLASH通信功能:FPGA与FLASH通信,对FLASH进行擦除、写和读

(4)跑马灯功能:指示Golden Image运行正常

2.3.2 Golden Image和update Image的配置 流程<ug908>

(1)通过Vivado编译生成bitstreams文件

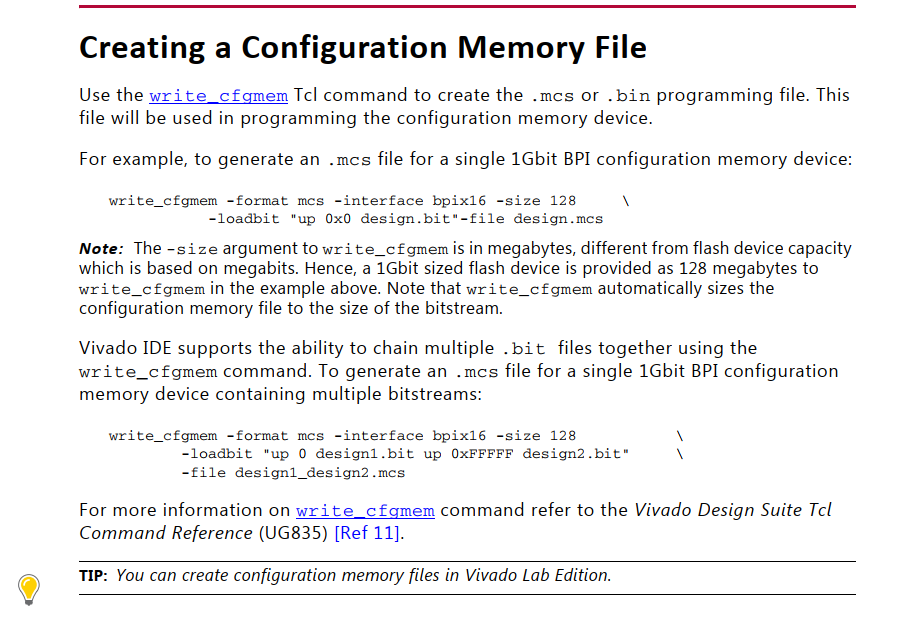

(2)创建可配置文件.msc

(3)连接JTAG

(4)设置配置FLASH型号

(5)下载程序

(6) BOOT FPGA

2.3.3 Golden Image和update Image的配置实例

采用的FPGA是ALINX的开发板,FPGA型号是:ARTIX-XC7A35T-2FGG484

(1)确定配置方式,其中7系列的配置模式如下,主要分为两大类,分别为MASTER和SLAVE模式,主要区别就是数据驱动的CLK从哪里来。MASTER模式就是FPGA提供时钟,SLAVE模式时外部提供时钟。参考手册《UG470》

(2) 通过VIVADO配置Gold Image,其中GOLD 程序需要定位next boot address ,参考手册《xapp1247》

注意:由于我们选用的128Mbits的ROM,而非是128MBytes的ROM。因此在生成.mcs,地址设置是根据Byte计算。

比如我们将update Image的地址配置在ROM的中间位置,地址应该是 0x0040000,而非0x0400000.

VIVADO生产MCS 的脚本如下:

write_cfgmem -format mcs -size 16 -interface SPIx4 -loadbit {up 0x00000000 "E:/xapp1247-multiboot-spi/Vivado/Golden/Golden.runs/impl_2/Top_mudule.bit" } -loaddata {up 0x00400000 "E:/xapp1247-multiboot-spi/Vivado/Update/Update.runs/impl_2/update_module.bit" } -file "E:/xapp1247-multiboot-spi/Vivado/gold_update"。

同时为了有效跳转update,我们需要将在golden image的XDC文件设置如下:

A. 设置SPI接口和模式

#set_property CONFIG_MODE SPIX1 [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

B. 设置压缩模式,节省传输时间

#Compress the bitstream to fit on 128M QSPI

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

C. 在Golden image设置好update image地址

#BITSTREAM PROPERTIES REQUIRED FOR GOLDEN IMAGE:

set_property BITSTREAM.CONFIG.CONFIGFALLBACK ENABLE [current_design]

set_property BITSTREAM.CONFIG.NEXT_CONFIG_ADDR 0x0400000 [current_design]

为了在update image出现错误的时候,能够有限跳转回去golden image,我们需要将update image的文件设置如下:

A. 设置FALLBACK 使能

set_property BITSTREAM.CONFIG.CONFIGFALLBACK ENABLE [current_design]

B. 设置压缩模式,节省传输时间

#Compress the bitstream to fit on 128M QSPI

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

C. 设置SPI接口和模式

#set_property CONFIG_MODE SPIX1 [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property CONFIG_MODE SPIx4 [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

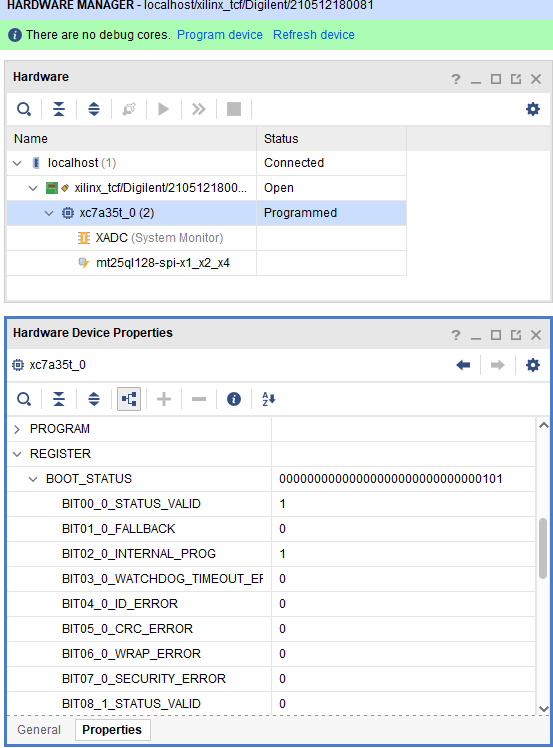

(3)配置后查看是否成功

Hardware Device Properties可以监测Register BOOT_STATUS的状态,如下图所示,配置成功,成功跳转到update image执行

为了判断是否可以跳转,我们可以人为的制造CRC错误,用hex editor打开update 的bitstreams文件,强制修改CRC,可以实现FALLback.