Tres fases de transmisión TLP

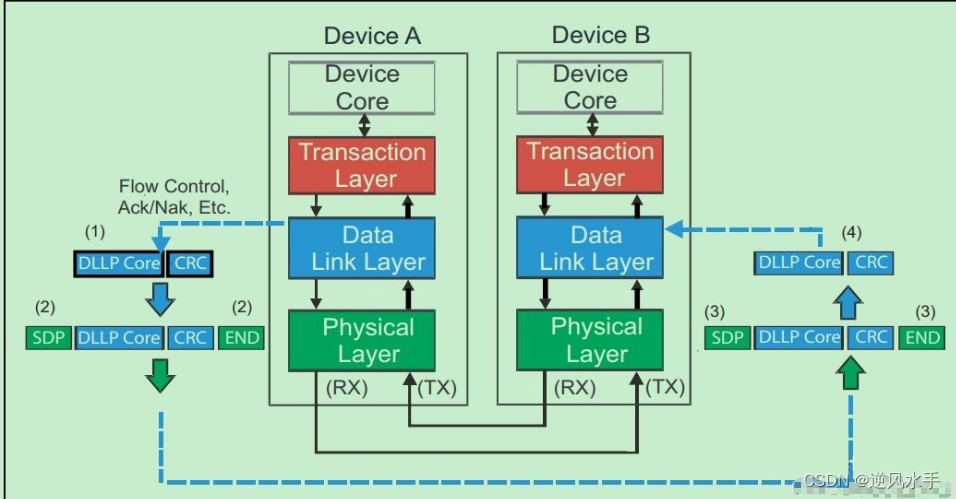

Las tres fases de la transmisión TLP involucran diferentes capas en la pila de protocolos PCIe, de la siguiente manera:

TLP Send Phase 1 (TS1): Esta fase se realiza en la Capa de Transporte (Transaction Layer). En esta etapa, el paquete TLP se codificará y formateará, y se agregará cierta información de control, como el ID de transmisión y el número de secuencia. Al mismo tiempo, en esta etapa se llevarán a cabo algunos procesos relacionados, como el control de flujo y la corrección de errores.

TLP Send Phase 2 (TS2): esta fase se realiza en la capa de enlace de datos. En esta etapa, el flujo de bits del paquete TLP se convierte en una señal diferencial del enlace de la capa física y luego se envía al canal a través del controlador del chip de la capa física (controlador).

TLP Send Phase 3 (TS3): esta fase se realiza en la capa física. En esta etapa, el controlador convierte el flujo de bits en una señal diferencial para el enlace de la capa física y la transmite por el canal. El receptor diezma, muestrea y decodifica estas señales para restaurar el flujo de bits original. Si la transmisión es exitosa, el extremo receptor enviará una retroalimentación de reconocimiento (ACK) al extremo emisor para completar el proceso de transmisión de datos.

Por lo tanto, la fase de envío de TLP comienza desde la capa de transporte, pasa por la capa de enlace de datos y la capa física, y finalmente completa la transmisión de datos.

TS1

En el protocolo PCIe, TS1 se refiere a TLP Transmission Stage 1 (TLP Transmission Stage 1), que también puede denominarse TLP Stage 1 para abreviar. TLP se refiere al Protocolo de capa de transporte (Paquete de capa de transacción), que se utiliza para transmitir datos y controlar información en el sistema PCIe. La fase 1 de envío de TLP se realiza antes de enviar el paquete TLP a la capa física, e incluye los siguientes pasos:

- El remitente codifica el paquete TLP, lo que incluye agregar encabezados, realizar verificaciones de CRC, etc.

- El remitente convierte el paquete TLP codificado en un flujo de bits que se puede transmitir en la capa física.

- El remitente envía el flujo de bits a la capa física para iniciar el proceso de transmisión.

Por lo tanto, TS1 se refiere a una etapa de procesamiento antes de que el paquete de datos TLP pase por la capa de transporte, lo que implica la codificación y conversión del paquete de datos TLP para garantizar que los datos puedan transmitirse correctamente a la capa física. Cabe señalar que en la especificación PCIe, TS1 a veces se denomina etapa 1 de transmisión DLLP (etapa 1 de transmisión de paquetes de capa de enlace de datos), pero el significado es el mismo.

TS23

En el protocolo PCIe, TS2 se refiere a TLP Transmission Stage 2 (TLP Transmission Stage 2), que también puede denominarse TLP Stage 2 o DLLP Transmission Stage 2 (Data Link Layer Packet Transmission Stage 2). TS2 es una etapa de procesamiento cuando el paquete TLP ingresa a la capa de enlace de datos. Su tarea principal es convertir el paquete TLP codificado en la capa de transporte en una señal diferencial que puede ser transmitida por la capa física y realizar algún procesamiento de control y corrección de errores. en él. , como pre-énfasis, control de potencia, salida diferencial, etc.

TS3 se refiere a TLP Transmission Stage 3 (TLP Transmission Stage 3), que también puede denominarse TLP Stage 3 para abreviar. TS3 es una etapa de procesamiento en la capa física, y su tarea principal es esperar la retroalimentación de reconocimiento (ACK) del extremo receptor para determinar si los datos se transmiten con éxito. Si tiene éxito, el remitente notificará a la pila de protocolos de la capa superior; de lo contrario, realizará una retransmisión u otras operaciones de corrección de errores.

Cabe señalar que en la especificación PCIe, a veces TS2 y TS3 se denominan colectivamente como la etapa de transmisión de la capa de enlace de datos, porque todos se ejecutan en la capa de enlace de datos de la pila de protocolos PCIe. Sin embargo, TS2 involucra principalmente el procesamiento de conversión entre la capa física y la capa de enlace de datos, mientras que TS3 es para la confirmación y procesamiento de los resultados transmitidos por la capa física.

Restablecimiento de bus secundario

El restablecimiento de bus secundario es un mecanismo de restablecimiento en el protocolo de bus PCI Express (PCIe), que se utiliza para restaurar dispositivos y subsistemas PCIe en un estado parcialmente fallido.

En el bus PCIe, cada Root Complex (complejo raíz) tiene un bus principal y cada bus secundario está conectado a un puente PCI en el bus principal. Cuando un dispositivo o subsistema en el bus secundario es anormal, otros dispositivos conectados al bus también pueden verse afectados, lo que genera errores de transmisión de datos, bloqueos del sistema y otros problemas. En este momento, el mecanismo de restablecimiento del bus secundario se puede usar para intentar reparar estas condiciones anormales y restaurar el estado de funcionamiento normal del bus.

Específicamente, cuando el Controlador de Host encuentra que ocurre una situación anormal en el Bus Secundario, puede enviar una señal de Restablecimiento del Bus Secundario al Bus. Esta señal avisará a todos los dispositivos y subsistemas conectados al Bus para que realicen una operación de reset, devolviéndolos a su estado inicial. Durante este proceso, se borrarán todas las áreas mapeadas en la memoria y los registros de configuración de dispositivos relacionados con el Bus, y se terminarán todas las operaciones DMA en curso.

Cabe señalar que la señal de restablecimiento del bus secundario solo afectará a los dispositivos y subsistemas del bus actual y no afectará a los dispositivos y subsistemas de otros buses del bus PCIe. Por lo tanto, si hay anomalías en varios buses, puede ser necesario realizar una operación de reinicio en cada bus para lograr un efecto de reparación completo.

En resumen, el restablecimiento del bus secundario es un mecanismo de restablecimiento en el protocolo del bus PCIe, que se utiliza para restaurar dispositivos y subsistemas PCIe que se encuentran en un estado parcialmente fallido. Puede borrar todas las áreas de mapeo de la memoria y los registros de configuración de dispositivos relacionados con el bus y terminar la operación DMA en curso, que es un método importante de recuperación de fallas.