Introducción

Aurora es un protocolo ligero y extensible de capa de enlace para mover datos entre enlaces seriales punto a punto. Esto proporciona una interfaz transparente a la capa física, lo que facilita el uso de transceptores de alta velocidad además de protocolos patentados o estándar de la industria. Si bien utiliza muy pocos recursos lógicos, Aurora ofrece baja latencia, alto ancho de banda y un conjunto de características altamente configurables.

característica:

- Gran ancho de banda, limitado solo por la velocidad de datos del transceptor

- Admite una gran cantidad de cables unidos para un alto ancho de banda general

- Soporta canales full-duplex y simplex

- Tamaño de cuadro ilimitado/encuadre flexible

- Paquete lógico pequeño con interfaz AXI-ST estándar.

- Control de flujo incorporado y soporte de conexión en caliente

Aurora se usa ampliamente en aplicaciones que requieren conexiones de backplane, de placa a placa y de chip a chip. Los segmentos de mercado incluyen comunicaciones por cable, almacenamiento, servidores, prueba y medición, industrial, de consumo y médico, entre otros. Además, Aurora también se puede utilizar como un puerto de depuración en aplicaciones de procesador integradas.

tasa

El rendimiento del núcleo de Aurora 64B/66B depende del número de transceptores, el tipo de transceptor y la tasa de línea objetivo para los transceptores seleccionados

Para los transceptores GTH, el rendimiento varía de 0,48 Gb/s a 254,06 Gb/s desde diseños de un solo carril hasta diseños de 16 carriles, respectivamente. El rendimiento de los transceptores GTY oscila entre 0,455 Gb/s y 400 Gb/s, y las velocidades de línea admitidas oscilan entre 0,5 Gb/s y 25,7813 Gb/s. Cuando la velocidad de línea es superior a 16,375 Gb/s, es posible que el rendimiento máximo de GTY no sea preciso teniendo en cuenta las diferencias de trazado de carriles en el diseño

La codificación 64B/66B ofrece un aumento de rendimiento teórico sobre la codificación 8B/10B debido a su sobrecarga de transferencia muy baja (3 %) en comparación con el 25 % de la codificación 8B/10B

codificación 66B/64B

La codificación 64B/66B codifica datos de 64 bits o información de control en bloques de 66 bits para la transmisión, y los dos primeros bits del bloque de 66 bits representan el encabezado de sincronización, principalmente debido a la alineación de datos en el extremo receptor y la sincronización del flujo de bits de datos recibidos. Hay dos tipos de encabezados de sincronización: "01" y "10". "01" significa que los siguientes 64 bits son datos y "10" significa que los siguientes 64 bits son información de datos.

La información de datos 0 y 1 no está necesariamente equilibrada, por lo que se requiere codificación.

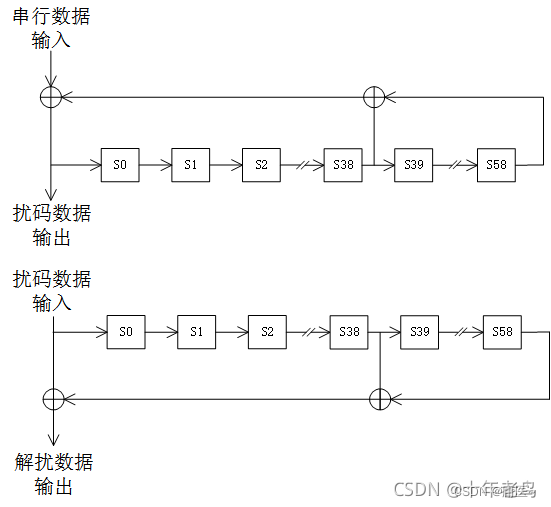

La codificación 64b/66b no tiene forma de limitar la longitud de la ejecución (es decir, la longitud del 0 continuo o del 1 continuo en el flujo de datos) a un valor relativamente pequeño, y solo puede obtener un balance de CC relativamente óptimo y un valor relativamente bajo seleccionando un polinomio apropiado La probabilidad del valor mayor de Run Length. Obviamente, la adopción de la codificación 64b/66b impone requisitos muy altos en el CDR del transceptor en serie.

codificar código

El principio matemático de los códigos de codificación utiliza polinomios, y la selección de polinomios generalmente se basa en las características de los códigos de codificación, incluida la aleatoriedad de los datos generados y la capacidad de codificar 0 y 1 consecutivos. Un codificador simple consta de una serie de flip-flops dispuestos para cambiar un flujo de datos. La mayoría de los flip-flops solo necesitan generar el siguiente flujo de bits, pero en circuitos de codificación complejos, los flip-flops deben realizar operaciones lógicas (operaciones AND y OR) con bits históricos en el flujo de datos.

Los principales módulos funcionales del núcleo 64B/66B

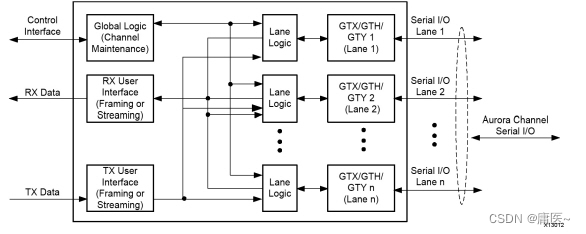

• Lógica de canal: Cada transceptor GT está controlado por una instancia del módulo Lógica de canal, que inicializa cada transceptor, maneja la codificación y decodificación de caracteres de control y realiza la detección de errores.

• Lógica global: el módulo de lógica global en el núcleo realiza la vinculación de canales para la inicialización de canales. Durante el funcionamiento, el canal realiza un seguimiento de los caracteres inactivos No listo definidos por el protocolo Aurora 64B/66B y supervisa todos los módulos lógicos del canal en busca de errores.

• Interfaz de usuario de RX: la interfaz de usuario de recepción de flujo de eje (RX) mueve datos del canal a la aplicación y realiza funciones de control de flujo.

• Interfaz de usuario de TX: la interfaz de usuario de transporte de flujo de eje (TX) mueve datos de la aplicación al canal y también realiza funciones de control de flujo de TX. El módulo de compensación de reloj estándar está integrado dentro del núcleo. Este bloque controla la transmisión periódica de caracteres de compensación de reloj (CC).

retraso del canal

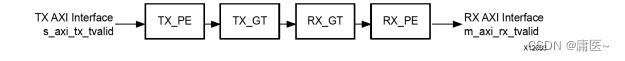

Para la configuración predeterminada de un solo carril, la latencia a través del núcleo Aurora 64B/66B es causada por la latencia de la canalización a través del motor de protocolo (PE) y a través de los transceptores GTX y GTH. La latencia de la tubería PE aumenta con el ancho de la interfaz AXI4-Stream. La latencia del transceptor está determinada por las características del transceptor.

Para tener en cuenta la latencia, los módulos Aurora 64B/66B se dividen entre la lógica de los transceptores GTX, GTH y GTY y la lógica del motor de protocolo (PE) implementada en la FPGA.

Esta figura ilustra la latencia de la ruta de datos.