ilustrar

Grabe una prueba escrita de Fa Ge en la noche del 19 de abril. Compártelo con las personas de IC que lo necesiten.

Puesto: Verificación de diseño de circuitos integrados digitales (Hefei, Anhui)

¡La reimpresión requiere mi consentimiento!

Mis opiniones no son necesariamente precisas, bienvenido a intercambiar y corregir en el área de comentarios ~~

1. (20 puntos) Para una pregunta muy clásica de informática, consulte:

Este tema de los números y la electricidad solo puede decirse que es muy clásico; lo más importante es lidiar con las restricciones.

Luego, con respecto a la simplificación de elementos restringidos, aquí está mi opinión como referencia.

La forma general del elemento de restricción es: y o fórmula = 0 (si no está en esta forma, es mejor cambiarla a esta forma) , como BC = 0 en esta pregunta, o AB + CD = 0; ABC + CD = 0, etc.

La idea de la solución directa es dibujar un mapa de Karnaugh y dibujar una X en la cuadrícula del mapa de Karnaugh correspondiente a cada elemento en el lado izquierdo del signo igual de restricción , es decir, un elemento irrelevante. Para esta pregunta, es dibujar X en la cuadrícula correspondiente a BC ( es decir, B=1 y C=1 ).

La solución específica se da a continuación:

2. (5 puntos) Pregunta de respuesta corta, ¿cuál es la función de las herramientas de síntesis en el flujo ASIC? Al sintetizar, se requiere el archivo SDC para las restricciones. Indique la sintaxis de 3 SDC.

Para dar mi opinión: el papel de la síntesis es asignar el código HDL a la lista de conexiones a nivel de puerta en la biblioteca de dispositivos.

Enumeración de sintaxis SDC:

set_input_delay delay_value -clock clock_ref [ –max ] [ –min ] [ –clock_fall ] [-rise] [-fall] [-add_delay] input_list

create_clock[-add] [-name <clock_name>] -period [-waveform<edge_list>]

set_false_path -desde [obtener_relojes CLKA]-hasta [obtener_relojes CLKB]]

3. (10 puntos) Preguntas intelectuales (preguntas de razonamiento)

El texto es demasiado molesto, así que me di por vencido. Mostrar a todos:

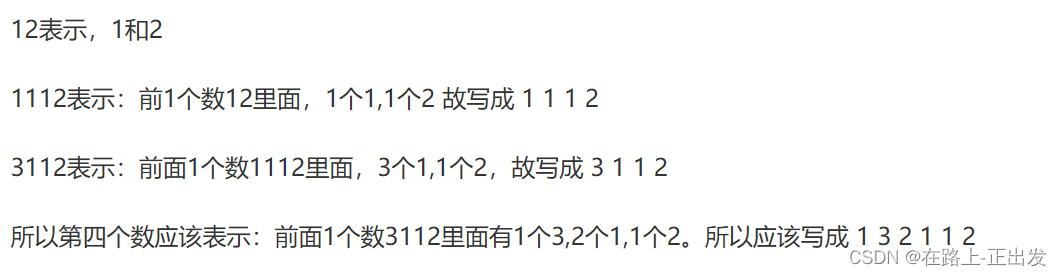

(1) 2 12 1112 3112 132112, ¿cuál es el siguiente número? Dar una razon;

El siguiente número es 311322

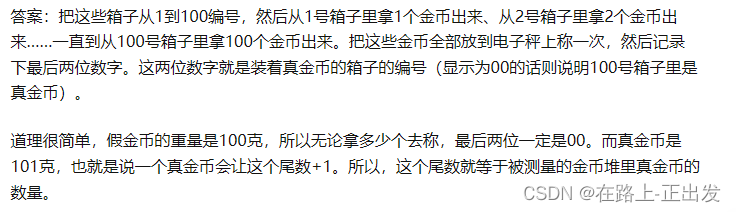

(2) Un ladrón logró entrar en la bóveda del banco. En la bóveda encontró cien cofres, cada uno lleno de monedas de oro. Sin embargo, solo una caja contenía monedas de oro reales y las 99 cajas restantes contenían monedas de oro falsas. La forma y la textura de las monedas de oro reales y falsas son exactamente iguales, y nadie puede distinguirlas a simple vista. Solo tienen una diferencia: las monedas de oro reales pesan 101 gramos cada una, mientras que las monedas de oro falsas pesan 100 gramos. En la bóveda hay una báscula electrónica que puede medir con precisión el peso de cualquier artículo hasta el gramo. Pero desafortunadamente, esta báscula electrónica está conectada al sistema de alarma del banco y no será válida mientras se use una vez. Disculpe, ¿cómo puede un ladrón encontrar la caja que contiene monedas de oro reales usando la balanza electrónica solo una vez?

Este tema es muy clásico:

4. (10 puntos) Elija cualquier proyecto en el que haya participado, describa brevemente el contenido y el proceso del proyecto, describa las tareas que realiza en el proyecto, elija un problema que considere difícil y explique la solución.

5. (5 puntos) Escriba una función de clasificación de burbujas y un programa de prueba en python.

def bubbleSort(arr):

n = len(arr)

# 遍历所有数组元素

for i in range(n):

# Last i elements are already in place

for j in range(0, n-i-1):

if arr[j] > arr[j+1] :

arr[j], arr[j+1] = arr[j+1], arr[j]

arr = [64, 34, 25, 12, 22, 11, 90]

bubbleSort(arr)

print ("排序后的数组:")

for i in range(len(arr)):

print ("%d" %arr[i]),6. (15 puntos) Escriba un árbitro Round Robin en Verilog. Los puertos del módulo son los siguientes:

reloj de entrada;

entrada reset_b;

solicitud de entrada [N-1:0];

entrada [N-1] bloqueo;

subvención de salida [N-1]; //uno-caliente

La señal de entrada de bloqueo aquí indica que el solicitante ha recibido el permiso de arbitraje, y el árbitro no puede iniciar un nuevo arbitraje antes de que el bloqueo correspondiente se reduzca. (Puede entenderse simplemente como ocupación de árbitro)

Esta pregunta requiere una programación parametrizada, y los parámetros se pueden ajustar cuando se instancia el módulo. Es decir, no puede escribir un parámetro fijo, como un módulo con N=8.

Diagrama de forma de onda de referencia:

Ideas para esta pregunta de referencia:

Implementación de Verilog del algoritmo Round-Robin

Combinado con las necesidades del tema, daré mi opinión aquí:

Código fuente del diseño:

// =================================================================================== // 功能: // -1- Round Robin 仲裁器 // -2- 仲裁请求个数N可变 // -3- 加入lock机制(类似握手) // -4- 复位时的最高优先级定为 0 ,次优先级:1 -> 2 …… -> N-2 -> N-1 // By:Xu Y. B. // =================================================================================== `timescale 1ns / 1ps module Round_Robin_Arbiter #( parameter N = 4 //仲裁请求个数 )( input clock, input reset_b, input [N-1:0] request, input [N-1:0] lock, output reg [N-1:0] grant//one-hot ); // 模块内部参数 localparam LP_ST_IDLE = 3'b001;// 复位进入空闲状态,接收并处理系统的初次仲裁请求 localparam LP_ST_WAIT_REQ_GRANT = 3'b010;// 等待后续仲裁请求到来,并进行仲裁 localparam LP_ST_WAIT_LOCK = 3'b100;// 等待LOCK拉低 // 模块内部信号 reg [2:0] R_STATUS; reg [N-1:0] R_MASK; wire [N-1:0] W_REQ_MASKED; assign W_REQ_MASKED = request & R_MASK; always @ (posedge clock) begin if(~reset_b) begin R_STATUS <= LP_ST_IDLE; R_MASK <= 0; grant <= 0; end else begin case(R_STATUS) LP_ST_IDLE: begin if(|request) //首次仲裁请求 begin R_STATUS <= LP_ST_WAIT_LOCK; grant <= request & ((~request)+1); R_MASK <= ~((request & ((~request)+1))-1 | (request & ((~request)+1))); end else begin R_STATUS <= LP_ST_IDLE; end end LP_ST_WAIT_REQ_GRANT://处理后续的仲裁请求 begin if(|request) begin R_STATUS <= LP_ST_WAIT_LOCK; if(|(request & R_MASK))//不全为零 begin grant <= W_REQ_MASKED & ((~W_REQ_MASKED)+1); R_MASK <= ~((W_REQ_MASKED & ((~W_REQ_MASKED)+1))-1 | (W_REQ_MASKED & ((~W_REQ_MASKED)+1))); end else begin grant <= request & ((~request)+1); R_MASK <= ~((request & ((~request)+1))-1 | (request & ((~request)+1))); end end else begin R_STATUS <= LP_ST_WAIT_REQ_GRANT; grant <= 0; R_MASK <= 0; end end LP_ST_WAIT_LOCK: begin if(|(lock & grant)) //未释放仲裁器 begin R_STATUS <= LP_ST_WAIT_LOCK; end else if(|request) //释放的同时存在仲裁请求 begin R_STATUS <= LP_ST_WAIT_LOCK; if(|(request & R_MASK))//不全为零 begin grant <= W_REQ_MASKED & ((~W_REQ_MASKED)+1); R_MASK <= ~((W_REQ_MASKED & ((~W_REQ_MASKED)+1))-1 | (W_REQ_MASKED & ((~W_REQ_MASKED)+1))); end else begin grant <= request & ((~request)+1); R_MASK <= ~((request & ((~request)+1))-1 | (request & ((~request)+1))); end end else begin R_STATUS <= LP_ST_WAIT_REQ_GRANT; grant <= 0; R_MASK <= 0; end end default: begin R_STATUS <= LP_ST_IDLE; R_MASK <= 0; grant <= 0; end endcase end end endmoduleArchivo de simulación:

// ===================================================================== // 功能:测试模块 Round_Robin_Arbiter 功能 // By:Xu Y. B. // ===================================================================== `timescale 1ns / 1ps module TB_Round_Robin_Arbiter(); parameter N = 4; //仲裁请求个数 reg clock; reg reset_b; reg [N-1:0] request; reg [N-1:0] lock; wire [N-1:0] grant;//one-hot initial clock = 0; always #10 clock = ~clock; initial begin reset_b <= 1'b0; request <= 0; lock <= 0; #20; reset_b <= 1'b1; @(posedge clock) request <= 2; lock <= 2; @(posedge clock) request <= 0; @(posedge clock) request <= 5; lock <= 7; @(posedge clock) lock <= 5; @(posedge clock) request <= 1; @(posedge clock) lock <= 1; @(posedge clock) request <= 0; @(posedge clock) lock <= 0; #100; $finish; end Round_Robin_Arbiter #( .N(N) ) inst_Round_Robin_Arbiter ( .clock (clock), .reset_b (reset_b), .request (request), .lock (lock), .grant (grant) ); endmoduleResultados de la simulación:

En comparación con la forma de onda de referencia dada, las dos son consistentes.

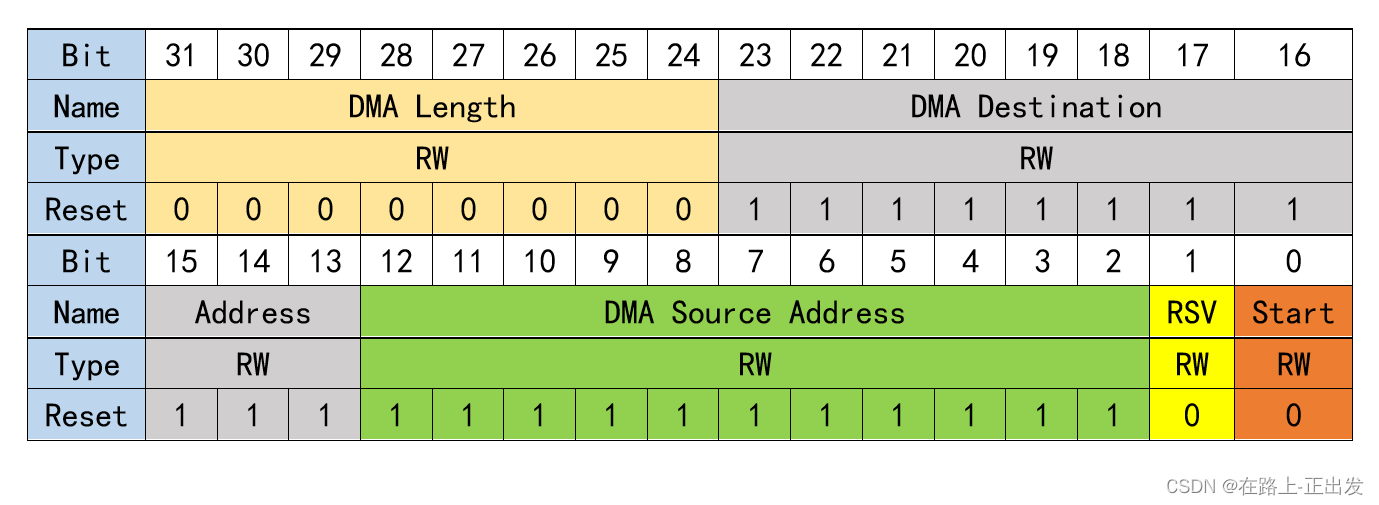

7. (15 puntos) Acerca de la configuración del registro DMA, tabla de registros DMA (dirección 0x81050010):

Tipo indica el tipo de lectura y escritura. Restablecer significa restablecer el valor.

Escriba una función C void dma_driver(void), complete los siguientes requisitos paso a paso:

- Dirección de origen (0x30) requerida para asignar DMA

- Asigne la dirección de destino requerida por DMA (0x300)

- Configurado para transmitir datos de 128 bytes

- iniciar transferencia DMA

- Espere a que finalice la transferencia DMA

La forma en que está escrito el código no es única, esta es mi opinión: (actualizado el 23 de abril, gracias a chongwusc en el área de comentarios por señalar el problema)

void dma_driver(void) { unsigned int *ptr = (unsigned int *)0x81050010; int DMA_SRC_ADDR = 0x30; int DMA_DST_ADDR = 0x300; int DMA_LENGTH = 128; int DMA_START = 0X01; int REG_CLEAR = 0x0; // 根据评论区用户 chongwusc 提出的问题,增加寄存器清零的操作,方便后续通过按位或运算配置寄存器 // 时无BUG *ptr &= REG_CLEAR; // STEP1 *ptr |= DMA_SRC_ADDR << 2; // STEP2 *ptr |= DMA_DST_ADDR << 13; // STEP3 *ptr |= DMA_LENGTH << 24; // STEP4 *ptr |= DMA_START; // 等待 stop while((*prt) & DMA_START) { } }

8. (20 puntos) El filtro de paso de banda de segundo orden está construido con componentes RC. El rango de paso de banda es de 1kHz~30kHz. Las dos resistencias R son ambas de 10kΩ. ¿Cuál es la capacitancia de los dos capacitores?

En primer lugar, debe saber cómo es el circuito del filtro de paso de banda (RC) de segundo orden:

La idea básica es calcular la función de transferencia y luego encontrar la frecuencia de corte; dado que R1=R1=10kΩ, la fórmula siempre se denota por R: (Si encuentra algún problema con los pasos de derivación, deje un mensaje en el área de comentarios a tiempo, gracias )

Según la expresión finalmente derivada, para jwRC2, este ítem, cuando w tiende a infinito, uo/ui tiende a cero. Entonces, el punto crítico de alta frecuencia es wRC2 = 1+2C2/C1 (ignore el elemento de baja frecuencia 1/jwRC1 en este momento);

De igual forma, para el ítem de baja frecuencia 1/jwRC1, w tiende a infinitas horas, uo/ui tiende a cero, entonces el punto crítico de baja frecuencia es 1/wRC1 = 1+2C2/C1;

ordenado:

El proceso de solución utiliza MATLAB:

Las ideas se refieren a: diseño de circuito de filtro de frecuencia RC

Hasta ahora, se han resuelto todas las preguntas de la prueba escrita de Fa Ge en la noche del 19. Si tiene alguna pregunta, hágamelo saber a tiempo (deje un mensaje en el área de comentarios ~~)

¡Vamos IC!

chupar suerte

Esta es una historia posterior. Después de una larga espera, finalmente recibí las noticias de seguimiento hoy (9 de mayo) y aprobé el examen escrito:

Dar ánimos a los compañeros que van a hacer la prueba escrita, ¡vamos!