Capítulo 3 Bus y memoria

Descripción general del autobús

Definición : Canal de transmisión de información, un conjunto de cables eléctricos compartidos que transmiten información entre varios componentes en un sistema informático (incluso entre sistemas).

El sistema de bus generalmente consta de una línea de transmisión + interfaz + controlador de bus .

Características eléctricas : la dirección de transmisión y el rango de nivel efectivo de las señales en cada línea de transmisión se dividen en bus unidireccional (simple) y bus bidireccional (dúplex completo, dúplex medio).

La característica eléctrica más básica : en cualquier momento, solo puede haber flujo de información en una dirección, y no se permite un comportamiento opuesto. Puedes enviar y recibir más, enviar más y recibir más; no puedes enviar más y recibir más, enviar más y recibir más.

Para los dispositivos maestros conectados al bus, solo un dispositivo maestro puede enviar datos al bus en cualquier momento.

Lógica de tres estados : alto nivel, bajo nivel, estado de alta impedancia

- La alta impedancia es equivalente a eliminar la influencia de la salida del circuito posterior.

- A menudo hay varios maestros de bus conectados al bus del sistema, y solo un maestro de bus puede ocupar el bus a la vez, y las señales de dirección, datos y control emitidas por otros maestros de bus deben estar en un estado de alta impedancia.

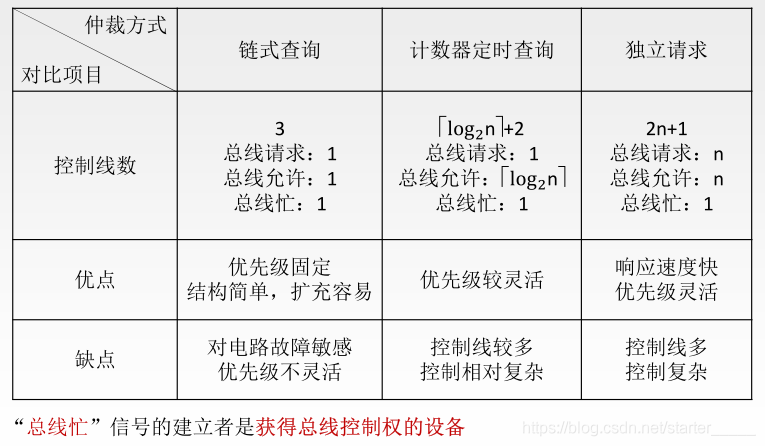

Arbitraje de bus : cuando varios componentes maestros candidatos en el bus solicitan usar el bus al mismo tiempo, debe haber un mecanismo de arbitraje de bus para arbitrar la solicitud de acuerdo con la política.

Arbitraje de bus centralizado:

-

Consultas en serie/en cadena

- Ventajas: método de consulta encadenado con prioridad fija y diseño simple

- Desventajas: Sensible a las fallas del circuito de hardware y la prioridad no se puede cambiar. Cuando los componentes con alta prioridad utilizan el bus con frecuencia, los componentes con baja prioridad no pueden utilizar el bus durante mucho tiempo.

-

Consulta de tiempo de contador

-

Pros: puede cambiar las prioridades, no hay sensibilidad de la cadena a las fallas del circuito

Si comienza desde el dispositivo 0 cada vez, el orden de prioridad de cada dispositivo es el mismo que el método de consulta en cadena, y el orden de prioridad se fija en este momento; si comienza desde el dispositivo después del punto de parada cada vez, cada dispositivo tienen igual prioridad

-

Desventaja: aumentar el número de líneas de control, si el dispositivo tiene NNN , la cantidad de líneas de control requeridas eslog 2 N + 2 \log_2 N+2iniciar sesión2norte+2

-

-

Consultas bajo demanda paralelas/independientes

-

ventaja:

- La velocidad de respuesta es rápida, el bus permite enviar la señal BG directamente desde el controlador al equipo relacionado, sin pasar ni consultar entre los equipos

- Control muy flexible sobre las prioridades

-

defecto:

- El número de líneas de control es grande, si el dispositivo tiene nnn , necesitas2 n + 1 2n+12 norte+1 línea de control. Donde, +1 es la línea BS, que se utiliza para que el dispositivo retroalimente a la unidad de control de bus que se ha utilizado el bus.

- La lógica de control del bus es más compleja.

-

Comunicación en autobús :

En la comunicación por bus, el componente que envía datos se denomina componente de origen y el componente que recibe los datos se denomina componente de destino.

La comunicación que realiza el control de comunicación de bus basado en el punto de vista de "no conciencia" se denomina comunicación síncrona .

La comunicación basada en la "conciencia de la necesidad" para el control de la comunicación del bus se denomina comunicación asíncrona .

Comunicación síncrona : Significa que la transmisión de información entre los dos componentes que participan en la comunicación está controlada por una escala de tiempo de ancho fijo y distancia fija.

Cada dos tics, la unidad de origen envía datos al bus sin reconocer si la unidad de destino recibió los datos. El componente de destino toma muestras del bus cada dos marcas de tiempo para obtener datos, sin confirmar que los datos se han enviado y sin confirmar al componente de origen que los datos recibidos son correctos.

Comunicación asíncrona : Significa que los dos componentes que participan en la comunicación necesitan "percibir" el funcionamiento de la otra parte. Esta "percepción" se realiza a través de la "señal de apretón de manos". Generalmente, se utiliza un conjunto de respuestas para enviar un doble señal de contacto

Es adecuado para la comunicación entre componentes con diferentes velocidades de trabajo y ocasiones donde las líneas de comunicación se ven perturbadas (larga distancia).

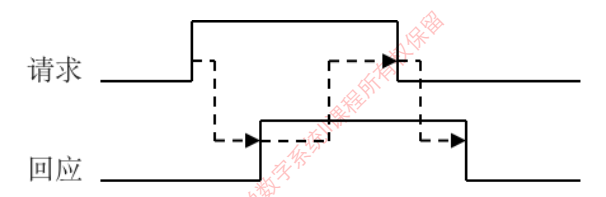

El protocolo "handshake" para comunicación asíncrona se divide en:

-

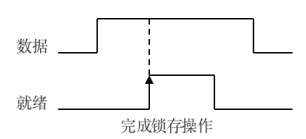

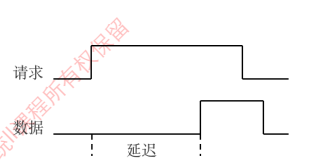

El control unilateral significa que el proceso de comunicación está controlado por el componente de origen o el componente de destino.

El extremo emisor envía datos y se encuentra en el estado de datos listos después de un período de retraso.Idealmente, el extremo receptor recibe el estado listo y toma los datos.

El extremo receptor envía una solicitud de datos y toma los datos después de un cierto retraso

-

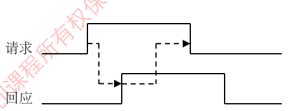

El control bilateral significa que el proceso de comunicación está controlado conjuntamente por el componente de origen y el componente de destino.

Sin enclavamiento : solo existe una relación recursiva , es decir, la señal de respuesta se envía después de recibir la señal de solicitud de la otra parte, y el extremo solicitante no recibe la señal de respuesta, pero cancela automáticamente la señal de solicitud después de un período de retraso .

En esencia, es una especie de control unilateral.

[Error en la transferencia de imagen del enlace externo, el sitio de origen puede tener un mecanismo de enlace antirrobo, se recomienda guardar la imagen y cargarla directamente (img-8b7RqyhA-1655600236284) (https://raw.githubusercontent.com/wjrzm/ PicGO/main/img/202206190855154.png)]

Semi-enclavamiento : hay dos relaciones recursivas , es decir, la señal de respuesta se envía después de recibir la señal de solicitud de la otra parte y la señal de solicitud se cancela después de recibir la señal de respuesta de la otra parte.

La seguridad es mejor.

Enclavamiento completo : hay tres relaciones recursivas , es decir, la señal de respuesta se envía después de recibir la señal de solicitud de la otra parte, y la señal de solicitud se cancela después de recibir la señal de respuesta de la otra parte, y se envía la señal de respuesta final después de recibir la señal de solicitud de la otra parte Cancelación después de la cancelación de la señal.

La seguridad es la más alta, pero el control es problemático y, a menudo, se usa en la comunicación de red.

índice de rendimiento del autobús

-

Ancho del bus: el número de bits del bus de datos, generalmente el número de buses de datos.

-

La frecuencia de reloj del bus: es decir, cuántos relojes hay en un segundo, es decir, el recíproco del ciclo de reloj T.

-

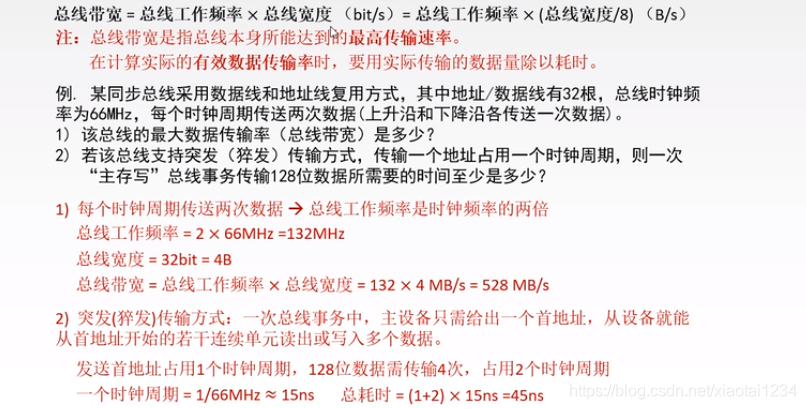

Ancho de banda del bus (velocidad de transmisión estándar): el número de bits de datos que se pueden transmitir en el bus por unidad de tiempo.

Ancho de banda del bus = Frecuencia operativa del bus × Ancho del bus ( bit / s ) = Frecuencia operativa del bus × Ancho del bus8 ( B / s ) = Ancho del bus8 × Ciclo del bus ( B / s ) \begin{aligned}Ancho de banda del bus &= Frecuencia operativa del bus \ times ancho de bus\: (bit/s) \\&= frecuencia de operación del bus\times \frac{ancho de bus}{8} \: (B/s) \\&= \frac{ancho de bus}{8 \ times bus ciclo} \: (B/s)\end{alineado}ancho de banda del bus=frecuencia de funcionamiento del autobús×Ancho de bus( bit / s ) _=frecuencia de funcionamiento del autobús×8ancho de autobús( B / s )=8×ciclo de autobúsancho de autobús( B / s ) -

Número de ciclos de transferencia de datos individuales

-

Modo normal: al transmitir, envíe primero la dirección y luego envíe los datos (es decir, envíe un número en dos ciclos de trabajo)

-

Modo de ráfaga: solo el primer número adopta el método normal (dos ciclos de trabajo), y los datos subsiguientes solo necesitan un ciclo de trabajo (generalmente satisfaciendo el principio de localidad, no es necesario enviar la dirección, la dirección se incrementa automáticamente en 1)

-

-

RS232-C: comunicación serial asíncrona de un solo extremo de baja velocidad

En el modo de transmisión no balanceado, las señales de datos en los extremos de recepción y envío son relativas a la tierra de la señal, y la capacidad de resistir la interferencia del modo común es pobre. La comunicación de corta distancia solo se puede utilizar para la comunicación punto a punto. La comunicación a corta distancia a menudo utiliza un método de conexión de tres hilos (RXD, TXD, GND), que puede lograr una transmisión bidireccional y una comunicación full-duplex. Dado que RS232-C usa lógica negativa, a menudo es necesario agregar un chip de conversión de nivel cuando se conecta con un microcontrolador.

En la transmisión RS232-C, está en un estado de alto nivel cuando está inactivo, los datos de la izquierda son LSB y los datos de la derecha son MSB.

memoria

Memoria: es una colección de muchas unidades de almacenamiento utilizadas para almacenar programas y datos que se están ejecutando actualmente.

Según el principio de la arquitectura de von Neumann, todos los programas deben cargarse en la memoria antes de la ejecución. Por lo tanto, cuando la CPU ejecuta el programa, obtiene instrucciones y datos de la memoria.

Operaciones básicas de memoria:

- Leer: sacar datos de la memoria sin destruir el contenido de la unidad de almacenamiento original

- Escribir: almacenar información en una unidad de almacenamiento, reemplazando la parte original con información existente

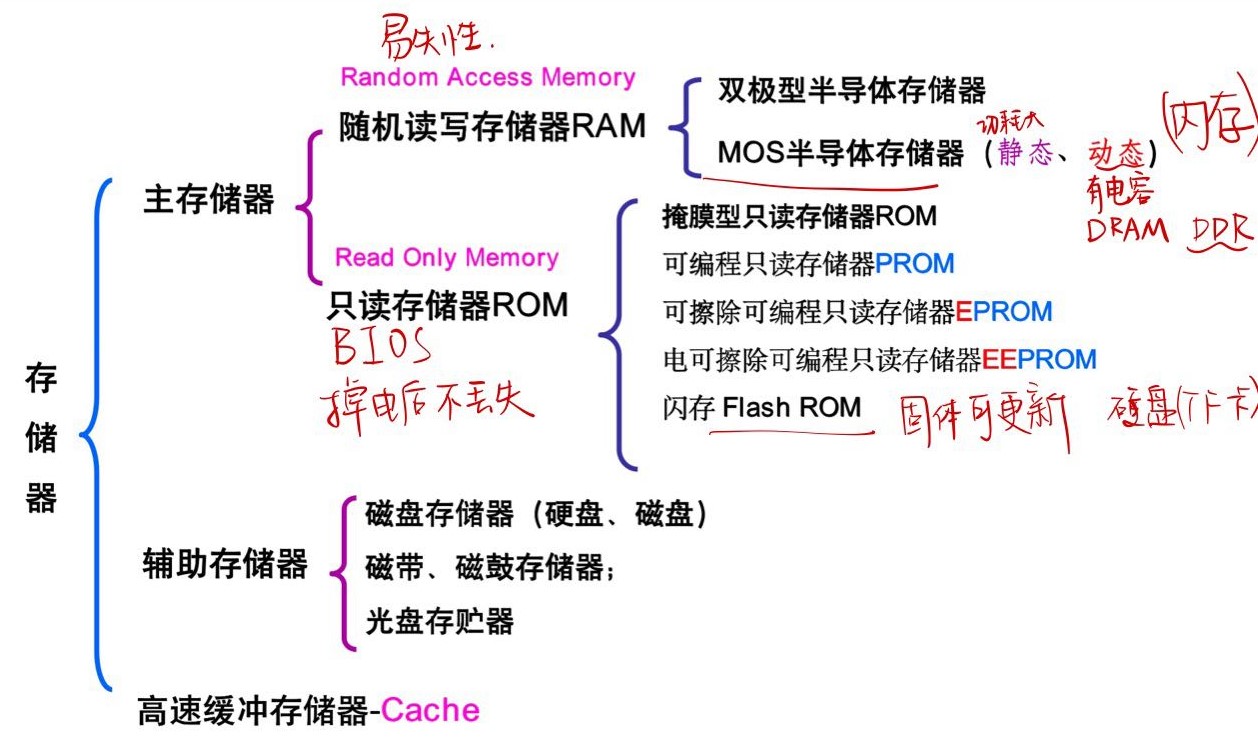

Clasificación de almacenamiento:

Memoria principal: se utiliza para almacenar instrucciones y datos, que pueden ser direccionados directamente por la CPU.

Memoria auxiliar: incapaz de interactuar directamente con la CPU, se caracteriza por una gran capacidad y bajo costo

Caché: Ubicada entre la memoria principal y la CPU, almacena principalmente los segmentos del programa que se están ejecutando y los datos relacionados para uso de alta velocidad por parte de la CPU; la velocidad de la caché es la más alta entre todas las memorias, con poca capacidad y alto costo.

Capacidad de almacenamiento = número de palabras almacenadas × \times× longitud de palabra, cada unidad de memoria puede almacenar 8 bits, es decir, 8 bits binarios, llamados 1 byte

- La relación jerárquica entre la memoria principal y la memoria auxiliar: resolviendo el problema de la pequeña capacidad informática

- Relación jerárquica entre caché y memoria principal: resuelve el problema de la lentitud dentro del host

Cuando almacene más de un byte de datos, use el modo little-endian y el modo big-endian.

Modo Little Endian: use el modo bajo bajo, alto alto.

Cada unidad de memoria puede almacenar 8 Bits (bits binarios), que se convierten en un byte.

Cada bit de almacenamiento está compuesto por un circuito con una función de memoria similar a un flip-flop (Flip Flop).

RAM (memoria de acceso aleatorio) memoria de lectura y escritura aleatoria : puede leer y escribir aleatoriamente cada unidad de almacenamiento en ella, y es el principal componente de almacenamiento del sistema informático. Eso es lo que solemos llamar memoria.

- El tiempo requerido para leer y escribir el contenido de cualquier celda es independiente de la ubicación de la celda

- Todo el contenido de la unidad de almacenamiento se pierde después de un corte de energía y no se puede recuperar

- De acuerdo con el principio de funcionamiento del circuito de almacenamiento, la RAM se puede dividir en RAM estática y RAM dinámica.

**SRAM (RAM estática)** se basa en un flip-flop biestable (circuito complejo, alto costo), siempre que no se pierda la energía, la información nunca se perderá y no hay necesidad de actualizar el circuito .

- La información almacenada es estable, siempre que la alimentación no esté encendida, no haya operaciones de lectura y escritura, y la información guardada sea constante

- Operaciones de lectura y escritura rápidas, cercanas a la velocidad de la CPU

- Gran consumo de energía, baja integración, caro, generalmente utilizado como caché

**DRAM (RAM dinámica)** se basa en condensadores para almacenar información. El circuito es simple y altamente integrado, pero el condensador tiene fugas y la información se perderá. Por lo tanto, se requiere un circuito dedicado para actualizar periódicamente.

- Tiene gran capacidad, bajo consumo de energía y baja velocidad, y se usa ampliamente como memoria.

- Actualizar: El proceso de leer y reescribir cada bit de información almacenada en DRAM.

- Características: La información almacenada es inestable y necesita ser actualizada regularmente, con alta integración y bajo precio, generalmente se utiliza como memoria principal del sistema-memoria.

ROM (memoria de solo lectura) memoria de solo lectura : el contenido solo se puede leer, no escribir. La mayor ventaja es que la información almacenada se puede almacenar durante mucho tiempo. Cuando se apaga la alimentación, la información en el La ROM no desaparecerá. Se usa principalmente para almacenar programas y datos fijos. , que generalmente se usa para almacenar el cargador de arranque.

La capacidad de almacenamiento de 2764 es 8K*8Bits, lo que significa que los bits de la línea de dirección del chip son 13 (2^13) y las líneas de datos son 8.

-

tipo de memoria

La ROM almacena programas del sistema, subrutinas estándar y varias constantes

La RAM está configurada para la programación del usuario

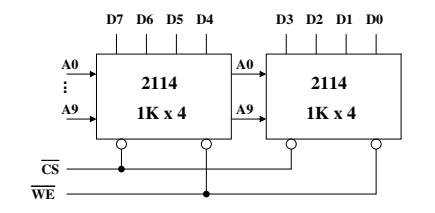

Expansión de memoria :

-

Extensión de bits: aumenta la longitud de la palabra de almacenamiento

Se requiere una memoria de 1024$\times 8 bits, se pueden usar dos memorias de 1024 8 bits, dos de 1024La memoria de 8 bits se puede expandir con dos chips de 1024 \times$4, donde las líneas de dirección están conectadas en paralelo y las líneas de datos están conectadas en serie.

-

Expansión de palabras: aumenta la capacidad de la submemoria

Se requiere una memoria de 64K$\times 8-bit, y se pueden usar 4 piezas de memoria de 16K de 8 bits, y se pueden usar 4 piezas de 16KPara una memoria de 8 bits, se pueden usar cuatro memorias de 16 K \times$8 bits, y se usa un decodificador 2-4 para conectar la señal de selección de chip para las dos líneas de dirección adicionales . Las catorce líneas de dirección originales están conectadas en paralelo.

-

Juzgar la dirección de paridad: para juzgar el atributo de paridad de una palabra/byte, solo necesita mirar el bit 0, 1 es impar y 0 es par.

Interfaz de memoria y CPU

El acceso X86 a los periféricos es independiente, ARM no lo es.

La interfaz de E/S es el puente entre la CPU y los periféricos, y la memoria es el almacén de datos y programas.

Modo de E/S de acceso 80x86: dirección de E/S independiente, aislada de la memoria de acceso

Modo de E/S de acceso MIPS/PowerPC/ARM: dirección de E/S asignada a la memoria (direccionamiento unificado)

Problemas de direccionamiento de chips de memoria y E/S:

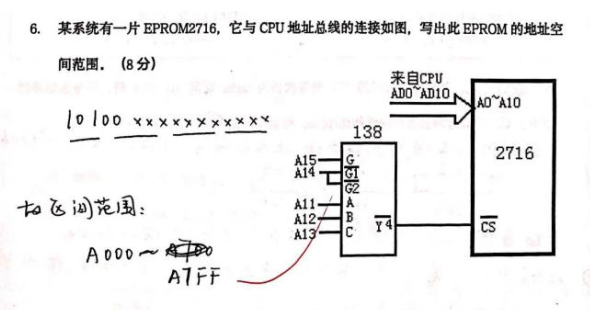

De la tabla de verdad del decodificador 138, A 15 = 1 A_{15}=1A15=1,UN 14 = 0 UN_{14}=0A14=0 , salidaY 4 ‾ = 0 \overline{Y_4}=0Y4=0 por lo tantoA 13 A 12 A 11 = 100 A_{13}A_{12}A_{11}=100A13A12A11=100 , por lo que el rango de memoria es1010000000000000 ∼ 1010011111111111 1010000000000000 \sim 10100111111111111010000000000000∼1010011111111111 esA 000 ∼ A 7 FF A000 \sim A7FFun 000∼A7FF。 _ _

memoria caché

La memoria de gran capacidad que constituye la memoria principal del sistema es la DROM, que es mucho más lenta que la CPU, y el precio de la SROM que iguala la velocidad de la CPU es muy alto. La operación más importante de la computadora es obtener instrucciones y datos de la memoria, y la memoria lenta limita severamente el rendimiento de la CPU. Se agrega una pequeña cantidad de memoria estática entre la CPU y la memoria principal, y esta memoria estática es un caché de alta velocidad .

- Localidad temporal: si se accede a un elemento de información, es probable que se vuelva a acceder en un futuro próximo. Tales como bucle de programa, pila, etc.

- Localidad espacial: es probable que la información que se usará en un futuro cercano esté cerca de la información que se usa en la dirección del espacio, como códigos de secuencia, elementos de matrices.

Caché y memoria son la relación entre escritorios y librerías.

La caché y la memoria se dividen en páginas y bloques del mismo tamaño, por lo que para realizar la conversión de la dirección de la memoria principal y la dirección de la caché hay que diseñar cómo asignar la página de la memoria principal a la página de la caché.

Específicamente, vea la declaración en el PPT:

- Mapeo directo (Direct-mapped): mapeo uno a uno según el número de serie

- Totalmente asociativo: cualquier página en la memoria principal se puede asignar a cualquier página en el caché

- Conjunto asociativo: Dividido en varios grupos, mapeo directo entre grupos, mapeo totalmente asociativo dentro de un grupo

tema:

- Ancho de banda del bus = frecuencia de operación del bus * ancho del bus

- En la asignación de direcciones de la memoria caché, si cualquier bloque de la memoria principal se puede asignar a cualquier bloque de la memoria caché, este método se denomina asignación totalmente asociativa.

- En el arbitraje de bus centralizado, el modo de solicitud independiente tiene el tiempo de respuesta más rápido

- El ciclo de bus se refiere al tiempo requerido para que la BIU complete una operación de memoria de acceso o puerto de E/S.

- Tomando el mismo número de palabras que la condición de comparación, la tasa de transferencia de datos de lectura más alta es - SRAM

- Use chips SRAM de 2K*4 bits para formar una memoria de 16Kbytes , y se requieren un total de 16 chips SRAM

- Hay un sistema de microcomputadora que usa las líneas de dirección de 10 bits inferiores A0~A9 de la CPU como las líneas de dirección de los puertos de entrada y salida. Hay 16 direcciones de puerto dentro del chip de interfaz en el sistema. La señal de selección de chip del El chip de interfaz es generado por el decodificador de dirección.Las líneas de dirección de entrada del decodificador de dirección son generalmente A4~A9. (correspondiente a 4 líneas de dirección, generalmente se selecciona el bit más alto, pero también se requiere una señal de selección de chip)

- Un chip DRAM con una capacidad de 1M*1bit tiene 10 líneas de dirección y 1 línea de datos además de OE, WE, RAS, CAS, fuente de alimentación y conexión a tierra en los pines

- Al leer y escribir una palabra (32 bits) en un bus de datos de 32 bits, la eficiencia es máxima cuando los dos bits más bajos de la dirección de inicio de palabra son 00

- En general, la RAM que constituye la memoria de un sistema de microordenador incluye principalmente SRAM y DRAM.En comparación con SRAM, la principal ventaja técnica de DRAM es su alta densidad de almacenamiento.

- Después de un corte de energía, SRAM, DRAM y SDRAM no pueden retener datos de manera efectiva

- La ventaja de la memoria dinámica sobre la memoria estática es su bajo costo

- En el caso de la multiplexación del bus de dirección/datos, la línea de dirección de la memoria y el pin de la línea de dirección de la CPU deben conectarse a través del pestillo de dirección.

- La memoria estática tiene la ventaja de ser más rápida que la memoria dinámica.

- Las características técnicas de la memoria y la memoria externa se reflejan principalmente en el método de conexión con la CPU

- En la jerarquía de la memoria, el orden de rendimiento de mayor a menor es Reg>SRAM>DRAM>HDD

- El bus de datos transmite datos e información de estado y es bidireccional y de tres estados.

- El bus de direcciones transmite información de direcciones y es unidireccional y de tres estados.

- El bus de control transmite señales de control y es unidireccional.

bloque de caché

- Mapeo directo: mapeo uno a uno según el número de serie, primero divida la memoria principal y el caché en bloques del mismo tamaño (también llamados filas), y luego divida la memoria principal en varias áreas según el tamaño de todo cache. Regla de mapeo: el bloque Y de un área determinada de la memoria principal solo se puede cargar en el bloque Y de Cache.

- Conexión de grupo: dividida en varios grupos, asignación directa entre grupos y asignación de conexión completa dentro de un grupo. Es decir, la memoria principal y el caché se dividen en bloques del mismo tamaño, el caché se divide en varios grupos, como dos grupos, y la memoria principal se divide según la cantidad de grupos de caché. Reglas de mapeo: El bloque n en cualquier área de la memoria principal solo se puede mapear al grupo n de la caché (método directo), que puede ser cualquiera de los dos bloques del grupo n (método asociativo completo)

- Modo totalmente asociativo: cualquier página de la memoria principal se puede asignar a cualquier página de la memoria caché. Primero divida la memoria principal y la caché en bloques (también llamados filas) del mismo tamaño. Reglas de mapeo: un bloque en la memoria se puede cargar en cualquier bloque en el caché. (necesita registrar la relación correspondiente). ETIQUETA de la tabla de conversión de direcciones: el número de unidades es consistente y corresponde al número de bloques de caché, y el contenido es el número del bloque de memoria principal asociado con el bloque de caché.

Mapeo directo entre grupos y mapeo totalmente conectado dentro de grupos. Es decir, la memoria principal y el caché se dividen en bloques del mismo tamaño, el caché se divide en varios grupos, como dos grupos, y la memoria principal se divide según la cantidad de grupos de caché. Reglas de mapeo: El bloque n en cualquier área de la memoria principal solo se puede mapear al grupo n de la caché (método directo), que puede ser cualquiera de los dos bloques del grupo n (método asociativo completo)

- Modo totalmente asociativo: cualquier página de la memoria principal se puede asignar a cualquier página de la memoria caché. Primero divida la memoria principal y la caché en bloques (también llamados filas) del mismo tamaño. Reglas de mapeo: un bloque en la memoria se puede cargar en cualquier bloque en el caché. (necesita registrar la relación correspondiente). ETIQUETA de la tabla de conversión de direcciones: el número de unidades es consistente y corresponde al número de bloques de caché, y el contenido es el número del bloque de memoria principal asociado con el bloque de caché.