1. Información general

Los RTL8211F-CG/RTL8211FD-CG/RTL8211FI-CG/RTL8211FDI-CG de Realtek son transceptores Ethernet altamente integrados que cumplen con los estándares 10Base-T, 100Base-TX y 1000Base-T IEEE 802.3. Proporciona todas las funciones de capa física necesarias para enviar y recibir paquetes Ethernet a través de cables UTP CAT.5. El RTL8211FI y el RTL8211FDI son de grado industrial.

RTL8211F(I)/RTL8211FD(I) utiliza DSP avanzado y tecnología de interfaz analógica (AFE) para realizar la transmisión de datos de alta velocidad a través del cable UTP. Funciones tales como detección de cruce y corrección automática, corrección de polaridad, ecualización adaptativa, cancelación de diafonía, cancelación de eco, recuperación de tiempo y corrección de errores se implementan en RTL8211F(I)/RTL8211FD(I) para proporcionar transmisión y recepción robustas en el tiempo de 10 Mbps, 100 Mbps o 1000 Mbps capacidades.

La transmisión de datos 1000Base-T, 10Base-T y 100Base-TX entre MAC y PHY se realiza a través de la interfaz RGMII. El RTL8211F(I)/RTL8211FD(I) admite múltiples voltajes de señal RGMII, incluidos 3,3, 2,5, 1,8 y 1,5 V.

2 RTL8211F-CG características :

- Compatible con el estándar 1000Base-T IEEE 802.3ab

- Compatible con el estándar 100BASE-TX IEEE802.3u

- Compatible con el estándar 10Base-T IEEE 802.3

- Apoyo RGMII

- Compatible con IEEE 802.3az-2010 (Ethernet de bajo consumo)

- Wake-on-lan incorporado

- Función de interrupción de soporte

- Admite detección paralela, detección cruzada y corrección automática, corrección automática de polaridad

- Admite apagado del núcleo PHYRSTB

- Corrección de desviación de línea base

- Admite transmisión por cable 120mCAT.5 basada en 1000Base-T

- Regulador de conmutación integrado y LDO, señal RGNII opcional 3,3/2,5/1,8/1,5

- Admite oscilador de cristal externo de 25 MHz

- Proporcione una fuente de reloj MAC de 125 MHz

- Proporciona 3 LED de estado de red

- Función de ahorro de energía de enlace de soporte

- ethernet verde

- Paquete verde QFN40

- Proceso de 55 nm, consumo de energía ultrabajo

- Proceso de fabricación de grado industrial (RTL8211FI/RTL8211FDI)

3 Aplicación del sistema

- Televisión Digital

- MAU (Unidad de Acceso a los Medios)

- CNR (Elevador de Comunicaciones y Redes)

- consola de juego

- Impresoras y máquinas de oficina

- Reproductor de DVD y VCR

- concentrador ethernet

- interruptor de Eternet

Además, el RTL8211F(I)/RTL8211FD(I) se puede utilizar en cualquier sistema integrado que requiera una MAC Ethernet sobre una conexión física UTP.

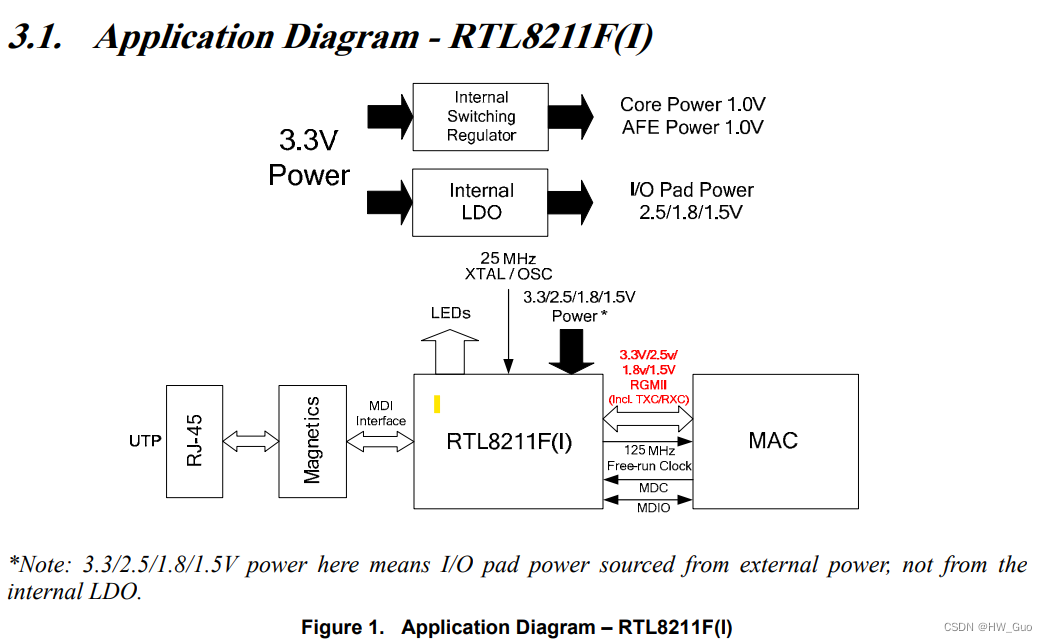

3.1 Diagrama de bloques de la aplicación RTL8211F(I)

3.2 Diagrama de bloques de la aplicación RTL8211FD(I)

4 Diagrama de bloques del sistema

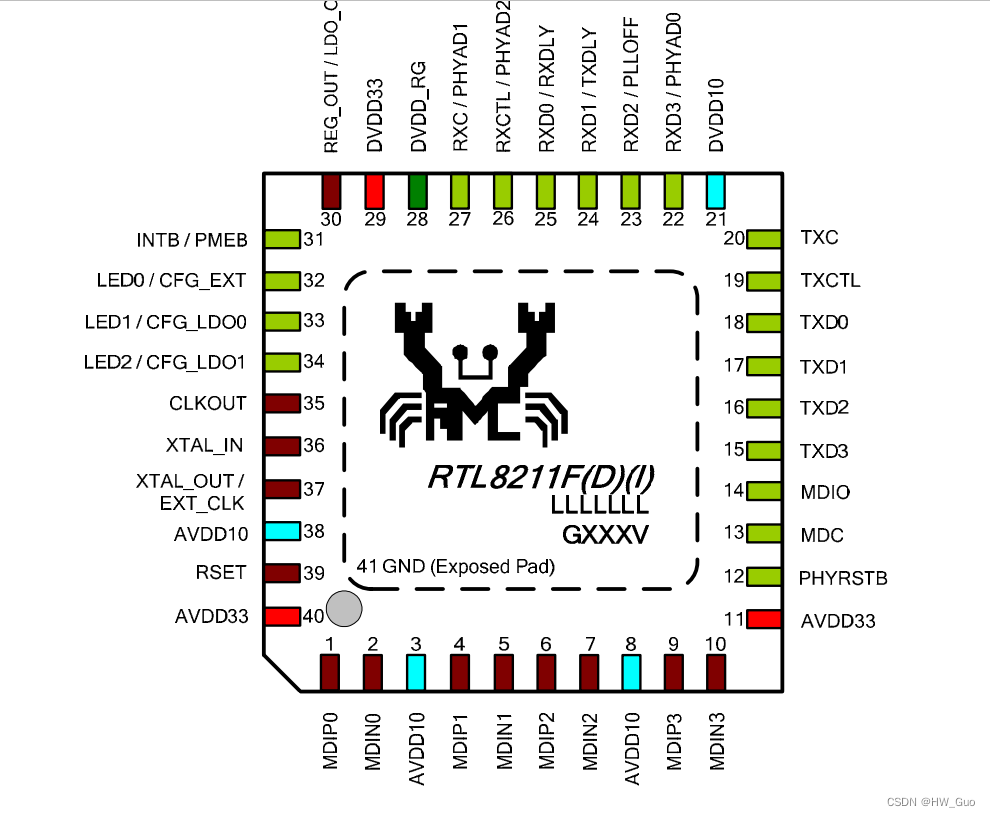

diagrama de 5 pines

Descripción de 6 pines

| Interfaz |

Número de pin |

Pin nombre |

Tipo |

Descripción |

| Interfaz del transceptor |

1 |

MDIP0 |

IO |

el par BI_DA+/- |

| 2 |

MDIN0 |

IO |

||

| 4 |

MDIP1 |

IO |

el par BI_DB+/-, |

|

| 5 |

MDIN1 |

IO |

||

| 6 |

MDIP2 |

IO |

el par BI_DC+/-. |

|

| 7 |

MDIN2 |

IO |

||

| 9 |

MDIP3 |

IO |

el par BI_DD+/-. |

|

| 10 |

MDIN3 |

IO |

||

| RELOJ |

36 |

XTAL_IN |

I |

Entrada de cristal de 25 MHz. |

| 37 |

XTAL_OUT/EXT_CLK |

O |

Salida de cristal de 25 MHz. |

|

| 35 |

CLK FUERA |

O |

Reloj de referencia de 125/25MHz |

|

| RGMII |

20 |

txc |

I |

transmitir reloj de referencia |

| 18 |

TXD0 |

I |

Dato transmitido. Los datos se transmiten de MAC a PHY a través de TXD[3:0]. |

|

| 17 |

TXD1 |

I |

||

| dieciséis |

TXD2 |

I |

||

| 15 |

TXD3 |

I |

||

| 19 |

TXTL |

I |

Transmitir señal de control desde el MAC |

|

| 27 |

RXC/PHYAD1 |

O |

El reloj de referencia de recepción continua |

|

| 25 |

RXD0/RXDLY |

O |

Recibir datos. Los datos se transmiten de PHY a MAC a través de RXD[3:0]. |

|

| 24 |

RXD1/TXDLY |

O |

||

| 23 |

RXD2/PLLOFF |

O |

||

| 22 |

RXD3/PHYAD0 |

O |

||

| 26 |

RXCTL/PHYAD2 |

O |

Recibir señal de control al MAC |

|

| Gestión Interfaz |

13 |

MDC |

I |

Reloj de datos de gestión |

| 14 |

MEDIO |

E/S/PU |

Entrada/Salida de Datos de Gestión |

|

| 31 |

INTB/PMEB |

Acerca de/De |

Evento de interrupción/administración de energía |

|

| Reiniciar |

12 |

PHYRSTB |

I |

Restablecimiento de hardware. Activa baja. |

| CONDUJO |

32 |

LED0/CFG_EXT |

O |

Alto = Enlace activo a 10/100/1000 Mbps |

| 33 |

LED1/CFG_LDO0 |

O |

||

| 34 |

LED2/CFG_LDO1 |

O |

||

| Regulador y Referencia |

39 |

RESET |

O |

Referencia (referencia de resistencia externa). |

| 30 |

REG_SALIDA/LDO_SALIDA |

O |

Para RTL8211F(I): Regulador de conmutación Salida de 1,0 V. Conéctese a un inductor de 2,2 µH o 4,7 µH. |

|

| Energía y Tierra |

29 |

DVDD33 |

PAG |

Alimentación de E/S digital no RGMII. 3,3 V |

| 28 |

DVDD_RG |

PAG |

Alimentación del pad de E/S digital RGMII |

|

| 21 |

DVDD10 |

PAG |

Energía de núcleo digital. 1,0 V |

|

| 11,40 |

AVDD33 |

PAG |

Potencia Analógica. 3,3 V. |

|

| 3,8,38 |

AVDD10 |

PAG |

Potencia Analógica. 1,0 V. |

|

| 41 |

TIERRA |

GRAMO |

Suelo. |

7 Instrucciones de configuración de hardware

| Número de PIN |

Pin nombre |

tipo de pin |

nota de aplicación |

| 35 |

CLK FUERA |

O |

La fuente de reloj de 125M, si no se usa, debe dejarse flotando |

| 14 |

MEDIO |

E/S/PU |

Necesita agregar una resistencia pull-up de 1.5K |

| 22 |

PHYAD0 |

O/LI/PD |

PHY[2:0] Configuración de dirección física |

| 27 |

PHYAD1 |

O/LI/PD |

|

| 26 |

PHYAD2 |

O/LI/PD |

|

| 24 |

TXDLY |

O/LI/PD |

Agregar extracción, agregar retraso de reloj TX de 2 ns |

| 25 |

RXDLY |

O/LI/PD |

加上拉,增加2ns RX时钟延时 |

| 32 |

CFG_EXT |

O/LI/PD |

上拉:IO PAD选择外部电源 下拉:IO PAD选择内部LDO电源 |