Capítulo 1 Interpretación de la arquitectura del brazo heurístico

Capítulo 2 Microarquitectura de la CPU

Capítulo 3 Microarquitectura del sistema

Capítulo 4 Microarquitectura de bus

Capítulo 5 Microarquitectura de monitoreo

Capítulo 6 Microarquitectura de seguridad

Capítulo 7 Microarquitectura de virtualización

Capítulo 8 Arquitectura Armv9-A

Capítulo 9 Arquitectura Armv8-M

Capítulo 10 Arquitectura Armv8-R

Capítulo 11 Interpretación de Cortex-A715

Capítulo 12 Interpretación de Cortex-X3

Capítulo Trece Interpretación del Neoverso

Capítulo 14 Interpretación de Cortex-M85

Capítulo 15 Interpretación de Cortex-R82

Tabla de contenido

1. Descripción general de la arquitectura

1.1 Arquitectura de Von Neumann

2.2 Seis generaciones de herencia

2.3.1 Gran Hermano Cortex-A710

2.3.2 Segundo hermano menor Cortex-R82

2.3.3 Hermanita menor Cortex-M85

2.4.1 Unidad de procesamiento de gráficos GPU

2.4.2 Unidad de procesador de red neuronal NPU

4.3 Elaborar estrategias y ganar a miles de kilómetros de distancia

4.3.1 Carga y descarga - salida de consola

4.3.2 FiberHome - Marquesina LED

4.3.3 Emisión de contraseña-cifrado

4.3.4 Forraje primero - código de inicio

4.3.5 Listo para usar: secuencia de comandos de enlace

prefacio

- Recordatorio : el texto completo tiene 10 000 palabras y el tiempo estimado de lectura es de 15 minutos;

- Lectores : Amigos que estén interesados en la arquitectura Arm;

- Resumen : Este artículo analiza principalmente la lógica subyacente de la arquitectura Arm y presenta el diseño de nivel superior de la arquitectura Arm; basado en la arquitectura del núcleo del procesador, con la arquitectura del sistema como núcleo, y las series A y M. arquitecturas típicas, los componentes clave del sistema están diseñados Descripción fácil de entender, la arquitectura Arm mencionada en este artículo no incluye arquitecturas GPU y NPU;

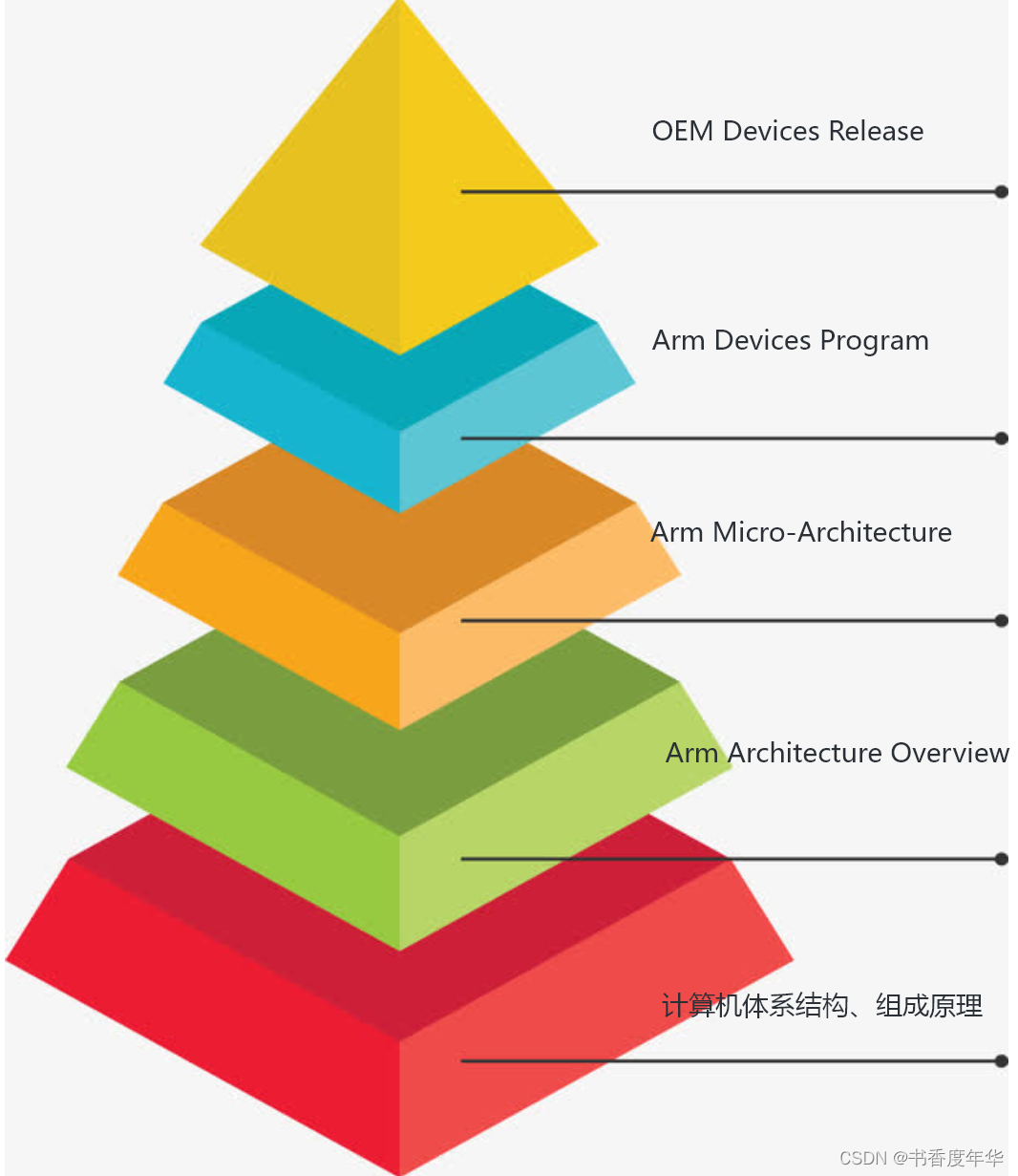

Figura 1 Estructura de conocimiento del brazo

- Palabras clave : arquitectura Arm, microarquitectura, Cortex-A, Cortex-R, Cortex-M, Armv7, Armv8, Armv9, ISA, conjunto de instrucciones, bus AMBA, depuración, Trustzone, virtualización, EL-2, S-EL2, EL-1 , S-EL1, sistema operativo, RISC-V;

- Recomendaciones relacionadas : Si te interesan conceptos como estructura, arquitectura y sistemas, se recomienda leer Arquitectura y Sistemas ;

- Recomendación relacionada : si está interesado en la empresa Arm, se recomienda leer un artículo para comprender la empresa Arm ;

1. Descripción general de la arquitectura

1.1 Arquitectura de Von Neumann

- La estructura de Von Neumann, también conocida como estructura de Princeton, es una estructura de memoria que combina la memoria de instrucciones del programa y la memoria de datos. La dirección de almacenamiento de instrucciones del programa y la dirección de almacenamiento de datos apuntan a diferentes ubicaciones físicas de la misma memoria, por lo que las instrucciones y los datos del programa tienen el mismo ancho. Por ejemplo, las instrucciones y los datos del programa de la unidad central de procesamiento 8086 de Intel tienen un ancho de 16 bits.

- El matemático von Neumann propuso tres principios básicos para la fabricación de computadoras, a saber, el uso de la lógica binaria, el almacenamiento y la ejecución de programas, y la computadora se compone de cinco partes (calculadora, controlador, memoria, dispositivo de entrada, dispositivo de salida). como la arquitectura de von Neumann.

1.2 Arquitectura de Harvard

- La estructura de Harvard es una arquitectura paralela, su característica principal es que el programa y los datos se almacenan en diferentes espacios de almacenamiento, es decir, la memoria del programa y la memoria de datos son dos memorias independientes, y cada memoria se direcciona y accede de forma independiente. Introducción A las dos memorias corresponden los 4 buses del sistema: el bus de datos y el bus de direcciones de programa y datos.

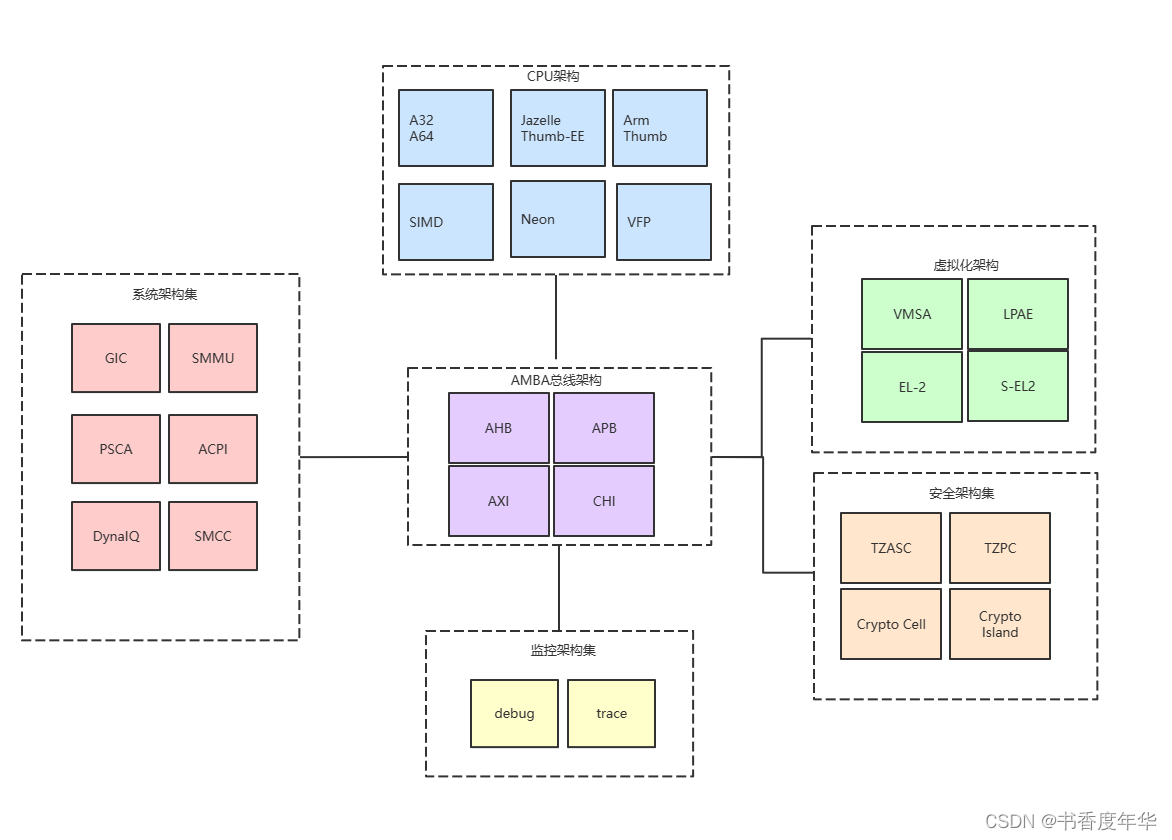

1.3 Arquitectura del brazo

- La arquitectura Arm se refiere a la arquitectura del procesador Arm , incluida la microarquitectura de la unidad central de procesamiento (CPU), la microarquitectura del sistema, la microarquitectura de bus, la microarquitectura de monitoreo, la microarquitectura de seguridad y la microarquitectura de virtualización.

- La microarquitectura de la CPU es la implementación de la arquitectura del conjunto de instrucciones ISA , que incluye A32/T32, A64, NEON, VFP, etc.;

- El conjunto de arquitectura del sistema incluye controlador de interrupción GIC/administrador de memoria del sistema SMMU/administración de energía PSCA/APCI, etc.;

- La microarquitectura bus se refiere a la microarquitectura AMBA , incluyendo AHB, APB, AXI, CHI, etc.;

- La microarquitectura de monitoreo incluye depuración de depuración y rastreo de seguimiento;

- La microarquitectura de seguridad incluye Trustzone, Realm, Crypto Cell, Crypto Island, etc.;

- Las microarquitecturas de virtualización incluyen VMSA, LPAE, EL-2, S-EL2, etc.

| Microarquitectura de CPU | La arquitectura de la unidad central de cómputo que implementa la arquitectura del conjunto de instrucciones y las arquitecturas de las series A, R y M describen la arquitectura de la CPU . |

| Microarquitectura del sistema | La arquitectura de componentes del sistema que existe para que los diversos componentes del procesador funcionen correctamente |

| microarquitectura de autobús | La arquitectura puente que conecta los diversos subsistemas arquitectónicos |

| Supervisión de microarquitectura | Depurar y rastrear cada componente de la arquitectura del sistema. |

| Microarquitectura de seguridad | Una colección de arquitecturas utilizadas para implementar la seguridad del sistema. |

| microarquitectura de virtualización | Una colección de arquitecturas para virtualizar recursos de hardware. |

Figura 2 Arquitectura de nivel superior del procesador Arm

2. Mapa de arquitectura

2.1 Troika

- La arquitectura Arm se divide en tres familias de arquitectura: Cortex-A, Cortex-M y Cortex-R según diferentes escenarios de aplicación;

- La arquitectura Arm A-Profile incluye principalmente procesadores de la serie Cortex-A para terminales móviles y PC, procesadores Neoverse de alto rendimiento para computación en la nube y aprendizaje automático, y procesadores de la serie Cortex-X de alto rendimiento desarrollados en cooperación con los clientes. las series pueden formar series independientes;

- La arquitectura Arm M-Profile incluye principalmente Armv6 M0, Armv7 Cortex-M3, Cortex-M4, Armv8 Cortex-M23, Cortex-M33, Cortex-M35, Cortex-M55, Cortex-M85, utilizados para MCU general, campo de redes IoT;

- La arquitectura Arm R-Profile incluye principalmente Cortex-R4, Cortex-R5, Cortex-R7, Cortex-R8 de Armv7, Cortex-R52 y Cortex-R82 de Armv8, que se utilizan en el campo del control en tiempo real.

La evolución de cada familia arquitectónica es independiente e interrelacionada. En la actualidad, la serie A ha evolucionado a la versión Armv9, la serie M ha evolucionado a la versión Armv8 y la serie R ha evolucionado a la versión Armv8. A continuación se muestra la arquitectura de los procesadores representativos de cada familia.

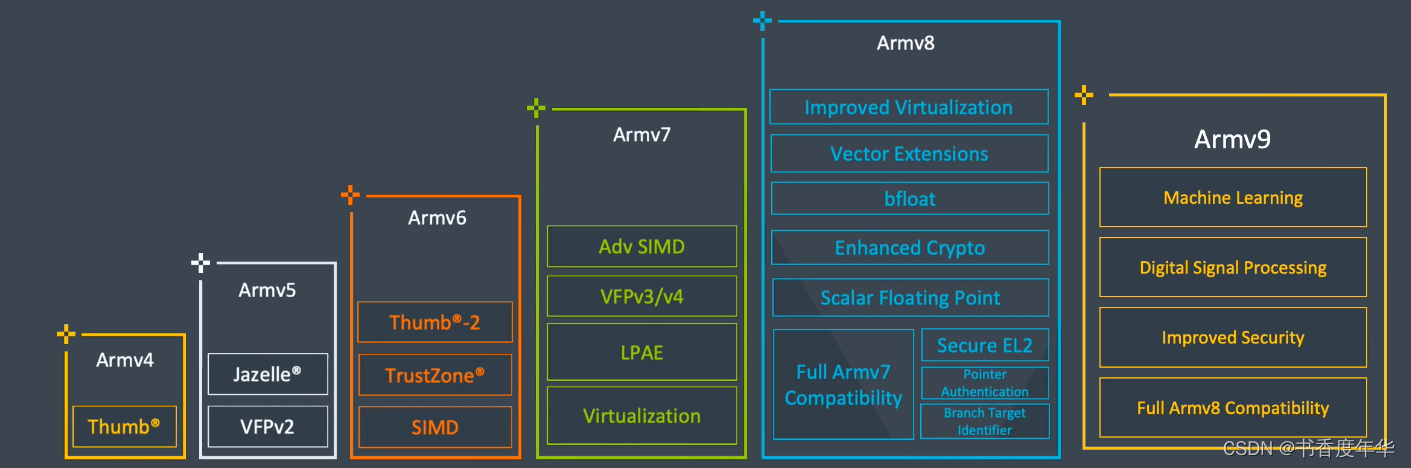

2.2 Seis generaciones de herencia

- La arquitectura Arm ha pasado por seis versiones desde Armv4 a Armv9;

- Actualmente, hay tres versiones de Armv7, Armv8 y Armv9 que están activas en el mercado;

- Cada versión introduce/desaprueba diferentes características funcionales, como Trustzone de Armv6, virtualización de Armv7, extensión de vector SVE de Armv8, extensión de matriz SME de Armv9, etc.

Figura 3 Versión de arquitectura

2.3 Miembros más nuevos

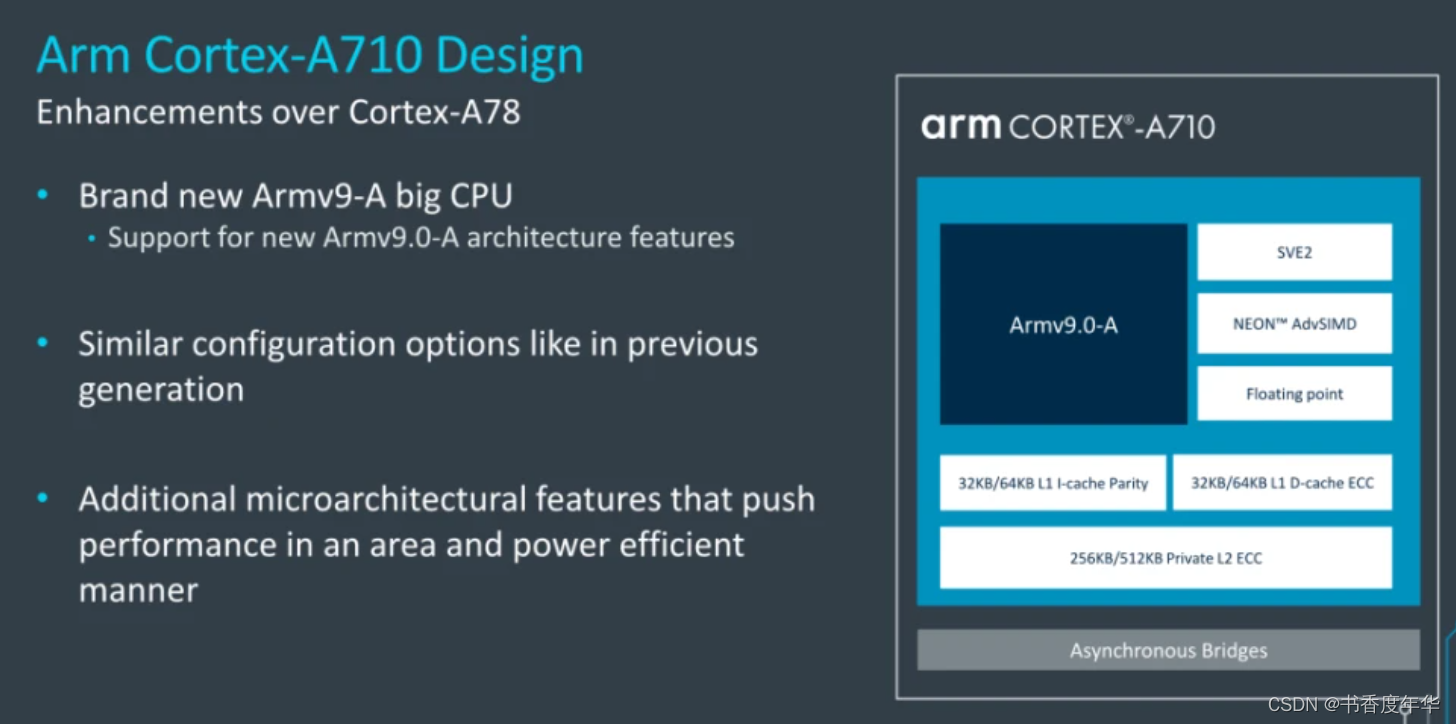

2.3.1 Gran Hermano Cortex-A710

Cortex-A710 es una versión mejorada de Cortex-A78, la arquitectura de núcleo grande de la arquitectura Armv9-A, que es básicamente la misma que la generación anterior.La nueva microarquitectura puede lograr un mejor rendimiento y un menor consumo de energía; el mejorado versión de computación vectorial Compatibilidad con arquitectura extendida SVE2; compatibilidad con arquitectura NEON para SIMD y DSP avanzados; arquitectura de punto flotante FPU compatible con punto flotante vectorial VFPv3.

Figura 4 Diagrama de arquitectura de Cortex-A710

2.3.2 Segundo hermano menor Cortex-R82

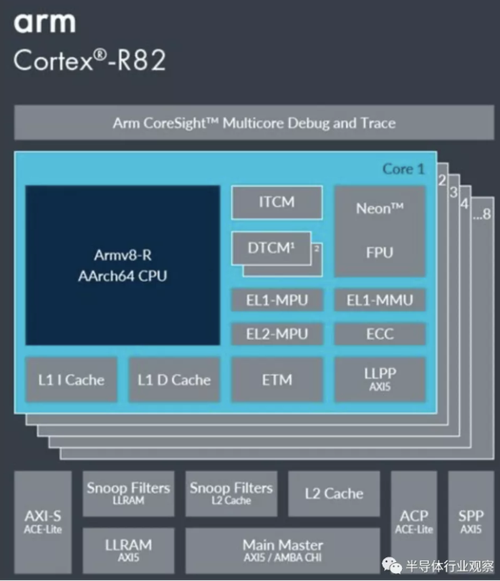

Cortex-R82 es el último procesador de la serie R, que utiliza la arquitectura Armv8, que incluye CoreSgiht MDT, GIC, FPU, TCM, SCU, ACP, AXI-S, AXI-M, LLPP, LLRAM y otras microarquitecturas.

Figura 5 Diagrama de arquitectura de Cortex-R82

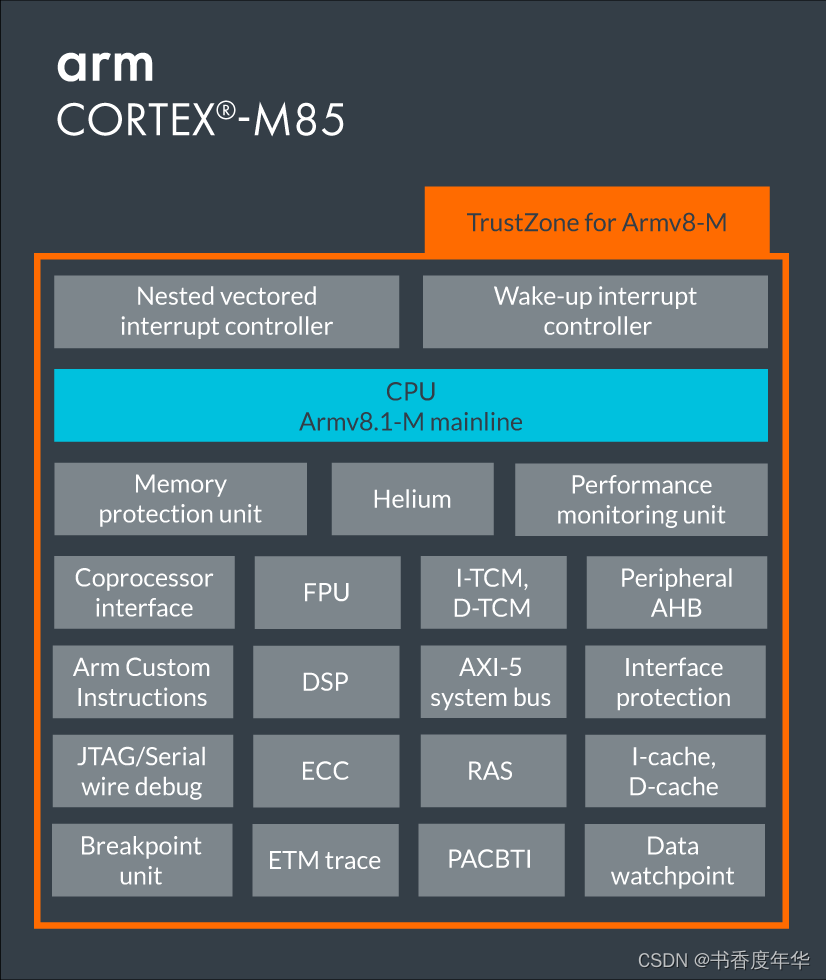

2.3.3 Hermanita menor Cortex-M85

M85 es una arquitectura Armv8.1-M, que incluye MPU, Helio, PMU, CP, FPU, TCM, AHB, DSP, ETM, PACBTI, APH y otras microarquitecturas.

Figura 6 Diagrama de arquitectura de Cortex-M85

2.4 Clan de arquitectura

La arquitectura Arm descrita en este artículo se refiere a la arquitectura de procesador de uso general y no incluye procesadores especializados. Además de los procesadores de propósito general, Arm también tiene procesadores de gráficos y procesadores de redes neuronales.

2.4.1 Unidad de procesamiento de gráficos GPU

Figura 7 Hoja de ruta de la GPU de Malí

La arquitectura GPU se divide en dos ramas: la arquitectura tradicional Mali y la última arquitectura Immortalis:

- Malí tiene actualmente cuatro generaciones, a saber, Utgard, Midgard, Bifrost y Valhall.

- Immortalis es una arquitectura recientemente lanzada, representada por Immortalis-G715

Para obtener más información sobre la arquitectura de GPU, consulte Armar GPU

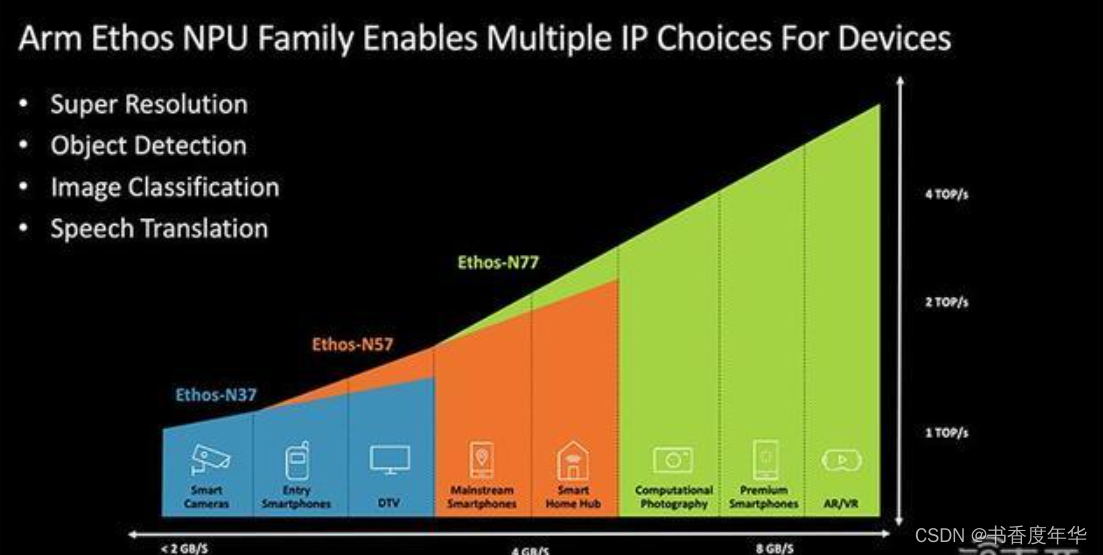

2.4.2 Unidad de procesador de red neuronal NPU

Figura 8 Familia de NPU Ethos

Ethos: NPU es una arquitectura de chip de aprendizaje automático basada en redes neuronales lanzada por Arm, que incluye U55, U65, N78,

Para obtener más información sobre NPU, consulte Armar NPU

3. Arquitectura mágica

La magia arquitectónica se refiere a características arquitectónicas, como magia informática, magia de seguridad, magia de virtualización, etc. En esta parte, presentaremos estas magias misteriosas desde las dimensiones de facción, era y micromagia.

3.1 Facciones

3.1.1 Magia Cortex-A

Armadura 8.0 (Armv8.0-A)

- Avanzar SIMD

- aSIMD, datos múltiples de instrucción única avanzada de longitud fija mejorada

- En Armv8-A, junto con la longitud variable SVE y SVE2, se forma SIMD

- SVE se utiliza principalmente en HPC y es estándar en V9

- Extensión criptográfica (CE)

- Aceleradora AES: AEAD, AESE

- Acelerador SHA: SHA1, SHA256

- CDN

- Aceleración CRC por hardware

Armadura 8.1 (Armv8.1-A)

- Instrucciones de acceso a la memoria atómica (AArch64)

- PostgreSQL ya admite extensiones de acceso atómico de almacenamiento diseñadas para sistemas LSE a gran escala , como la instrucción de carga exclusiva LDXR y la instrucción de almacenamiento exclusiva STXR.

- Regiones de orden limitada (AArch64)

- Secuencia de acceso a la memoria diseñada para instrucciones LSE, carga-adquisición, almacenamiento-liberación de sistemas grandes

- Es una versión mejorada de DMB, DSB e ISB en la era fuera de servicio

- Mayor tamaño del identificador de máquina virtual (VMID) y extensiones de host de virtualización (AArch64)

- ID de máquina virtual más grandes en virtualización

- Ejecute Host directamente en la tecnología EL2 VHE

- Acceso privilegiado Nunca (PAN) (AArch32 y AArch64)

- El acceso del kernel a la memoria del espacio del usuario se puede restringir a través de PAN

Armadura 8.2 (Armv8.2-A)

- Soporte para direcciones de 52 bits (AArch64)

- Admite direcciones físicas grandes de 52 bits y direcciones virtuales grandes, generalmente para aplicaciones de servidor

- La capacidad de los PE para compartir entradas de Translation Lookaside Buffer (TLB) (AArch32 y AArch64)

- TLB compartido Multi-PE, es decir, entradas de tabla de páginas compartidas

- Instrucciones de procesamiento de datos FP16 (AArch32 y AArch64)

- Se admite la precisión media, a diferencia de la precisión simple y doble

- Perfilado estadístico (AArch64)

- Herramientas integradas de estadísticas de instrucciones dentro de la canalización, como retraso de paquetes, información importante de instrucciones de muestreo (acceso/acierto/fallo, error de predicción de bifurcación, interbloqueo de lectura-escritura o no), de qué nivel de almacenamiento se origina

- El soporte de Fiabilidad Disponibilidad Servicio (RAS) se vuelve obligatorio (AArch32 y AArch64)

- Para proporcionar mecanismos para garantizar la confiabilidad, la disponibilidad y la capacidad de servicio, TF-A ha respaldado el marco RAS

- Seguridad extendida CE

- SHA2-512, SHA3

- SM3, SM4

Armadura 8.3 (Armv8.3-A)

- Autenticación de puntero (AArch64)

- Realice la autenticación de identidad en punteros de instrucciones y punteros de datos

- Actualmente, GCC -msign-return-address admite la devolución de la autenticación LR

- Virtualización anidada (AArch64)

- Permitir que los invitados ejecuten hipervisores en EL1

- Añadido mecanismo de acceso de EL1 a EL2

- Compatibilidad avanzada con números complejos de datos múltiples de instrucción única (SIMD) (AArch32 y AArch64)

- aSIMD admite aritmética compleja

- Compatibilidad mejorada con la conversión de tipos de datos de JavaScript (AArch32 y AArch64)

- Soporte mejorado de conversión de tipo de datos javascript

- Un cambio en el modelo de coherencia de memoria (AArch64)

- Agregue soporte RCpc más débil sobre la base de RCsc

- Compatibilidad con el mecanismo de ID para cachés visibles del sistema más grandes (AArch32 y AAch64)

- Expansión del registro de ID de caché

Armadura 8.4 (Armv8.4-A)

- Virtualización segura (AArch64)

- Compatibilidad con S-EL2, puede ejecutar una máquina virtual segura en un entorno seguro

- Mejoras de virtualización anidadas (AArch64)

- Soporte de mesa de traducción pequeña (AArch64)

- Restricciones de alineación relajadas (AArch32 y AArch64)

- Particionamiento y monitoreo de memoria (MPAM) (AArch32 y AArch64)

- Soporte criptográfico adicional (AArch32 y AArch64)

- Contador de escala genérico (AArch32 y AArch64)

- Instrucciones para acelerar SHA

Armadura 8.5/9.0 (Armv8.5-A/Armv9.0-A)

- Etiquetado de memoria (AArch64)

- Identificación de destino de rama (AArch64)

- Instrucciones del generador de números aleatorios (AArch64)

- Limpieza de caché hasta el punto de persistencia profunda (AArch64)

- V5A

Armadura 8.6/9.1 (Armv8.6-A/Armv9.1-A)

- Instrucciones General Matrix Multiply (GEMM) (AArch64)

- Trampas de grano fino para virtualización (AArch64)

- Temporizador genérico de alta precisión

- Sugerencia para la recopilación de datos (AArch64)

- V6-A

Armadura 8.7/9.2 (Armv8.7-A/Armv9.2-A)

- Soporte mejorado para conexión en caliente PCIe (AArch64)

- Carga atómica de 64 bytes y almacenamiento en aceleradores (AArch64)

- Esperar instrucción (WFI) y Esperar evento (WFE) con tiempo de espera (AArch64)

- Grabación de Branch-Record (solo Armv9.2)

Armadura 8.8/9.3 (Armv8.8-A/Armv9.3-A)

- Interrupciones no enmascarables (AArch64)

- Instrucciones para optimizar las operaciones de estilo memcpy() y memset() (AArch64)

- Mejoras a PAC (AArch64)

- Ramas condicionales insinuadas

3.1.2 Cortex-R mágico

Magia de séptima generación (Armv7-R)

Magia de octava generación (Armv8-R)

3.1.3 Magia Cortex-M

Magia de octava generación (Armv8.0-M)

Magia de octava generación v1 (Armv8.1-M)

- MVE (extensión de vector de perfil M), brazo de helio

-

LoB/predicación de cola de bucle/BF

-

Seguridad

- Permiso de ejecución

- V8.2-M PAC (autenticación de puntero)

- V8.2-M BTI (Instrucciones de destino de rama)

- DIT (temporización independiente de datos)

- UDE (extensión de depuración sin privilegios)

era 3.2

| 2022 | PERFIL A 2022 |

| 2021 | PERFIL A 2021 |

| 2020 | PERFIL A 2020 |

| 2019 | - |

| 2018 | PERFIL A 2018 |

| 2017 | PERFIL A 2017 |

| 2016 | PERFIL A 2016 |

| 2015 | PERFIL A 2015 |

| 2014 | PERFIL A 2014 |

3.3 Micromagia

| NEÓN | operaciones con vectores enteros |

| VFP | Operaciones con vectores de punto flotante |

| TODAS | Operación de expansión de vector de longitud variable |

Consulte la familia de registros ID_AA64xxxx para identificar las características arquitectónicas de la implementación actual de la CPU.

4. Ejercicio de arquitectura

4.1 Gran Reunión

Con el paso del tiempo y los cambios en la demanda, cada familia de productos se ha convertido en varios miembros, entre los cuales los procesadores de la serie Cortex-A han lanzado 24 modelos desde A5 a A715, y los procesadores de la serie Cortex-M han lanzado un total de 24 modelos desde M0. a M85. 11 modelos, los procesadores de la serie Cortex-R han lanzado 11 modelos de R4 a R82. Para ver las diferencias entre cada procesador, puede ver la tabla de enlaces a continuación.

- Tabla de comparación de características del procesador de la serie Arm Cortex-A

- Tabla de comparación de características del procesador Arm Cortex-M

- Tabla de comparación de características del procesador ArmCortex-R

4.2 Formación

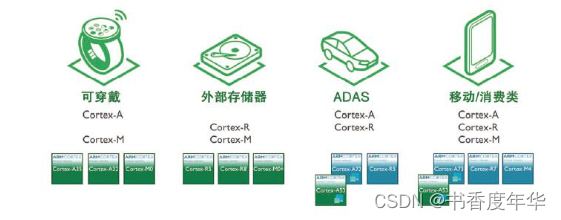

Diferentes procesadores pueden manejar diferentes aplicaciones.

En términos de dispositivos portátiles, se utilizan principalmente Cortex-A y Cortex-M; en términos de almacenamiento, Cortex-R y Cortex-M; en términos de ADAS, hay Cortex-A y Cortex-R, A se usa para alta computación de rendimiento, y R se usa para control de seguridad y en tiempo real; en el mercado de consumo móvil, Cortex-A, Cortex-R y Cortex-M tienen aplicaciones, A se usa como procesador de aplicaciones, R se usa principalmente como banda base , y Cortex-M se puede usar para el campo de chips del concentrador de sensores (concentrador de sensores).

Figura 7 Campo de aplicación

4.3 Elaborar estrategias y ganar a miles de kilómetros de distancia

4.3.1 Carga y descarga - salida de consola

/*Hello world*/

#include <stdio.h>

int main()

{

printf("Hello World\n");

return 0;

}4.3.2 FiberHome - Marquesina LED

#include"led.h"

void LED_Init(void)

{

RCC->APB2ENR|=1<<2;

RCC->APB2ENR|=1<<5;

GPIOA->CRH&=0XFFFFFFF0;

GPIOA->CRH|=0X00000003;

GPIOA->ODR|=1<<8;

GPIOD->CRL&=0XFFFFF0FF;

GPIOD->CRL|=0X00000300;

GPIOD->ODR|=1<<2;

}4.3.3 Emisión de contraseña-cifrado

void mbedtls_aes_encrypt( mbedtls_aes_context *ctx,

const unsigned char input[16],

unsigned char output[16] )

{

int i;

uint32_t *RK, X0, X1, X2, X3, Y0, Y1, Y2, Y3;

RK = ctx->rk;

GET_UINT32_LE( X0, input, 0 ); X0 ^= *RK++;

GET_UINT32_LE( X1, input, 4 ); X1 ^= *RK++;

GET_UINT32_LE( X2, input, 8 ); X2 ^= *RK++;

GET_UINT32_LE( X3, input, 12 ); X3 ^= *RK++;

for( i = ( ctx->nr >> 1 ) - 1; i > 0; i-- )

{

AES_FROUND( Y0, Y1, Y2, Y3, X0, X1, X2, X3 );

AES_FROUND( X0, X1, X2, X3, Y0, Y1, Y2, Y3 );

}

AES_FROUND( Y0, Y1, Y2, Y3, X0, X1, X2, X3 );

X0 = *RK++ ^

( (uint32_t) FSb[ ( Y0 ) & 0xFF ] ) ^

( (uint32_t) FSb[ ( Y1 >> 8 ) & 0xFF ] << 8 ) ^

( (uint32_t) FSb[ ( Y2 >> 16 ) & 0xFF ] << 16 ) ^

( (uint32_t) FSb[ ( Y3 >> 24 ) & 0xFF ] << 24 );

X1 = *RK++ ^

( (uint32_t) FSb[ ( Y1 ) & 0xFF ] ) ^

( (uint32_t) FSb[ ( Y2 >> 8 ) & 0xFF ] << 8 ) ^

( (uint32_t) FSb[ ( Y3 >> 16 ) & 0xFF ] << 16 ) ^

( (uint32_t) FSb[ ( Y0 >> 24 ) & 0xFF ] << 24 );

X2 = *RK++ ^

( (uint32_t) FSb[ ( Y2 ) & 0xFF ] ) ^

( (uint32_t) FSb[ ( Y3 >> 8 ) & 0xFF ] << 8 ) ^

( (uint32_t) FSb[ ( Y0 >> 16 ) & 0xFF ] << 16 ) ^

( (uint32_t) FSb[ ( Y1 >> 24 ) & 0xFF ] << 24 );

X3 = *RK++ ^

( (uint32_t) FSb[ ( Y3 ) & 0xFF ] ) ^

( (uint32_t) FSb[ ( Y0 >> 8 ) & 0xFF ] << 8 ) ^

( (uint32_t) FSb[ ( Y1 >> 16 ) & 0xFF ] << 16 ) ^

( (uint32_t) FSb[ ( Y2 >> 24 ) & 0xFF ] << 24 );

PUT_UINT32_LE( X0, output, 0 );

PUT_UINT32_LE( X1, output, 4 );

PUT_UINT32_LE( X2, output, 8 );

PUT_UINT32_LE( X3, output, 12 );

}4.3.4 Forraje primero - código de inicio

.text

.global _start

_start:

@异常向量表

b reset

nop

b swi_handler

nop

nop

nop

b irq_hander

nop

reset:

ldr sp,=buf+512*3

@irq模式

mrs r0,cpsr

bic r0,#0x1f

orr r0,#0x12

msr cpsr,r0

ldr sp,=buf+512*2

@user模式

mrs r0,cpsr

bic r0,#0x1f

orr r0,#0x10

msr cpsr,r0

ldr sp,=buf+512

mov r0,#0x11

mov r1,#0x22

SWI 1

add r2,r0,r1

nop

nop

stop:

nop

nop

nop

B stop

@软中断

swi_handler:

@入栈保护现场

stmfd sp!,{r0-r12,lr}

mov r0,#0x1f

mov r1,#0x2f

mov r2,#0x3f

mov r3,#0x4f

mov r4,#0x5f

@出栈 恢复现常,还原模式 spsr->cpsr

@lc -> pc

ldmfd sp!,{r0-r12,pc}^

@mov pc,lr

@中断

irq_hander:

@入栈保护现场

stmfd sp!,{r0-r12,lr}

@中断处理

@switch(irqnum)

ldmfd sp!,{r0-r12,pc}^

.DATA

buf:

.space 512*3

.end

4.3.5 Listo para usar: secuencia de comandos de enlace

SECTIONS

{

. = 0x80000,

.text.boot :{*(.text.boot)}

.text : {*(.text)}

.rodata : {*(.rodata)}

.data : {*(.data)}

. = ALIGN(0x8);

bss_begin = .;

.bss :{*(.bss*)}

bss_end = .;

. = ALIGN(4096);

init_pg_dir = .;

+= 4096;

}V. Resumen

Desde el punto de vista del proceso, este artículo proporciona una introducción heurística a la arquitectura Arm basada en las líneas principales de la descripción general de la arquitectura, el desarrollo de la arquitectura, las características de la arquitectura y los ejercicios de arquitectura. Desde la perspectiva de la estructura de conocimiento piramidal, este artículo involucra la arquitectura informática, la arquitectura del sistema Arm, la microarquitectura, el modelo de programación del procesador y la programación de aplicaciones; desde la perspectiva del pensamiento sistémico, es probable que este artículo sea superficial para los lectores, por lo que lo siguiente Los capítulos describirán la arquitectura Arm de una manera más sistemática, sistemática y profunda.

Referirse a

- Arm CPU Architecture Reference Manual Collection

- Una colección de manuales de referencia de microarquitectura de autobuses AMBA

- Colección de manuales de referencia de microarquitectura de sistemas

- Una colección de manuales de referencia de microarquitectura de conjunto de instrucciones

- Una colección de manuales de referencia de microarquitectura segura

- Arquitectura del sistema de control de potencia PSCA

el término

máquina de Turing

Una máquina abstracta, modelo mental;

autobús

El troncal de comunicación pública que transmite información entre varios componentes funcionales de una computadora;

zona de confianza

Tecnología para lograr dominios confiables a través del aislamiento;

hipervisor

Un monitor de máquina virtual es software, firmware o hardware que se utiliza para crear y ejecutar máquinas virtuales.

Compartir el conocimiento es una virtud. Si crees que este artículo está bien escrito, dale me gusta, marca y comparte.