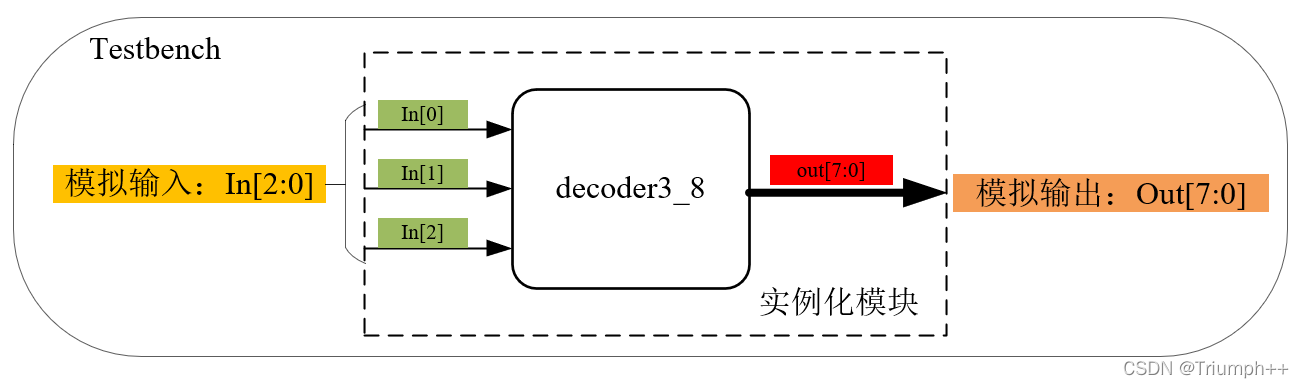

El propósito de escribir Testbench es simular y verificar el código RTL en Modsim y verificar si la lógica del código es correcta al ver la forma de onda de la simulación e imprimir la información. A continuación se describe la estructura del código Testbench con un decodificador 3-8.

¡La esencia del código Testbench es observar si la señal de salida cumple con los requisitos de diseño simulando el cambio de la señal de entrada! Por lo tanto, el núcleo de Testbench es cómo simular la señal de entrada e ingresar la señal de entrada simulada en el módulo de función para generar la señal de salida, como se muestra en la figura anterior. La solucion es:

- Generar señal de entrada por número aleatorio

- Pase la señal de entrada analógica al bloque de funciones instanciando el bloque

¡El código del banco de pruebas se puede personalizar o generar automáticamente!

2 decodificador personalizado 3-8 código de banco de pruebas

2.1 El módulo funcional existente es un decodificador 3-8, y el código RTL del módulo funcional es:

module decoder3_8(

input wire [2:0] in,

output reg [7:0] out

);

// always/initial 模块中只能用 reg型变量

always @(*) begin

case(in)

3'h0: out = 8'h01;

3'h1: out = 8'h02;

3'h2: out = 8'h04;

3'h3: out = 8'h08;

3'h4: out = 8'h10;

3'h5: out = 8'h20;

3'h6: out = 8'h40;

3'h7: out = 8'h80;

// 避免lanth

default: out = 8'h00;

endcase

end

endmodule2.2 El código de Testbench correspondiente es:

`timescale 1ns/1ns // 时间单位及=精度设置

module tb_decoder3_8();

reg [2:0] in;

wire [7:0] out;

// 初始化

initial begin

in <= 3'h0;

end

// 实现输入信号电平自动变化

always #10 in <= {$random} % 8;

initial begin

$timeformat(-9, 0, "ns", 6);

$monitor("time:%t in:%b out:%b",$time,in,out);

end

// 通过实例化模块把模拟输入信号传入功能模块中

decoder3_8 decoder3_8_inist(

.in(in),

.out(out)

);

endmodule2.3 Código Descripción

(1) Unidad de tiempo: unidad de tiempo de instrucción precompilada de escala de tiempo/precisión de tiempo

- Defina la unidad de tiempo: `timescale 1ns/1ns significa que la unidad de tiempo es 1ns y la precisión de tiempo es 1ns

- La unidad de tiempo y la precisión de tiempo consisten en los valores 1, 10 y 100 y las unidades s, ms, us, ns, ps y fs

- La unidad de tiempo no puede ser menor que la precisión de tiempo

- La unidad de todas las cantidades relacionadas con el tiempo del proceso de simulación (es decir, 1 unidad de tiempo)

- Precisión de tiempo: determine la precisión de las cantidades relacionadas con el tiempo y la escala mínima de 1 ns/1 ps que muestra la simulación. La precisión es de 0,01 ns.

(2) Retraso: #Número

- #10 significa que el tiempo de retraso es de 10 unidades, cuando la unidad de tiempo es 1ns, la afirmación significa que el tiempo de retraso es de 10ns

(3) Denominación del módulo de prueba: tb_<nombre del módulo de funciones>

- El nombre del módulo de función es: decoder3_8, y el nombre del módulo de prueba correspondiente es: tb_decoder3_8

(4) Necesidad de definir la señal de entrada/salida analógica:

- Las señales de entrada/salida son coherentes con las señales de entrada/salida definidas en el módulo de función

- La señal de entrada generalmente se define como una señal de tipo reg , porque debe asignarse en el bloque de instrucción siempre/inicial más adelante.

- La señal de salida es generalmente del tipo de cable.

(5) Inicialización de la señal de entrada

- Inicialice con la declaración inicial , el bloque de código en esta declaración se ejecuta solo una vez

- Se puede inicializar a 0/1 según sea necesario

(6) Use la declaración siempre para darse cuenta del cambio de nivel de la señal durante el proceso de simulación

- siempre se ejecutará varias veces durante la simulación

- siempre #10 en <= {$random} % 8; Significa que el nivel de in cambia cada 10 unidades de tiempo :

{$random}%8 significa seleccionar al azar un número entre [0, 7] - en <= {$random} % 8; la conversión del tipo de datos se realizará automáticamente al asignar

- Es mejor tener solo una declaración después de siempre

(7) Pase la señal de entrada analógica al módulo de función instanciando el módulo

- Es decir, la señal de entrada analógica se puede pasar al módulo de funciones.

(8) Monitoreo en tiempo real de variables a través de $monitor

- Impresión en tiempo real de los valores de las señales de entrada y salida para un fácil monitoreo

- Las funciones del sistema como $monitor deben estar en el bloque de declaración inicial

3 funciones comunes del sistema

¡Las funciones del sistema escritas en el archivo del banco de pruebas deben estar en el bloque de declaración inicial!

3.1 $timeformat establece el formato para mostrar la hora

Usa el formato:

$timeformat(time_unit, decimal_number, suffix_string, minimum_field_wdith);- time_unit: unidad de tiempo, en forma de número. 0(s), -3(ms), -6(us), -9(ns), -12(ps),

-15(ps), también se pueden usar valores intermedios: -10 significa 100ps como unidad - decimal_number: El número de lugares decimales para imprimir el valor de tiempo

- suffix_string: La cadena (cadena de sufijo) que sigue al valor de tiempo, generalmente escribe la unidad de tiempo correspondiente ns, ps, etc.

- minimal_field_wdith: es la longitud mínima de esta parte de la cadena combinada con la cadena de valor de tiempo y la cadena de sufijo

- Propósito principal: cambiar la forma en que tareas como $write, $display, $strobe, $monitor, $fwrite, $fdisplay, $fstrobe y $fmonitor muestran el tiempo en formato %t

3.2 Otras funciones comunes del sistema

$display //打印信息,自动换行

$write //打印信息

$strobe //打印信息,自动换行,最后执行

$monitor //监测变量

$stop //暂停仿真

$finish //结束仿真

$time //时间函数

$random //随机函数

$readmemb //读文件函数uso:

$<系统函数名>("格式控制语句", 变量1, 变量2, 变量3....);- El orden de los tipos de datos en la instrucción de control de formato corresponde al orden de las variables

Los caracteres de control de formato correspondientes son:

(1) Caracteres de escape comunes

| Personaje de escape | significado |

| \norte | nueva línea |

| \t | pestaña horizontal |

| \v | pestaña vertical |

| \\ | barra invertida / |

| \'' | comillas'' |

| \un | campana |

| %% | signo de porcentaje % |

(2) Formatos de datos comunes

| Formato | ilustrar |

| %b / %b | binario |

| %d / %D | decimal |

| %o /%o | octales |

| %S.S | maleficio |

| %y y | Mostrar números decimales en notación científica |

| %c / %C | código ASCII |

| %t / %T | tiempo |

| %s / %S | cuerda |

| %v / %v | Intensidad de la señal de malla de alambre |

| %m / %m | Nombre de jerarquía |

Para más referencias de formato de impresión:

Formato de impresión System_Verilog

3.2.1 Tome $display para generar e imprimir información como ejemplo

uso:

$display("Add:%b+%b=%d",a, b, c); //格式“%b+%b=%d” 格式控制,未指定时默认十进制

- %b: Indica que la posición correspondiente muestra un número binario

- %d: indica que la posición correspondiente muestra un número decimal

- a, b, c son las variables que se imprimirán correspondientes a la secuencia de caracteres de control de formato en la declaración de control de formato

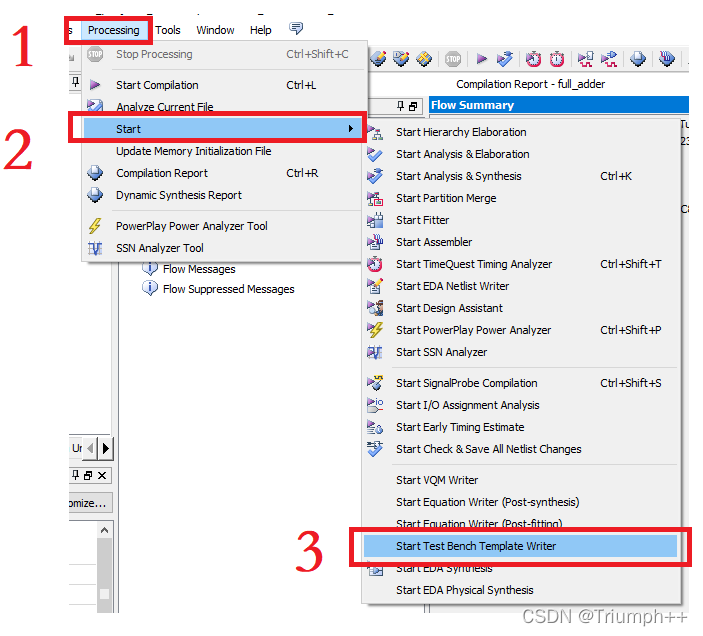

4 Genera automáticamente el código de Testbench

Haga clic en la siguiente imagen en secuencia:

Procesamiento -> Inicio -> Iniciar plantilla de banco de pruebas Witer

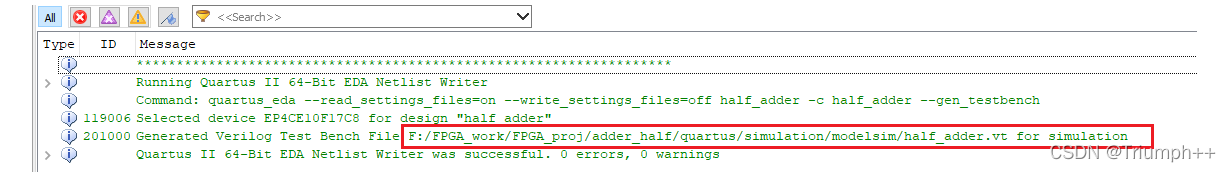

La ruta del archivo de banco de pruebas generado se mostrará a continuación:

Nota: El archivo generado en este momento es un archivo .vt, que debe cambiarse a un archivo .v en la carpeta generada y luego volver a escribirse según sea necesario.