Explicación del nivel de niñera del principio STM32 FSMC/FMC (2)

FSMC (controlador de memoria estática flexible), el nombre completo de "controlador de memoria estática flexible", es un periférico muy distintivo en STM32. A través de FSMC, STM32 puede pasar FSMC y los pines de memoria SRAM, ROM, PSRAM, Nor Flash y NandFlash conectados para intercambiar datos.

Cabe señalar que FSMC solo puede expandir la memoria estática, es decir, S: estático en el nombre, y no puede ser memoria dinámica.Por ejemplo, SDRAM no se puede expandir.

Para el almacenamiento de memoria como DRAM y SRAM, si no lo entiende, lea esto:

Explicación de los conceptos de SDRAM, DRAM y DDR FLASH ROM

Explicación popular de la FSMC

Ahora que sabemos que FMC se puede almacenar fácilmente con la memoria, ¿dónde está la conveniencia?

Usamos DRAM como un ejemplo simple para permitirle comprender la utilidad y conveniencia de FMC de la manera más intuitiva.

En primer lugar, pensemos en ello. Si desea encontrar uno en su computadora 文档文件的数据y luego copiarlo en el disco U , ¿cuáles son los pasos necesarios?

- Encuentre la ubicación (dirección) del documento en su computadora

- copiar este documento (datos)

- Pegue el documento en la memoria USB (transferencia de datos)

Se requieren un total de tres pasos, y nuestra DRAM y NOR FLASH son memorias, piense en ellas como computadoras, y el disco U es nuestro STM32

La microcomputadora de un solo chip se comunica con la memoria externa y también necesita conocer la dirección de los datos (la ubicación en la computadora) y luego transferir (copiar y pegar) el contenido de los datos. En este caso, la memoria debe 地址传输线seguir 数据传输线, además de algunos 控制时序引脚reinicios, escritura de datos, lectura de datos, etc.

-

1. Línea de dirección : se utiliza para transmitir información de dirección. Para dar un ejemplo simple: cuando la CPU busca datos en la memoria o el disco duro, primero encuentra la dirección a través de la línea de dirección y luego saca los datos a través de la línea de datos. Si hay 32 raíces, se puede acceder a los bytes de la 32ª potencia de 2, que son 4GB.

-

2, cable de datos (cable de datos), para transmitir datos o comunicación. En términos sencillos, significa que el microcontrolador envía instrucciones a la memoria y la memoria envía datos al microcontrolador.

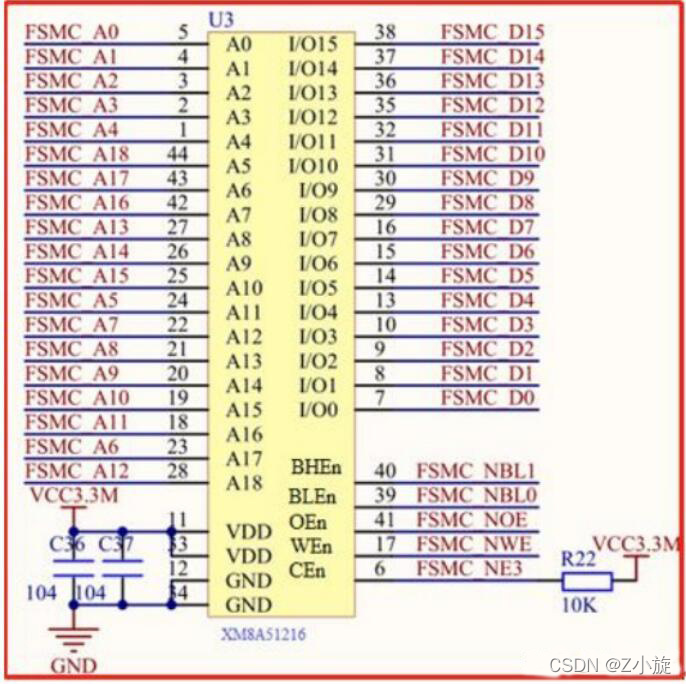

Veamos un diagrama esquemático de una memoria DRAM:

En la figura, A0 ~ 18 son líneas de dirección, con un total de 19 líneas de dirección (es decir, 2^19=512K, 1K=1024); DQ0 ~ 15 son líneas de datos, con un total de 16 líneas de datos. CEn es la señal de habilitación de chip, activo bajo; OEn es la señal de habilitación de salida, activo bajo; WEn es la señal de habilitación de escritura, activo bajo; BLEn y BHEn son control de byte alto y control de byte bajo respectivamente Signal;

Suponiendo que no usamos FSMC y nos comunicamos directamente con DRAM, el código debe escribirse así:

CEn=0;

WEn=0;

....

省略的控制时序

//确定地址线

A0=1;

A1=0;

A2=1;

A3=1;

A4=1;

A5=0;

A6=1;

A7=1;

A8=1;

A9=0;

A10=1;

A11=1;

A12=1;

A13=0;

A14=1;

A15=1;

A16=1;

A17=1;

A18=1;

//地址线确定好了,假设是写数据,那么就要开始发送数据了

CEn=0;

....

省略的控制时序

//数据总线发送数据

D0=1;

D1=0;

D2=1;

D3=1;

D4=1;

D5=0;

D6=1;

D7=1;

D8=1;

D9=0;

D10=1;

D11=1;

D12=1;

D13=0;

D14=1;

D15=1;

....

省略的控制时序

A través de la demostración más básica anterior, encontrará que es muy engorroso comunicarse con DRAM normalmente a través de la lógica secuencial del puerto IO.

Entonces, ¿hay una manera fácil? ¡algunos! La función FSMC que viene con STM32 está especialmente diseñada para este tipo de memoria. En STM32, algunas 引脚están especialmente diseñadas 地址线, algunas están especialmente diseñadas 数据线y algunas están diseñadas 控制线, y luego estas líneas de dirección corresponden a líneas de datos. Entonces, siempre que el 固定的地址externo La DRAM y otras memorias conectan las líneas de datos correspondientes a los pines correspondientes del STM32, la función del pin se establece en el modo de multiplexación y, al configurar el FSMC, puede asignar directamente la dirección fija anterior y otras operaciones STM32 Se realizará automáticamente para usted, ¡y puede almacenar los datos en SRAM!

Echemos un vistazo al proceso de lectura y escritura de datos usando FSMC:

Definir la dirección correspondiente a la línea de datos FSMC

//FSMC_Bank1_NORSRAM

#define FSMC_Addr_DATA ( ( uint32_t ) 0x60020000 )

Si desea escribir datos, puede asignar directamente un valor a esta dirección:

/**

* @brief SRAM写入数据

* @param usData :要写入的数据

* @retval 无

*/

void SRAM_Write_Data ( uint16_t usData )

{

* ( __IO uint16_t * ) ( FSMC_Addr_DATA ) = usData;

}

Si desea leer datos de la memoria, simplemente lea esta dirección directamente:

/**

* @brief 从SRAM读取数据

* @param 无

* @retval 读取到的数据

*/

uint16_t SRAM_Read_Data ( void )

{

return ( * ( __IO uint16_t * ) ( FSMC_Addr_DATA ) );

}

uint16_t usR=0;

usR = SRAM_Read_Data (); /* READ DATA*/

¿Es una operación tonta, que facilita enormemente nuestra programación? De hecho, es como el software IIC SPI y el hardware IIC SPI. No necesitamos preocuparnos por el tiempo del protocolo en sí. Estos son configurados internamente por STM32. Solo necesitamos enviar y leer los datos, STM32 se comunica con la memoria externa, usando el método de hardware es FMC, por lo que es fácil de entender

Entonces, después de que comprenda qué es FSMC, le explicaremos en detalle: ¿Cómo se configura en STM32 y qué características tiene? A continuación te los explicamos uno por uno.

Los chips de la serie STM32F1 no admiten SDRAM extendida (compatibilidad con STM32F4 y H7), solo admiten el uso de periféricos FSMC para expandir SRAM, debido a la limitación de la cantidad de pines, solo los chips STM32F103ZE o superiores pueden expandir SRAM externa

Diagrama de bloques de FSMC

El diagrama de bloques de FSMC se muestra en la figura:

El FSMC de F1 consta de cuatro módulos principales: bus AHB (incluido el registro de configuración de FSMC), reloj HCLK, controlador PSRAM y flash NOR, controlador de tarjeta PC y flash NAND;

Descripción del pin FMC

1. En el lado derecho del diagrama de bloques están los pines de control relacionados con los periféricos FSMC. Al controlar diferentes tipos de memoria, habrá algunos pines diferentes. La línea de dirección FSMC_A y la línea de datos FSMC_D son compartidas por todos los controladores.

Señal NOR/SRAM: Esta parte es la señal de control de la memoria como NOR y SRAM, donde:

- FSMC_CLK es la señal del reloj

- FSMC_NE[4:0] es la señal de selección de chip para seleccionar diferentes áreas de almacenamiento de SRAM

- FSMC_NBL[1:0] es la máscara de datos

- FSMC_NL es si la dirección de entrada es válida

Junto con las siguientes señales comunes, se forman los pines de control de la SRAM:

Asignación de direcciones FMC

2. Después de que FSMC se conecta a la memoria externa y se inicializa, puede leer y escribir datos directamente accediendo a la dirección.Esta parte tiene una dirección de almacenamiento fija en la memoria, y la unidad de almacenamiento se asigna al espacio de direccionamiento interno de STM32 ; en el programa, defina un puntero a estas direcciones, y luego puede modificar directamente el contenido de la unidad de almacenamiento a través del puntero.El periférico FSMC completará automáticamente el proceso de acceso a datos, y las operaciones como los comandos de lectura y escritura no requieren programa controlar, de la siguiente manera:

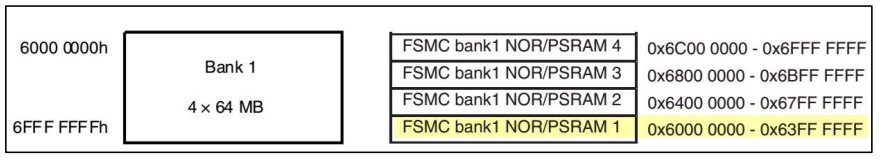

Es decir, el espacio de 1,0 GB de 0x6000 0000 a 0x9FFF FFFF se usa como la dirección de la FMC

Si observa el núcleo, el lado izquierdo es la asignación de espacio de almacenamiento del núcleo Cortex-M3, y el lado derecho es el mapa de direcciones del periférico STM32 FSMC. Se puede ver que las direcciones de NOR/PSRAM/SRAM/NAND FLASH y la tarjeta PC de FSMC están en el espacio de direcciones de la RAM externa. Es precisamente debido a la existencia de tal mapeo de direcciones que acceder a la memoria controlada por el FSMC es lo mismo que acceder a los registros periféricos en el chip del STM32 (el mapeo de direcciones de los periféricos en el chip es el área "Periférico" a la izquierda en la figura)

Es decir, acceder a FSMC es en realidad acceder a una dirección fija, que es similar a la operación de registro.

FSMC divide toda el área de almacenamiento en 4 áreas de banco. Las memorias NOR y SRAM solo pueden usar la dirección del banco 1. Cada banco está dividido en 4 bloques pequeños, y cada bloque pequeño tiene pines de control correspondientes para la conexión. Señal de selección de chip FSMC_NE1/2 /3/4

Cuando STM32 accede al espacio de direcciones 0x6C000000-0x6FFFFFFF, en realidad está accediendo a la primera área de FSMC BANK1

, el pin FSMC_NE1 se establecerá automáticamente en un nivel bajo

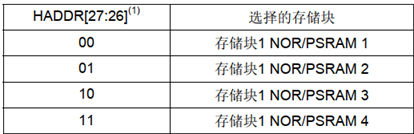

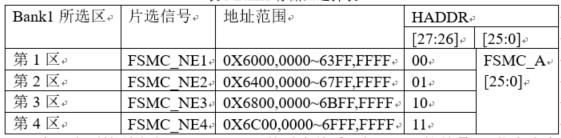

Específicamente, se selecciona el pequeño ayuno, que está determinado por el direccionamiento de la línea de dirección (ADDR[27:26])

El espacio de bytes de 256M de Bank1 está 28根地址线direccionado por (ADDR[27:0]) . Aquí ADDR es el bus de direcciones AHB interno, que ADDR[25:0]corresponde a la dirección de la memoria externa FSMC_A[25:0], y HADDR[26:27] se dirige a 4 áreas

Es decir, los primeros dos bits de la línea de dirección de 28 bits ADDR son para seleccionar esa partición, y los últimos 26 bits son para seleccionar la dirección de byte de 64M correspondiente.

Las cuatro áreas corresponden a binario:

Banco1 : 0110-0000 0000-0000 0000-0000 0000-0000, es decir, 60 00 00 00;

Banco2 : 0110-0100 0000-0000 0000-0000 0000-0000, es decir, 64 00 00 00;

Banco3 : 0110-1000 0000-0000 0000-0000 0000-0000, es decir, 68 00 00 00;

Bank4: 0110-1100 0000-0000 0000-0000 0000-0000, es decir, 6c 00 00 00;

Operación de ancho de bit diferente de FSMC

Además del FSMC_A[25:0] multiplexado a los pines específicos, el bus FSMC tiene un total de 26 direcciones y hay dos buses internos ADDR[27:26]. A través de estas dos rutas se distinguen FMC_NE1, FMC_NE2, FMC_NE3 y FMC_NE4. es decir, 0x60xx xxxx, 0x64xx xxxx, 0x68xx xxx y 0x6Cxx xxxx.

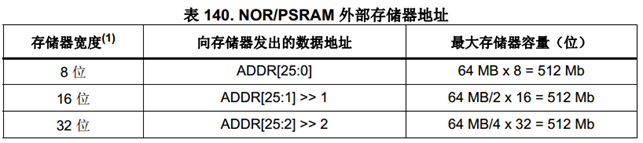

Cabe señalar aquí que cada dirección en el FSMC corresponde a un byte en la memoria

Supongamos que usamos el área 1 de BANK1, entonces 0x6000 0000-0x63ff ffff (un total de 64M bytes byte address) corresponde a la dirección de la memoria es 64Mx8=512M address

Es decir, la dirección de 64 MB de bits de la FSMC asigna la dirección de 64 MB de bytes de la memoria.

Es decir, por defecto, los datos de la dirección de la memoria son de 8 bits, que se pueden leer normalmente, pero si los datos de la dirección de la memoria son de 16 bits, 32 bits, es decir, dos bytes una dirección, cuatro bytes una dirección, entonces controle 16 bits , los dispositivos de almacenamiento de 32 bits de ancho que no admiten el acceso de un solo byte son más problemáticos. Por ejemplo, NOR Flash con un ancho de 16 bits solo admite escritura de 16 o 32 bits (escribiendo 16 bits dos veces) y no admite la escritura de datos de 8 bits.

En este caso, nuestra dirección de byte original correspondiente a 64M se convierte en una dirección de byte de doble byte de 32M, es decir, el último bit no es válido porque la dirección debe incrementarse en 2 a la vez.

En este momento, para facilitar la operación, FMC proporciona una solución en el diseño del hardware.Después de configurar el bus de datos interno ADDR[25:0], se conecta al pin de dirección FMC_A y el bit-0 del la dirección se "descartó". Cuente la dirección desde el bit 1 (equivalente a contar solo direcciones pares, hay 32 millones de direcciones en total)

Cuando la FSMC realmente genera la dirección, desplaza el valor de la dirección un bit hacia la derecha (equivalente a dividir por 2, lo que se convierte en una dirección par) y lo genera en la línea de dirección real. La documentación F103 dice esto:

Si el ancho de la memoria es de 32 bits, es una dirección de 4 bytes, que son dos bits desplazados hacia la derecha.

Finalmente, el ancho de la memoria externa está configurado para ser de 16 bits y el FMC utilizará la dirección interna ADDR[25:1] como la dirección de direccionamiento FMC_A[24:0] para la memoria externa. Si el ancho de la memoria es de 32 bits, el FMC utilizará la dirección interna ADDR[25:2] para el direccionamiento externo

registro FSMC

En la tercera parte de la figura anterior, el registro de configuración de control de bus AHB establece el FSMC,

Los dispositivos NOR/PSRAM/SRAM usan el mismo controlador, los dispositivos de tarjeta NAND/PC usan el mismo controlador y diferentes controladores tienen registros dedicados para configurar sus modos de operación.

- Control NOR FLASH con registro de control FSMC_BCR1/2/3/4, registro de sincronización de selección de chip FSMC_BTR1/2/3/4 y registro de sincronización de escritura FSMC_BWTR1/2/3/4.

Hay 4 registros de cada tipo, correspondientes a 4 áreas de almacenamiento diferentes.Los distintos registros se describen a continuación:

- El registro de control FSMC_BCR configura el tipo de memoria que se controlará, el ancho de la línea de datos y los parámetros de polaridad válida de la señal.

- El registro de temporización FMC_BTR se utiliza para configurar varios retrasos de tiempo durante el acceso a SRAM, como el tiempo de retención de datos, el tiempo de retención de direcciones, etc.

- El registro de tiempo de escritura FMC_BWTR es similar a los parámetros controlados por el registro FMC_BTR, se usa especialmente para controlar los parámetros de tiempo del tiempo de escritura.

reloj FSMC

El periférico FSMC está montado en el bus AHB, la señal de reloj proviene de HCLK (72 MHz por defecto) y la salida de reloj síncrono del controlador se obtiene dividiéndola.

Su frecuencia de reloj se puede configurar a través del bit CLKDIV del registro FSMC_BTR El factor de división de frecuencia (CLKDIV) de HCLK y FSMC_CLK se puede dividir entre 2 y 16.

-

Se puede utilizar para la comunicación síncrona con el chip NOR FLASH de tipo síncrono a través de la salida de pin FSMC_CLK ,

-

Para las memorias de tipo asíncrono , no se utiliza ninguna señal de reloj síncrono, por lo que la configuración del divisor de reloj no funciona.

Cuatro modos de FSMC

Para la memoria, se puede dividir en con reloj 同步存储器y sin reloj.异步存储器

- Latencia (DATLAT) requerida para obtener los primeros datos en un acceso de ráfaga síncrono

- En el modo de acceso de ráfaga asíncrono, FSMC establece principalmente tres parámetros de tiempo: tiempo de configuración de dirección (ADDSET), tiempo de configuración de datos (DATAST) y tiempo de retención de dirección (ADDHLD).

El periférico FSMC admite una variedad de tiempos diferentes para controlar diferentes memorias , sintetiza las características de la señal de los productos SRAM/ROM, PSRAM y NOR Flash, y define cuatro modelos de tiempo asíncronos diferentes de ABCD . Al elegir diferentes modelos de tiempo, debe establecer diferentes parámetros de tiempo

Configuración de parámetros FSMC

Sabemos que la memoria como NOR FLASH y SRAM tienen otras líneas de control además de la línea de dirección y la línea de datos 读写时序. En STM32, estos tiempos son muy cuidadosos y nos brindan un método de configuración que puede coincidir con diferentes tipos de memoria.

Echemos un vistazo a los diagramas de tiempo de los diferentes modos y veamos el proceso específico de FSMC a través del diagrama de tiempo:

Modo de operación de lectura 1

-

NOE es la línea de señal de lectura de la memoria , N significa activo bajo, O significa salida, E significa habilitar,

-

NWE es la línea de señal de escritura de la memoria , N significa activo bajo, W significa escribir, E significa habilitar,

Al escribir en la memoria, use NWE para generar un nivel bajo y NOE mantenga un nivel alto. Al leer la memoria, use NOE para generar un nivel bajo y NWE mantenga un nivel alto.

Operación de escritura en modo 1

La diferencia entre el modo A y el modo 1 es el cambio de NOE y el tiempo de lectura y escritura independiente

FSMC controla el tiempo de NOR FLASH asíncrono

A continuación, explicaremos el modo B utilizado para controlar NOR FLASH asíncrono.

Diagrama de tiempo de la lectura FSMC NOR FLASH:

Tomando el tiempo de lectura como ejemplo, la figura muestra que un ciclo de lectura de memoria consta de 地址建立周期(ADDSET), y数据建立周期(DATAST) .2 个 HCLK 周期

- En el ciclo de establecimiento de dirección, la línea de dirección envía la dirección a la que se debe acceder, la línea de señal de máscara de datos indica las partes de byte alto y bajo de la dirección que se va a leer, y la señal de selección de chip habilita el chip de memoria;

- Una vez que finaliza el ciclo de establecimiento de la dirección, la línea de señal de habilitación de lectura envía una señal de habilitación de lectura, y luego la memoria transfiere los datos de destino

a la FSMC a través de la línea de señal de datos, y la FSMC los entrega al núcleo

Diagrama de tiempo de escritura NOR FLASH de FSMC:

El tiempo de escritura es similar, la diferencia es que un ciclo de operación de memoria solo se compone de un ciclo de configuración de dirección (ADDSET) y un ciclo de configuración de datos (DATAST

), y la línea de señal de habilitación de escritura envía una señal de escritura durante el ciclo de configuración de datos, y luego el FSMC envía los

datos a través de la línea de datos a la memoria.

Cuando el periférico FSMC está configurado para funcionar normalmente y el NOR FLASH está conectado externamente, si los datos se escriben en la dirección 0x60000000 como 0xABCD, el FSMC generará automáticamente la señal de nivel correspondiente en cada línea de señal para escribir los datos. El FSMC controlará la señal de selección de chip NE1 para emitir un nivel bajo para seleccionar el chip NOR correspondiente, y luego usará la línea de dirección A[25:0] para generar 0x60000000, y emitirá una señal de habilitación de escritura de bajo nivel en la escritura NWE. habilita la línea de señal La señal de datos escritos 0xABCD sale de la línea de datos D[15:0], y luego los datos se almacenan en NOR FLASH.

Características de FSMC

Resumen de funciones de FSMC: Convierta la señal de transmisión AHB al protocolo de dispositivo externo apropiado; cumpla con los requisitos de tiempo para acceder a dispositivos externos.

Todas las memorias externas comparten la dirección, los datos y las señales de control emitidas por el controlador, y cada dispositivo externo puede distinguirse por una señal de selección de chip única. El FSMC accede solo a un dispositivo externo a la vez.

Características de FSMC

1. Una característica importante de FSMC es que admite operaciones de lectura y escritura asincrónicas de diferentes anchos de bit.

2. En el espacio de direcciones mapeado de FSMC, diferentes bancos son independientes y se pueden usar para expandir diferentes tipos de memoria. Cuando la FSMC usa varias memorias externas al mismo tiempo, la FSMC usará el parámetro de tiempo de demora de suspensión del bus para evitar conflictos de acceso.

3. Código de soporte para ejecutar directamente desde la memoria externa extendida por FSMC. No es necesario cargar primero en la SRAM interna.

El principio básico de FSMC está aquí. En el próximo artículo, explicaremos cómo usar la biblioteca HAL para inicializar FSMC.