Notas de estudio de diseño de circuitos integrados digitales

4. Verilog implementa un contador BCD

1 原理图

2 Verilog 代码

3 Modelsim仿真

- Código BCD: decimal codificado en binario, un número decimal codificado en binario, es un código numérico decimal que utiliza un número binario de 4 dígitos para representar uno de los dígitos 0-9 en el número decimal. La codificación BCD se puede dividir en dos tipos: código autorizado y código no autorizado. Los códigos autorizados son como el código 8421, el código 5421 y el código 2421, y los códigos no autorizados son como los 3 códigos restantes, los códigos Gray y los 3 códigos cíclicos restantes.

- El código BCD más comúnmente utilizado es el código 8421. Los pesos de cada bit son 8d, 4d, 2d y 1d. De manera similar, los pesos de cada bit del código 5421 son 5d, 4d, 2d y 1d. La característica del código 5421 es que el bit más alto tiene 5 0s consecutivos y luego 5 consecutivos. Por lo tanto, cuando el contador adopta este código, el bit más alto puede generar una salida de onda cuadrada simétrica; los 3 códigos restantes se obtienen sumando 0011b al código 8421; La característica del código Gray es que dos códigos adyacentes tienen solo un número binario diferente, y el formato de codificación no es único; los 3 códigos cíclicos restantes tienen las características de los códigos Gray y el comienzo y el final del El código se puede conectar al bucle, de modo que el registro de desplazamiento de retroalimentación se puede utilizar para la realización, implementación de hardware simple.

- Una de las principales aplicaciones del código BCD es el tubo nixie. Suponiendo que se muestre el número decimal 158, la solución general es dividir el número, decenas, centenas y miles del número decimal que debe mostrarse, es decir, divida 158 en 1, 5, 8, y luego averigüe el código de segmento de la pantalla del tubo digital correspondiente y envíelo al puerto IO conectado al tubo digital. En este proceso, se pueden realizar las siguientes operaciones: primero dividir por 158/100 = 1 para obtener el lugar de las centenas, luego tomar el resto 158% 100 = 58 y luego continuar con la operación de división 58/10 = 5 para obtener las decenas lugar, y luego tome el resto nuevamente 158% 10 = 8, obtenga el lugar de las unidades. Puede verse en el proceso anterior que la división es necesaria, pero debido a que la operación de división consume más tiempo de cálculo, el ciclo de instrucción general requerido es demasiado largo. Pero si primero se convierte a código BCD, el tiempo de cálculo se puede reducir considerablemente.

1. Esquemático

2 código Verilog

//----TOP module--------------------------

module BCD_counter_top(

input clk,

input rst_n,

input cin,

output cout,

output [11:0] q

);

wire cout3_0;

wire cout7_4;

BCD_counter uut3_0(

.clk(clk),

.cin(cin),

.rst_n(rst_n),

.cout(cout3_0),

.q(q[3:0])

);

BCD_counter uut7_4(

.clk(clk),

.cin(cout3_0),

.rst_n(rst_n),

.cout(cout7_4),

.q(q[7:4])

);

BCD_counter uut11_8(

.clk(clk),

.cin(cout7_4),

.rst_n(rst_n),

.cout(cout),

.q(q[11:8])

);

endmodule

//----BCD_counter------------------

module BCD_counter(

input clk,

input rst_n,

input cin,

output cout,

output [3:0] q

);

reg [3:0] cnt;

//----cnt-------------------------------

always@(posedge clk or negedge rst_n)

if(!rst_n)

cnt <= 4'd0;

else if(cin == 1)begin

if(cnt == 4'd9)

cnt <= 4'd0;

else

cnt <= cnt + 4'd1;

end else

cnt <= cnt;

//----cout-------------------------------

// always@(posedge clk or negedge rst_n)

// if(!rst_n)

// cout <= 0;

// else if(cin ==1 )begin

// if(cnt == 4'd9)

// cout <= 1;

// else

// cout <= cout;

// end else

// cout <= 0;

assign cout = (cin ==1 && cnt == 4'd9)? 1'b1:1'b0;

assign q = cnt;

endmodule

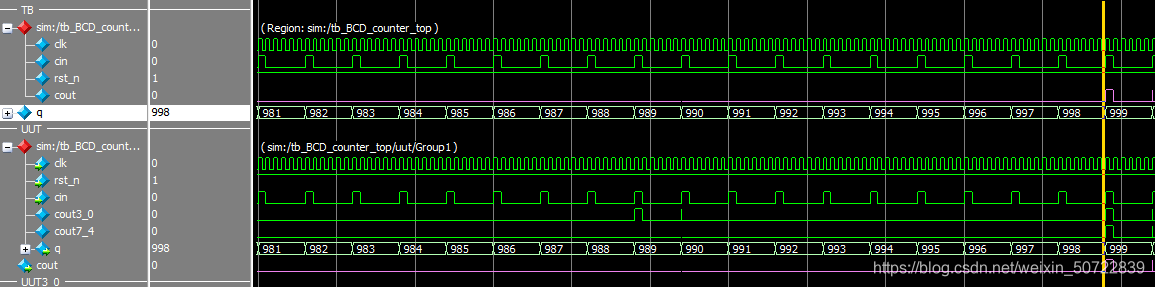

3 Simulación de Modelsim

parte del contenido transferido de las notas de autoaprendizaje de Xiaomei Ge FPGA ^^

[Nota]: notas de estudio personal, si hay errores, no dude en aclararme, esto es cortés ~~~