breve introducción

ug585

controlador Zynq UART está en un transceptor asíncrona dúplex completo que soporta una variedad de velocidades de transmisión programables y formato de señal de I / O, puede generar automáticamente una paridad, para apoyar la detección modo multi-maestro.

configuración y operación UART es controlado por un registro de modo.

El uso de rutas de datos separadas Tx y Rx, cada ruta de acceso contiene un 64-byte FIFO. El controlador de los datos en la operación de conversión Rx FIFO y Tx-paralelo, hay un conmutador de modo que soporta varios señal RxD y TxD configuración de bucle.

FIFO indicador de interrupción en apoyo del proceso de votación o proceso de interrupción accionado de dos maneras.

Programamos para leer y escribir datos de bytes de datos de registros de puerto Rx y Tx.

Zynq tiene dos controlador UART interno, UART0 y UART1, son capaces de la siguiente:

- generador de velocidad en baudios programable;

- 64-byte recibir y transmitir la FIFO;

- protocolo programable de serie, 6,7, bits de datos de 8 bits; 1, bit de parada 1,5-bit; paridad impar, paridad par, sin paridad y similares;

- detección de paridad, la detección de error de trama, la detección de error de desbordamiento;

- Generación de un salto de línea;

- La generación de una interrupción;

- RxD y TxD modo, el selector de modo para seleccionar Normal, eco o de bucle de retorno de diagnóstico;

- El bucle UART0 y UART1;

- señales de control del módem CTS, RTS, DSR, DTR, RI y DCD, EMIO sólo está disponible en la interfaz.

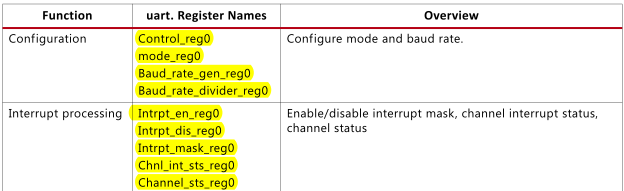

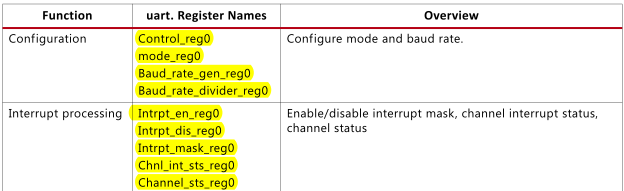

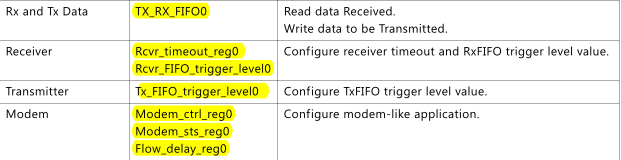

Descripción funcional

Y la lógica de control de interrupciones

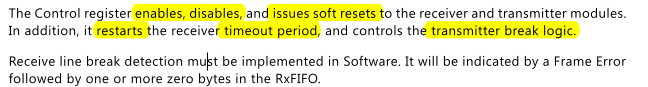

registro de control

interrupción

Chnl_int_sts_reg0

Channel_sts_reg0: sólo lectura

modo de registro

Seleccione el reloj de generación de velocidad de transmisión

Bit-anchura, bits de parada, bits de paridad

Modo de selección

uart.mode_reg0 [CHMODE]

- Modo Normal: Este es el modo de funcionamiento estándar UART, TxD y RxD Hay caminos separados.

- modo de eco automática: el modo de eco todavía reciben datos sobre RxD, pero el conmutador de modo para enrutar los datos a un receptor y TxD pasadores, el controlador no se pueden utilizar para transmisor de datos de transmisión.

- Modo de bucle de retorno local: Este modo no está conectado a la señal interna RxD y TxD, los datos se transmiten al receptor en el bucle.

- Remota modo bucle cerrado: Este modo está conectado a la RxD TxD, el controlador no puede enviar nada a TxD, cualquier contenido puede no ser recibida en la RxD.

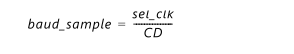

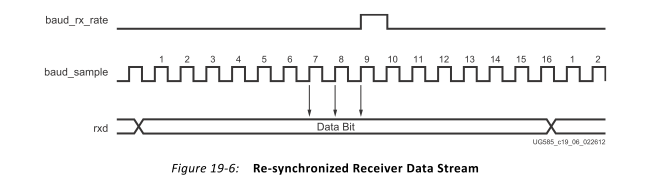

generador de la velocidad de transmisión

sel_clk ->

- velocidad de transmisión Rx

- velocidad de transmisión Tx

- Band Muestra

el registro de la velocidad en baudios Generador ((uart.Baud_rate_gen_reg0) 1 ~ 65 535

el registro de la velocidad en baudios del divisor (uart.Baud_rate_divider_reg0). 4 ~ 255,复位值15

9600 = 50 m / (651 * 8)

Enviar datos

Dejar que la carga escribiendo datos en el valor de registro a la TXFIFO TXFIFO en.

TXFIFO libre de la insignia, FIFO de datos no válidos en este indicador.

Cuando TXFIFO entrar en estado completamente interrumpida (TFULL), que indica que el FIFO está lleno. Hasta entonces realizar una operación de escritura, se disparará el desbordamiento, los datos no se carga en el TXFIFO.

TXFIFO bandera casi lleno (TNFULL) representa sólo un byte FIFO espacio libre. Podemos establecer el umbral de disparo (TTRIG), cuando el byte FIFO lograr esto desencadenará TTRIG (se muestra a continuación sección).

Y recibir la captura de datos FIFO

RXFIFO almacenar los datos serie recibidos recibidos del registro de desplazamiento. RXFIFO también tiene una función similar con TXFIFO bandera vacía, RFUL estado completamente interrumpido, disparadores de umbral RTRIG. Varios indicador de interrupción y como una sección esquemática reg.

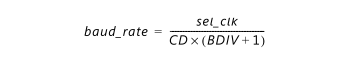

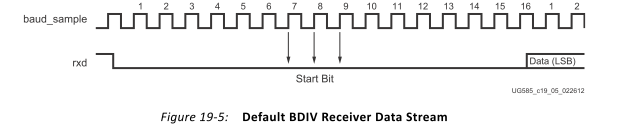

Tras la recepción, UART constantemente en la señal RxD es sobremuestreada, cuando se toman muestras de una mayor a menor transición se detecta, lo puso como el inicio del bit de inicio. En los ciclos de reloj media baudios, y luego tres muestras, si todavía baja, creo que esto es un bit de inicio válida.

Después de determinar un bit de inicio válida, la velocidad de transmisión de reloj de resincronización del receptor para la muestra (para evitar resbalones) de la señal de entrada RxD en la posición central de cada uno, como un esquema en la figura. Si usted ha escrito los procedimientos de transceptor Verilog UART, este enfoque no debe ser desconocido.

Cuando el valor determinado de una serie de datos de bits, que se transfiere a la recepción del registro de desplazamiento. Una vez montado un carácter completo, el contenido del registro de desplazamiento es empujado a RXFIFO en.

detección de errores Receptor

UART controlador ofrece cuatro error mecanismo de detección.

- Error de paridad. Cuando cada recepción de un carácter, el receptor calcula el valor de paridad de los bits de datos recibidos de acuerdo UART, se compara con los bits de paridad recibidos. Si los valores son diferentes, la bandera de error de paridad es 1, y genera una interrupción.

- error de trama. Cuando el receptor no recibe un bit de parada válido en el final de una trama, la bandera de error de trama se establece y se genera una interrupción.

- error de desbordamiento. Cuando se recibe un carácter, un controlador de UART RXFIFO detecta si hay espacio. Si existe el carácter escrito RXFIFO; si RXFIFO llena de espera; si se detecta el bit de inicio de la siguiente datos y RXFIFO todavía está lleno, a continuación, esperar a que los datos se perderán, mientras que el indicador de desbordamiento es 1, de producción de interrumpido.

- mecanismo de tiempo de espera. El receptor dispone de un contador descendente 10, cada vez que se recibe un nuevo bit de inicio o un programa en la escritura RxD de bandera especial el bit 1 se pone a cero y el contador de cuenta atrás se volverá a cargar. Cuando el contador llega a 0 hallazgos se produce tiempo de espera, el bit de bandera correspondiente (en este caso el contador de programa para poner a cero), se genera una interrupción.

Cuatro de interrupción descrita anteriormente no son necesarios, podemos proteger estas interrupciones también puede desactivar el mecanismo de tiempo de espera.

Uart.Chnl_int_sts_reg0 correspondiente a la [PARE]. [MARCO]. [ROVR] [RSTTO] Bit

programación Modelo

Si nuestra demanda es sólo una impresión en serie alguna información de depuración, a continuación, utilizar directamente o función xil_printf printf es suficiente, sin tener que realizar ninguna configuración del puerto serie. Si nos falta para completar ciertas funciones con UART, entonces es necesario para comprender el procedimiento y el diseño detallado de la UART.

1. inicio UART

secuencia de arranque UART es como sigue:

El controlador de reajuste;

configure I / O señal de enrutamiento. Rx / Tx EMIO o se pueden dirigir a MIO, se puede utilizar solamente la señal de control del módem EMIO;

configuración de reloj de referencia UART UART_Ref_Clk;

función de controlador de configuración;

interrupción de configuración, que RXFIFO y puede ser administrado mediante la interrupción de TXFIFO;

módem control de configuración ( opcional);

gestión de transmisión y recepción de datos, sondea o proceso de interrupción accionado se puede utilizar de dos maneras.

Configuración de función del controlador

Las principales funciones del controlador de configuración trama de caracteres, tasa de baudios, los niveles de activación FIFO, el mecanismo de tiempo de espera de Rx, y el controlador de capacitación. Después de reiniciar el controlador debe

configurar todos estos parámetros. Los pasos siguientes:

UART trama de caracteres de configuración, una longitud de bits de datos, paridad, bits de parada, modo / O I;

velocidad de transmisión de configuración;

proporcionado nivel de disparo RXFIFO, puede elegir activar o desactivar esta función;

permitir controlador;

receptor configurado tiempo de espera mecanismo, se puede optar por activar o desactivar la función.

3. Los datos de envío

Podemos utilizar el programa de dos formas de votación y de control de interrupción al flujo de datos TXFIFO y RXFIFO. Tanto el tamaño FIFO es de 64 bytes, por lo que cuando la bandera vacía TXFIFO efectiva, podemos escribir directamente a 64 bytes, sin comprobar el estado de TXFIFO. De hecho, cuando el transmisor está activo, el número de bytes que se pueden escribir a más de 64 bytes, puesto que el controlador también se elimina en los mismos datos de tiempo que se transfirió a la señal serializado TxD.

Un método de transmisión de datos de sondeo

El proceso es como sigue:

Compruebe TXFIFO está vacía;

datos de escritura a TXFIFO, 64 bytes se pueden escribir;

datos de escritura más. entonces podemos escribir otros vacíos TXFIFO 64 bytes, es decir, el paso 2; TXFIFO también puede detectar si hay un espacio, es decir, deja de leer y escribir bandera TFUL solo byte de datos.

Utilizando el método de interrupción de la transmisión de datos

El proceso es como sigue:

Vaciar de interrupción desactivado TXFIFO;

escribir 64 bytes de datos a TXFIFO;

detectando si hay espacio TXFIFO, deja de leer y escribir un solo dato TFUL bandera de byte;

Repita los pasos 2-3 hasta completar TXFIFO;

Habilitar TXFIFO vaciar interrupción;

espera hasta TXFIFO está vacío, entonces empezar de nuevo desde el paso;

4. Datos La recibidas

El método de proceso de recepción de datos de votación es el siguiente:

Esperar hasta que el número de datos alcanza el nivel de activación de RXFIFO;

datos leídos de la RXFIFO;

Repite el paso 2 hasta que la FIFO está vacío;

se produce Rx de tiempo de espera de interrupción se restablecerá.

El método de recepción de datos utilizando un proceso de interrupción es el siguiente:

Habilitar interrupción;

Esperar hasta que el número de datos RXFIFO alcanza un nivel de disparo o se produce un tiempo de espera;

datos leídos de la RXFIFO;

Repita los pasos 2-3 hasta que el FIFO está vacío;

que se borrará.

funciones de la biblioteca del SDK

Ref

file: /// D: /xlinx/SDK/2018.3/data/embeddedsw/XilinxProcessorIPLib/drivers/uartps_v3_7/doc/html/api/example.html

https://blog.csdn.net/FPGADesigner/article/details/ 88852990? depth_1-utm_source = distribute.pc_relevant.none tareas & utm_source = distribute.pc_relevant.none tareas

El puerto serie puede TX y RX distribución en el EMIO especificado. Tanto el M22 y P22 pasadores conectados a la cabeza CH340 o CP2012 a esta serie, hola_mundo SDK utilizadas para ejecutar a través de la rutina.

ref

https://blog.csdn.net/FPGADesigner/article/details/88805887