14-day learning training camp instructor course: Zhou Hehe "ARMv8/ARMv9 Architecture - Quick Start"

1. Types of exception handling

1.1 Interruption

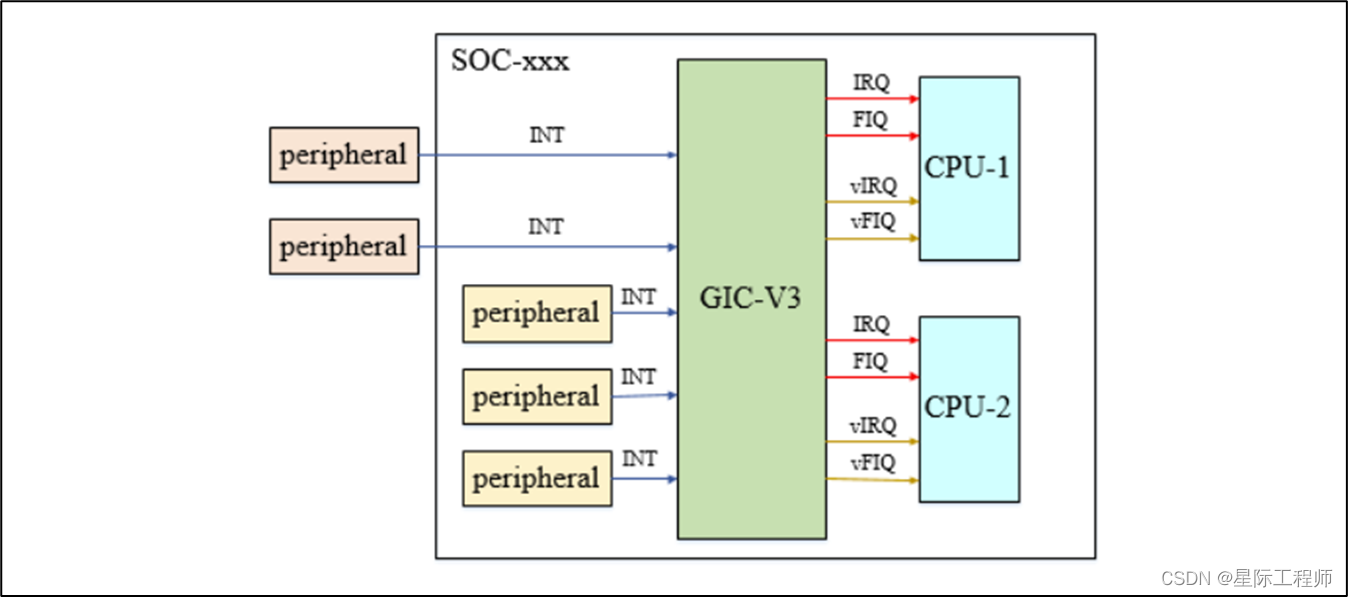

In ARM, the priority of FIQ is higher than that of IRQ. There will be an interrupt controller inside the SOC responsible for interrupt priority scheduling, and then send an interrupt signal to the processor. Interrupts are exceptions in asynchronous mode.

1.2 Cancellation

Abort exceptions are divided into data aborts and instruction aborts, and the MMU can capture errors and report them to the processor.

1.3 Reset

Reset is the highest priority exception in the processor, usually divided into power-on reset and software reset.

1.4 Abnormalities generated by the software

ARMv8 provides 3 software-generated exceptions. The reason for this exception is that the software attempts to enter a higher exception level.

SVC allows user-mode programs to request os services

HVC allows clients (Linux os) to request host services

SMC allows normal world programs to request security services

1.5 Synchronous and asynchronous exceptions

As the name suggests, a synchronous exception must wait for the CPU to finish processing the current exception before continuing to execute instructions.

Common sync exceptions:

Access to other levels of registers, such as EL1 currently, if you access EL2 registers, an exception will occur

SP unaligned

SVC, HVC, and SMC

address translation errors/address permissions

Common asynchronous exceptions:

Physical interrupts IRQ, FIQ and system errors

Virtual interrupts vIRQ, vFIQ, vSError

2. ARMv8 exception model

The description of ARMv8-a Exception level is as follows:

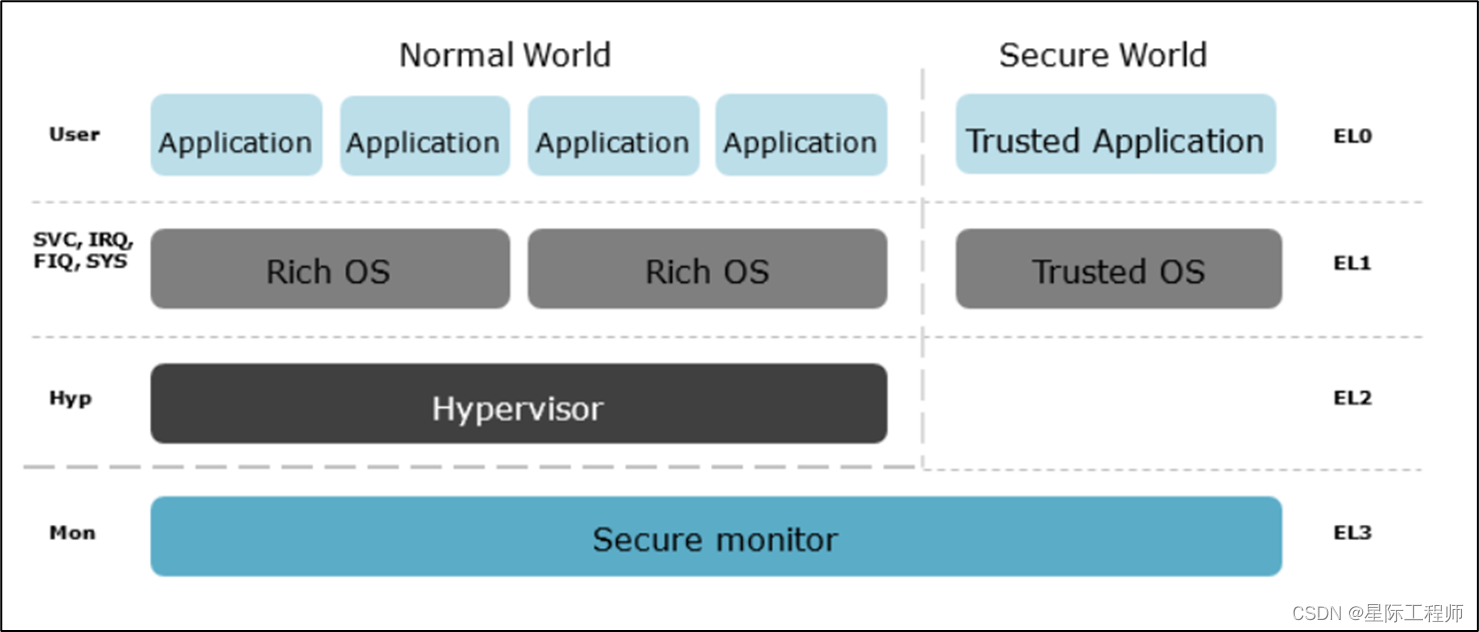

1) The first thing to note is that in AArch64, there are no concepts of processor modes such as User, SVC, and ABT, but ARMv8 needs to be forward compatible. In AArch32, these are handled The controller mode maps to 4 Exception levels.

2) Application is located at EL0 with the lowest privilege level, Guest OS (Linux kernel, window, etc.) is located at EL1, Hypervisor providing virtualization support is located at EL2 (may not be implemented), and Seurity Monitor providing security support is located at EL3 (may not be implemented).

3) Only when an exception occurs (or when the exception processing returns), the Exception level can be switched (this is also the reason for the naming of the Exception level, in order to handle the exception). When an exception occurs, there are two options, stay at the current EL, or jump to a higher EL, and the EL cannot be downgraded. Similarly, when exception processing returns, there are two options, stay at the current EL, or adjust to a lower EL.

3. GIC interrupt controller

Due to the large number of peripherals and their related interrupts in the SOC, and there are many different configuration methods for each interrupt, in order to reduce the burden on the CPU, the configuration and management of modern processor interrupts are generally implemented through the interrupt controller.

GIC is an interrupt controller launched by arm that can be used with cortex-A and cortex-R processors. There are currently four versions, namely GICv1 – GICv4. GICv3 is an interrupt controller widely used in armv8-based SOC design. The functions of GICv4 and GICv3 are basically the same, but in order to improve the performance of virtualization, the ability to directly inject virtual interrupts is added.