Article Directory

- 1. How to install

- 2. How to use

- 3. Matters needing attention

-

- Case 1: Splicing: {4{x}}

- Case 2 (regardless of ~a[0] operation): continuous & operation of bit selection expression a[0]

- Case 3 (without considering the ~a[0] operation): extend the solution of case 2

- Situation 4 (considering ~a[0] operation): No bit selection is performed on the left side, but the inversion operation is performed after the right bit selection

- Scenario 5: The ~ negation operator is used with a single bit selection expression

- Summarize:

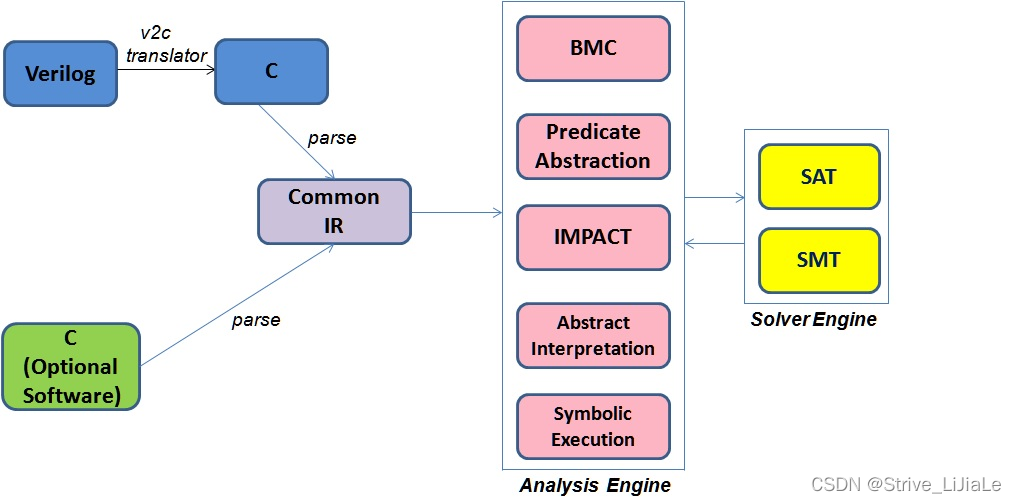

v2c is a Verilog to C translation tool. Given a register transfer level (RTL) hardware circuit description (HDL) in Verilog Hardware Description Language, it is used to automatically translate the Verilog RTL circuit into a software program expressed in C language. This software program is called a software netlist.

1. How to install

1. Download the binaries

We distribute precompiled static binaries for v2c for Linux Download binaries

2. Benchmarking

Download Benchmarks

We distribute several benchmarks in Verilog and ANSI-C for property verification, equivalence checking and simulation.

2. How to use

Application of v2c

describe

v2c is mainly used for our hardware attribute verification and is used to convert the hardware circuit given in Verilog RTL into a software program of tool flow C language. The representation of RTL circuits in software languages enables us to exploit a range of software verification techniques including abstract interpretation and path symbolic execution that have never been applied to RTL verification. It can also be used for hardware/software co-verification, equivalence checking and simulation of generated C programs.

tool flow

Working example using v2c converter

The following example illustrates the Verilog to C conversion using the tool. Designs contain sequential and combinational logic, procedural blocks, blocking and non-blocking assignments, and multiple module hierarchies. The code snippet on the left shows the Verilog RTL design and the code snippet on the right shows the C program.

Verilog C

------------------------------ ------------------------------

module top(Din,En,CLK,Dout); struct s_ff {

wire cs; reg ns; _Bool q;

input CLK, Din, En; } sff;

output Dout; struct s_en {

_Bool ns;

assign Dout = cs; struct s_ff sff;

always @(Din or cs or En) } sen;

begin

if (En) _Bool ff(_Bool CLK, _Bool Din,

ns = Din; _Bool *Dout) {

else _Bool qold;

ns = cs; qold = sen.sff.q;

end sen.sff.q = Din;

ff ff1(ns,CLK,cs); *Dout = qold;

endmodule return;

}

module ff(Din, CLK, Dout); void top(_Bool CLK, _Bool Din,

input Din, CLK; _Bool En, _Bool *Dout) {

output Dout; _Bool cs;

if(En) sen.ns = Din;

reg q; else sen.ns = cs;

assign Dout = q; ff(CLK,sen.ns,&cs);

always @(posedge CLK) *Dout = cs;

q <= Din; }

endmodule int main() {

_Bool CLK,En,Din,Dout;

while(1) {

Din = nondet_bool();

En = nondet_bool();

top(CLK,Din,En,&Dout);

}

return;

}

3. Matters needing attention

Case 1: Splicing: {4{x}}

转换结果:生成错误,乱码,不认识

解决:将简化操作展开:{x,x,x,x}

经测试,位选择拼接也可以{a[0],…}

Case 1-1 y&{x,x,x,x}

单独使用{x,x,x,x},可以正常转换,但再进行&操作,会转换成逻辑&&

Proportion 1-2 y&{x,x,x,x}&z

此时会将{x,x,x,x}转换为CONCATENATION()

位运算正常,并没有转换成逻辑运算&&

由此可见:{x,x,x,x}为最小拼接单位

Case 2 (regardless of ~a[0] operation): continuous & operation of bit selection expression a[0]

转换结果:会保留位选择表达式a[0]

解决:拆分为两个最小单元 进行 位选择&操作 ,赋值给非位选择表达式

由此可见:包含位选择a[0]时,不能进行连续&运行,将结果赋给非位选择变量

Case 3 (without considering the ~a[0] operation): extend the solution of case 2

仅有两个位选择表达式&操作时,赋值给位选择表达式

结果:产生符号“-”,经验证,此符号为减号作用,可转换

Situation 4 (considering ~a[0] operation): No bit selection is performed on the left side, but the inversion operation is performed after the right bit selection

结果:右边会保留位选择表达式

解决:右边位选择取后反操作和&操作不要同时出现,

法一:取中间变量代替位选择取反表达式(但会出现情形五问题,只能采用方法二);

法二:取中间变量代替将位操作表达式,然后将此中间变量取反后再进行&操作。

Scenario 5: The ~ negation operator is used with a single bit selection expression

结果:会忽略掉~

解决:将当个位选择表达式进行取反赋值给中间变量

Summarize:

- The left-hand expression cannot be a bit selection

- The expression bit selection on the right cannot be directly operated with "~"

It can be seen that the bit selection is the main influencing factor

so that there is no bit selection, and the result shows that the continuous & operation can be performed. Therefore, it is

further confirmed: after the bit selection operation needs to be replaced with an intermediate variable, other operations can be converted normally! ! !

In short: {} is the smallest splicing unit, a[0] is the smallest bit selection unit, both need to be replaced by intermediate variables!

Note: A one-phase AND is equivalent to a logical operation. Multi-bit AND, or bit operation.