The segment register is related to the memory addressing password of the CPU, please refer to (12 addressing modes in assembly)

As early as the 16-bit 8086CPU era, memory resources were precious, and the CPU used segmented memory addressing technology:

The addressable range of 16-bit registers is 64KB. By introducing the concept of segments, the memory space is divided into different areas: segments, addressing by segment base address + segment offset segment.

In this way, where is the base address of the segment stored? The 8086CPU specifically sets up several segment registers to store the base address of the segment. This is the origin of the segment register segment.

The segment register is also 16 bits.

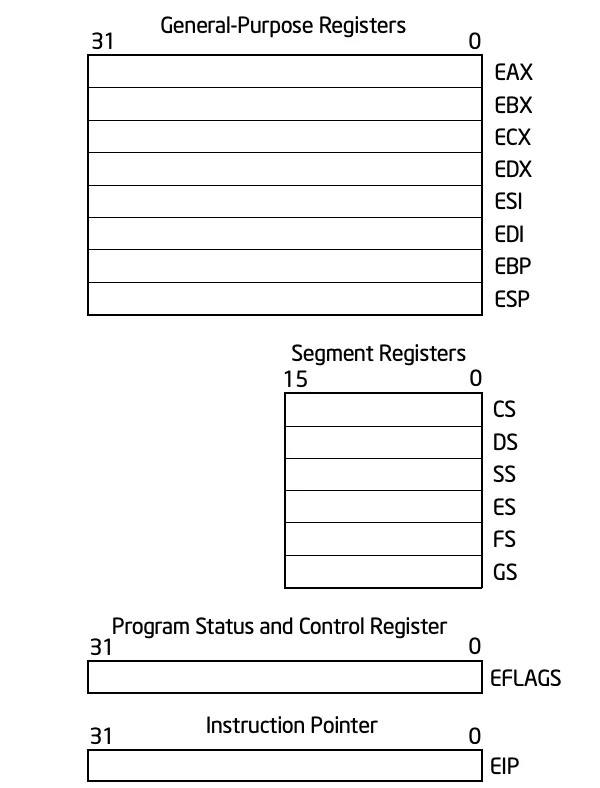

There are the following six segment registers. The first four were introduced in the early 16-bit mode. In the 32-bit era, two segment registers, fs and gs, were added.

cs : code snippet

ds : data segment

ss : stack segment

es : extended segment

fs : data segment

gs : data segment

The content stored in the segment register is closely related to the current memory addressing mode of the CPU.

When the CPU is in the 16-bit real address mode, the segment register stores the base address of the segment. When addressing, shift the content of the segment register 4 bits to the left (multiply by 16) to get the segment base address + the offset within the segment to get the final address.

When the CPU is working in protected mode, the content stored in the segment register is no longer the segment base address. At this time, the segment register stores the segment selector , which is used to indicate which segment the current segment register "points to".

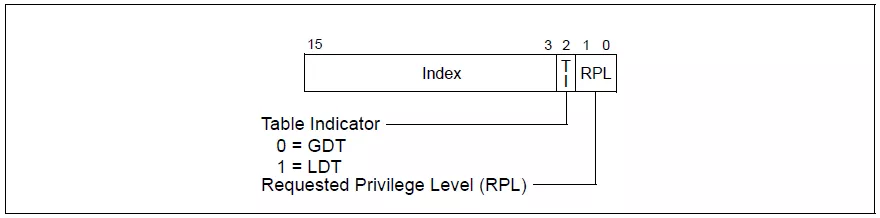

Note that I put quotation marks on the point here. What is stored in the segment register is not the direct address of the memory segment, but the segment selector. Its structure is as follows:

The 16-bit segment register content is divided into three fields:

PRL : The privilege request level is the four privilege levels we often call ring0-ring3.

TI : 0 means that the global descriptor table GDT is used, and 1 means that the local descriptor table LDT is used.

Index : This is the index value of an item in a table. This table is called a memory descriptor table . Each item in it describes a memory segment.

There are two tables mentioned here, the global descriptor table GDT and the local descriptor table LDT. About the introduction of these two tables, I will elaborate on the descriptor register below. You only need to know that this is the CPU supports segmented memory. The tables needed for management are placed in memory. Each item in the table is a descriptor that records information about a memory segment.

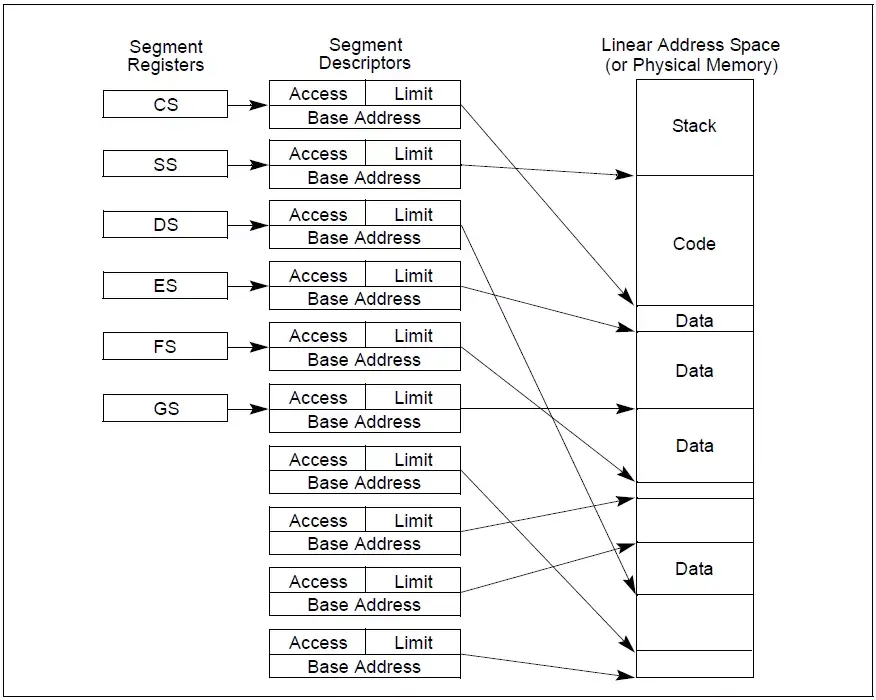

The segment registers and segment descriptors in protected mode to the last memory segment are linked together by the following figure:

General-purpose registers, segment registers, flag registers, and instruction registers. These four sets of registers together constitute a basic instruction execution environment. The context of a thread is basically these registers. When the execution thread is switched, the contents of these registers are modified. .