中断技术

中断概述

中断的流程是?

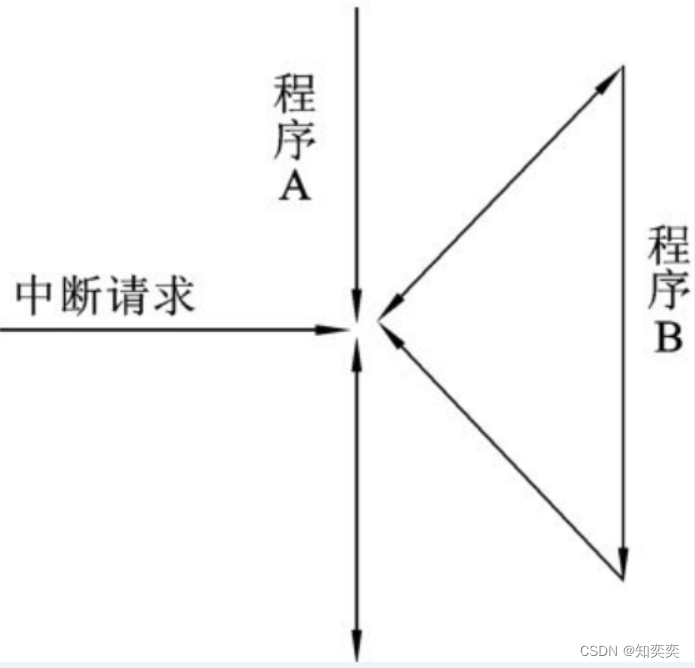

- CPU 正在执行进程 A

- 此时外部或者内部中断请求发生,CPU 响应中断

- 进程 A 暂时中断执行,转而运行中断服务程序 B

- 中断服务程序 B 运行结束,返回原来进程 A 中断的位置

- 继续执行进程 A

中断源

一种是外部中断或硬件中断,它们从 CPU 的不可屏蔽中断引脚 NMI 和可屏蔽中断引脚 INTR 引入;

另一种为内部中断或软件中断,是为解决 CPU 运行过程中出现的一些意外事件或便于程序调试而设置的

外部中断

NMI 引脚引入的中断称为不可屏蔽中断,处理紧急事件,不受中断标志 IF 影响

INTR 引脚引入的中断请求称为可屏蔽中断,只有当 CPU 的标志寄存器 FLAGS 的 IF=1 时,才允许响应此脚引入的中断请求

内部中断

内部中断不需要硬件支持,不受 IF 标志控制,不执行中断总线周期

除单步中断可通过 TF 标志允许或禁止外,其余都是不可屏蔽的中断

内部中断分类

- 除法错中断:除数为 0 时的中断

- 单步中断:TF=1 时,每执行完一条指令,就自动产生一个单步中断

- 溢出中断:溢出标志 OF=1 时,可由溢出中断指令 INTO 产生中断类型号为 4 的溢出中断

- 软件中断指令 INTn

- 断点中断:专为调试设计

中断向量表

每次中断,都会把断点和标志寄存器推入堆栈保护,之后找到中断服务程序入口地址并执行;

中断服务程序结束后,执行返回值 IRET,从堆栈恢复当前 CPU 状态与断点

中断服务程序的入口地址通常被称为中断向量(interruptvector)或中断矢量

中断向量表存放中断服务程序入口地址的段地址(CS)和地址的偏移量(IP)

中断嵌套

CPU 响应中断时,会根据优先级先响应优先级高的中断请求,后响应优先级低的中断请求

中断嵌套发生于优先级更高的中断请求打断当前中断请求,使得低优先级中断请求进入嵌套栈中的过程

机器进入中断服务程序之后,硬件会自动关闭中断,禁止别的中断进入

中断处理过程

主要由五个过程:中断请求、中断源识别(中断判优)、中断响应、中断处理和中断返回

中断请求

中断请求信号分为以下两种

- 边沿触发:CPU 根据中断请求端的电平跳变判断信号有效与否

- 电平触发:CPU 根据中断请求有无稳定电平信号判断信号有效与否

中断源识别

由于同一时间内可能有两个及以上中断源发出中断请求,CPU 必须对其进行识别并取其中一个进行中断

判优手段分为两种:软件判优、硬件判优

中断响应

要响应中断请求,需具备以下四个条件

- 一条指令执行结束

- CPU 处于开中断状态

- 当前没有发生复位(RESET)、保持(HOLD)、内部中断和非屏蔽中断请求(NMI)

- 若当前执行的指令是开中断指令(STI)和中断返回指令(IRET),则它们执行完后再执行一条指令,CPU 才能响应 INTR 请求

中断处理

中断处理由中断服务子程序完成

中断服务子程序执行以下五个步骤

- 保护软件现场

- 开中断

- 执行中断处理程序

- 关中断

- 恢复现场

中断返回

中断返回需执行中断返回指令 IRET

可编程定时器与计数器

软件定时法:设计一个延时子程序,子程序中全部指令执行时间的总和就是该子程序的延时时间

硬件定时法:利用专用的硬件定时器/计数器,在简单软件控制下产生准确的延时时间

定时器/计数器在计数方式

- 加法计数器:每有一个计数脉冲就加 1,当加到预先设定的计数值时产生一个定时信号输出

- 减法计数器:送入计数初值后,每来一个计数脉冲就减 1,减到零时产生一个定时信号输出

DMA 控制器

接下来以 DMA 控制器 8237A 作为后续内容的介绍

8237A + 8 位锁存器 = 完整的 4 通道 DMA 控制器

各个通道可以完成的动作

- DMA 读操作:读存储器送外设

- DMA 写操作:读外设写存储器

- DMA 校验操作:通道不进行数据传送操作,只是完成校验功能

8237A 结构

8237A 有两种不同的工作状态

- 丛态方式:DMA 控制器未取得总线控制权时必须由 CPU 对 DMA 控制器进行编程,这时,CPU 处于主控状态

- 主态方式:当 DMA 控制器取得总线控制权后,系统就完全在它的控制下

HRQ(总线请求信号):该信号送到 CPU 的 HOLD 端,是向 CPU 申请获得总线控制权的 DMA 请求信号

HLDA(总线响应信号):响应总线请求信号

工作方式

主控设备执行 DMA 传送时有以下 4 种数据传送方式

- 字节传送:每次 DMA 传送请求只传送一个字节的数据,数据传送后当前字节计数器自动减 1,撤销 HRQ 信号,释放系统总线控制权,并退还给 CPU

- 块传送:一旦 8237A 获得总线控制权,连续地传送一个数据块,直到当前字节计数器减为 0 或由外部产生信号时终止 DMA 传送

- 请求传送:他可以保存 DMA 现场,并且可以快速恢复

- 级联模块:当一片 8237A 通道不够使用时,可通过多片级联的方式增加 DMA 通道

工作时序

8237A 有两个主要的工作周期,即空闲周期(idlecycle)和有效周期(activecycle)

空闲周期:系统复位后或无 DMA 请求时处于空闲周期,这时 DMA 处于从态方式

有效周期:当 8237A 在 SI 状态采样到外部有效的 DMA 请求信号 DREQ 后,就向 CPU 发 DMA 请求信号 HRQ,并进入有效周期 SO 状态