ISSI IS62WV51216ALL / IS62WV51216BLL высокоскоростной 8M-битное статическое ОЗУ, организована как 512K слов на 16 бит. Он использует высокоэффективную технологию Исси в CMOS. Это очень надежный процесс в сочетании с методами проектирования инновационной цепи, может производить высокую производительность и низкие энергопотребление устройства.

Когда CS1 ВЫСОКОЕ (отсеянные) или CS2 НИЗКИЕ (отсеянный) или НИЗКИЙ CS1, CS2 ВЫСОКАЯ и LB и UB оба HIGH, устройство находится в режиме ожидания, в этом режиме, вы можете уменьшить мощность CMOS входа уровень потребления.

Используя чип включить и выходной разрешающий вход память может быть легко расширена. Активный LOW Write Enable (WE) контроля памяти записи и чтения. Разрешение доступа к байту старших байт данных (UB) и младшим байтам (LB).

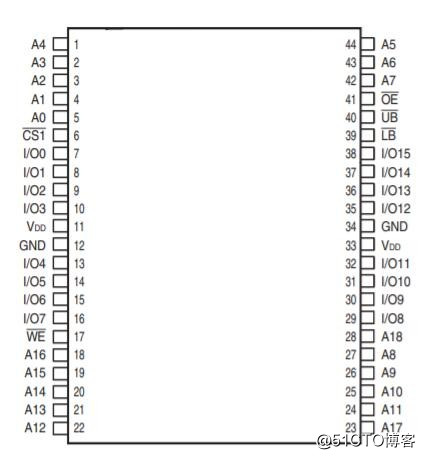

IS62WV51216ALL IS62WV51216BLL и упакованы в JEDEC стандартный 48-контактный мини BGA (7.2mmx8.7mm) и 44-контактный TSOP (тип II), в.

SRAM чипы модель IS62WV51216, булавки выглядит следующим образом :

В целом IS62WV51216 штифта грубо разделить на: линии питания, линию заземления, адресные линии, линии передачи данных, линии выбора кристалла, разрешение запись терминала, чтения дает возможность терминал и данные маски сигнальной линии.

В котором

• Высокоскоростной время доступа: 45ns, 55ns

• работа с низким энергопотреблением КМОП

-36mW (типичный) , работающий

-12μW (тип) КМОП ожидания

• Уровень TTL - совместимый интерфейс

• Один источник питания

-1,65 В - 2.2V VDD на (62WV51216ALL)

- 2.5V - 3.6V VDD на (62WV51216BLL)

• полностью статический режим: нет необходимости обновлять часы или

• выходного трехуровневых

• откусывания управления данными

• доступный промышленный температура

• Свинец