DMA — это прямой доступ к памяти.В системах FPGA существует несколько часто используемых требований DMA:

1. Внутри PL нет PS (здесь ЦП вместе именуется PS), который постоянно вмешивался бы в перемещение данных.Общими формами интерфейса являются AXIS и AXI, AXI и AXI;

2. Перемещение данных между PL и PS легче понять для ZYNQ. Он принадлежит внутреннему интерфейсу одного чипа. Для других интерфейсов, таких как PCIe, это будет немного сложнее и принадлежит интерфейсу между несколькими чипами;

Изучите цель подхода DMA:

1. Понимать методы перемещения данных внутри чипа, общие интерфейсы и методы реализации DMA;

2. Понимать методы перемещения данных между чипами, общие интерфейсы и методы реализации DMA;

Благодаря этому пониманию может быть создана структура структуры для миграции системных данных.Если возникнет подобная потребность, все, что на самом деле необходимо, — это вызвать существующие модули для ее реализации.

Эта статья начинается с введения в каждый IP-адрес DMA Xilinx, в основном с точки зрения интерфейсов.

1 AXI4 К AXI4

1.1 Центральный контроллер DMA AXI

AXI CDMA обеспечивает прямой доступ к памяти (DMA) с высокой пропускной способностью между адресом источника, отображенным в памяти, и адресом назначения, отображенным в памяти, с использованием протокола AXI4. Дополнительную функцию Scatter Gather (SG) можно использовать для разгрузки задач управления и последовательности с системного ЦП. Доступ к регистрам инициализации, состояния и управления осуществляется через подчиненный интерфейс AXI4-Lite, подходящий для процессора Xilinx MicroBlaze™.

Почему он называется CDMA? На самом деле он предназначен для обработки передачи данных в памяти интерфейса AXI, установленной на процессоре. Типичный сценарий - MicroBlaze. Почему бы не сказать ZYNQ? AXI ZYNQ монтируется непосредственно внутри процессора и не требует прямого доступа к памяти для управления. При необходимости можно выполнить прямое копирование программного обеспечения, и действие копирования инициирует внутреннюю операцию AXI DMA. Но если ZYNQ хочет использовать DDR на стороне PL, для работы он должен использовать CDMA, поскольку у ZYNQ нет интерфейса AXI Master, только SLAVE (здесь речь идет о высокопроизводительных интерфейсах HP, а не о низкоскоростных интерфейсах GP). .

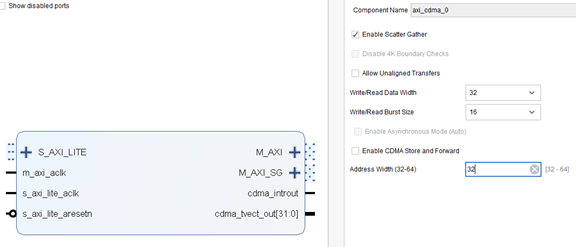

Рис. 1-1 Интерфейс AXI CDMA и параметры параметров, где S_AXI_LITE подключен к главному процессору управления, M_AXI подключен к памяти, а M_AXI_SG подключен к памяти (используется для хранения дескриптора dma в режиме SG DMA)

Рисунок 1-2 Блок-схема внутренней структуры CMDA

Рис. 1-3 Блок-схема ZYNQ, только высокопроизводительный AXI SLAVE, без MASTER

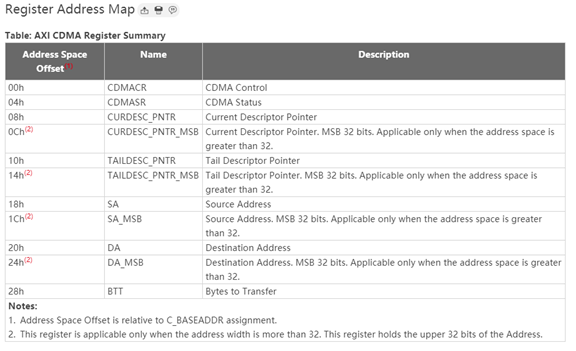

Давайте посмотрим на внутренние регистры.Это на самом деле более интуитивно понятно и подсказывает пользователю, как настроить модуль.Из метода настройки мы можем просто оценить сложность использования модуля. Из определения регистра управление, определение состояния, указатель дескриптора SG DMA, начальный адрес, целевой адрес и длина простого DMA не сложны в использовании. Затем рекомендуется использовать соответствующий программный код для прямого копирования кода драйвера стороны ZYNQ xilinx, а затем вы можете использовать его с небольшой модификацией.

Наконец, давайте посмотрим на занятость ресурса.Занятость ресурса пропорциональна разрядности.Обычно при 64-битной разрядности данных он занимает около 1500 LUT и 2500 FF.С моей точки зрения, этот ресурс довольно хорош.

Рисунок 1-4 Использование ресурсов

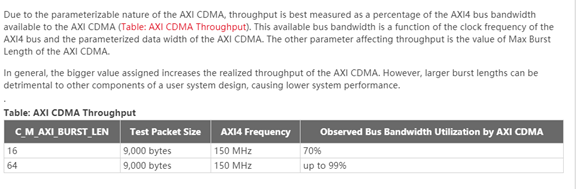

Рисунок 1-5. Эффективность передачи и полоса пропускания.

2 Поток AXI в AXI4

2.1 Перемещение данных AXI

AXI Datamover — это ключевой IP-адрес межсетевой инфраструктуры, который обеспечивает высокопроизводительную передачу данных между доменом, отображаемым в памяти AXI4, в домен AXI4-Stream. AXI Datamover обеспечивает каналы MM2S и S2MM AXI4-Stream, которые работают независимо друг от друга в полнодуплексном режиме. AXI Datamover является ключевым строительным блоком для ядра AXI DMA и обеспечивает защиту границ адресов размером 4 Кбайт, автоматическое пакетное секционирование, а также обеспечивает возможность постановки в очередь нескольких запросов на передачу, используя почти всю пропускную способность протокола AXI4-Stream. Кроме того, AXI Datamover обеспечивает перераспределение данных на уровне байтов, позволяя выполнять чтение и запись в память в любое место смещения байта.

AXI Datamover — это важный базовый IP-адрес.Все IP-адреса Xilinx DMA в основном включают этот модуль, который может конвертировать данные в форматы AXIS и AXI.

Этот модуль включает в себя почти все IP-адреса DMA, такие как XDMA, VDMA, AXI DMA, AXI MCDMA и т. д. Если существующие DMA xilinx не могут удовлетворить потребности, пользователь может самостоятельно разработать контроллер DMA для выполнения операции DMA.

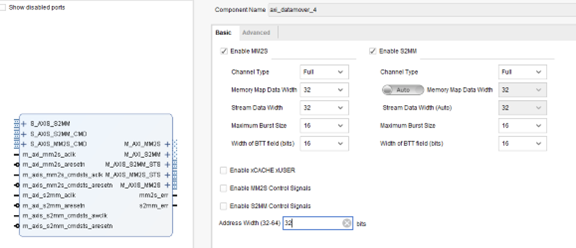

Рис. 2‑1. Интерфейс и элементы конфигурации AXI Datamover.

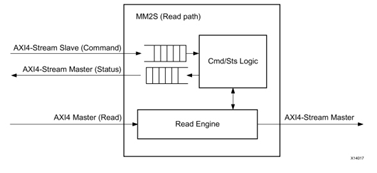

Рисунок 2-2. Канал чтения данных MM2S, считывание данных интерфейса AXI4, преобразование их в выходные данные AXIS.

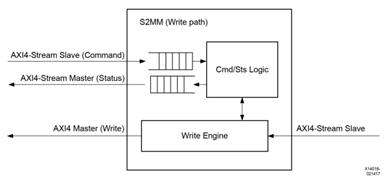

Рисунок 2‑3. Канал записи данных S2MM, ввод данных AXIS, преобразованный в данные AXI4 и записанный в память интерфейса AXI4.

Рисунок 2-4 Использование ресурсов

2.2 Контроллер AXI DMA

IP-адрес AXI Direct Memory Access (AXI DMA) обеспечивает прямой доступ к памяти с высокой пропускной способностью между памятью и целевыми периферийными устройствами типа AXI4-Stream. Его дополнительные возможности сбора данных также разгружают задачи по перемещению данных с центрального процессора (ЦП) в системах на базе процессоров. Доступ к регистрам инициализации, состояния и управления осуществляется через подчиненный интерфейс AXI4-Lite.

Короче говоря, контроллер AXI DMA обеспечивает простой способ преобразования (хранения данных) интерфейсов AXIS и AXI4 для управления программным обеспечением (через интерфейс AXI Lite).

Рисунок 2-5 Внутренняя блок-схема AXI DMA

Здесь необходимо кое-что объяснить: если вы решите не включать режим SG DMA, а использовать режим чистого управления регистрами для IP-адреса AXI DMA, использование ресурсов будет уменьшено, а производительность снизится (другие IP-адреса Xilinx DMA аналогично), почему снизится производительность? Это связано с тем, что режим регистрации не поддерживает предварительно установленные инструкции передачи и может только ждать завершения одной передачи, прежде чем начать следующую передачу, что уменьшает пропускную способность и увеличивает вмешательство ЦП. Однако этот режим также является самым простым и все еще зависит от требований к передаче, заложенных в проекте.

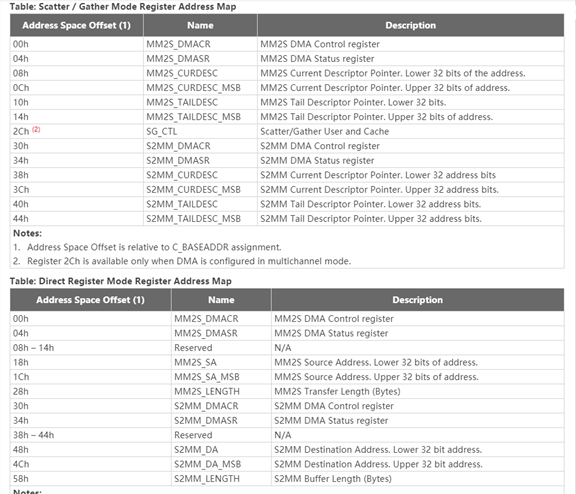

Давайте посмотрим на таблицу регистров.В таблице перечислены регистры в двух режимах: SG DMA и регистр DMA.Как видно из таблицы, на самом деле использовать AXI DMA несложно.Однако я все же рекомендую напрямую копировать код драйвера Xilinx SDK. Достаточно простого драйвера и примера, он прост, понятен и удобен в использовании.

В таблице Рисунок 2-6 показаны соответствующие регистры и их значения в режиме SG и режиме регистров.

Рисунок 2-7. С точки зрения использования ресурсов, это все еще довольно много.

Рисунок 2-8 Данные о задержке, производительности и пропускной способности. Данные о пропускной способности довольно хорошие. Вообще говоря, хорошо достичь 80%. Чтение происходит быстрее, чем запись, поэтому пропускная способность MM2S близка к 100 %, а пропускная способность S2MM составляет всего 75%.

2.3 Многоканальный DMA AXI

Проще говоря, это многоканальная версия AXI DMA. Она предназначена для многоканальной низкоскоростной передачи данных. AXI MCDMA поддерживает до 16 каналов в обоих направлениях, причем каждый канал независим друг от друга и позволяет осуществлять независимую настройку.Это обеспечивает множество низкоскоростных, многофункциональных.Приложение обеспечивает решение FPGA небольшой площади.

Поскольку AXI MCDMA является многоканальной версией AXI DMA, о ней не будет слишком много говориться.

AXI MCDMA облегчает миграцию больших данных, разгружая эту задачу встроенному процессору. Он выступает в качестве посредника между встроенной подсистемой AXI с отображением в памяти и подсистемой потоковой передачи AXI. MCDMA IP является полнодуплексным, с рассеянием и сбором и поддерживает до 16 каналов. Он может быть настроен как взвешенный циклический алгоритм или строгий приоритет.

Рисунок 2-9 Структурная блок-схема AXI MCDMA

2.4 AXI-видео DMA

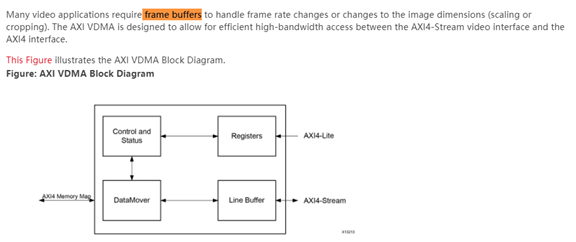

Ядро AXI Video Direct Memory Access (AXI VDMA) представляет собой программное IP-ядро Xilinx, которое обеспечивает прямой доступ к памяти с высокой пропускной способностью между памятью и целевыми периферийными видеоустройствами типа AXI4-Stream. Ядро обеспечивает эффективные двумерные операции DMA с независимыми асинхронными операциями каналов чтения и записи. Доступ к регистрам инициализации, состояния, прерываний и управления осуществляется через подчиненный интерфейс AXI4-Lite.

Зачем нам нужен AXI VDMA, если у нас есть AXI DMA? Причину можно увидеть из следующего абзаца.Обработка видео Xilinx в основном использует формат AXIS.Однако в практических приложениях существует множество потребностей в изменении частоты кадров и кэшировании кадров.Невозможно использовать AXI DMA напрямую, но это невозможно. хорошо интегрироваться с другими AXIS Видео IP интерфейса совпадает, поэтому AXI VDMA был специально разработан, в основном для кэширования кадров изображения.Друг хочет спросить, нельзя ли использовать BRAM для кэширования? Нет, потому что каждый кадр, соответствующий изображению, может быть очень большим и ресурсов BRAM недостаточно.

Использование AXI VDMA аналогично использованию других IP-адресов DMA. Никакого дальнейшего описания здесь не будет. Если вы хотите его использовать, вы можете напрямую проверить официальное руководство.

3 порта PCIe DMA

Компания Xilinx также выпустила интерфейс AXI DMA для интерфейса PCIe, который соответствует Xilinx DMA для PCIe. Аналогично другим интерфейсам, таким как USB и SRIO, пользователи также могут разрабатывать аналогичные решения DMA для создания высоконадежной и гибкой внутренней архитектуры системы. .

Xilinx® LogiCORE™ DMA для PCI Express® (PCIe) реализует высокопроизводительный настраиваемый DMA Scatter Gather для использования с интегрированным блоком PCI Express. IP обеспечивает дополнительный пользовательский интерфейс AXI4-MM или AXI4-Stream.

Рисунок 3-1 Интерфейс XDMA и элементы конфигурации параметров

Рисунок 3‑2 Внутренняя блок-схема XDMA

Так что же может сделать XDMA? Это очень много.С помощью этого модуля ваше конечное устройство PCIe может быть построено на шине AXI, и вы получите гибкую, надежную и высокопроизводительную архитектуру «система на кристалле».

4 вдохновение

Пользователи могут построить гибкую и надежную систему FPGA на основе архитектуры блок-схемы Xilinx DMA и взаимосвязанную с интерфейсами AXI и AXIS. Если эти IP-адреса не могут соответствовать требованиям, они также могут имитировать архитектуру PCIe XDMA и другие IP-адреса для создания своей собственной системы. -архитектура на кристалле.