requisitos de tempo sistema para o projeto do sinal do relógio é muito rigoroso, porque todos os nossos cálculos da série são baseados em um sinal de relógio constante como referência. No entanto, o sinal de relógio real muitas vezes não é sempre tão perfeito, haverá jitter (oscilação) e offset problema (de inclinação).

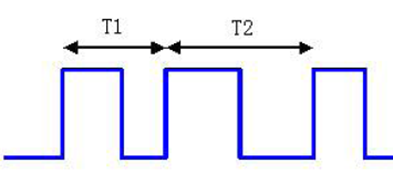

O chamado jitter (jitter), refere-se à diferença entre dois ciclos de relógio, os erros são gerados no gerador de relógio interno, e o oscilador interno ou o circuito PLL relacionado com nenhum efeito sobre a fiação. Tal como mostrado abaixo:

Além disso, uma vez que o ciclo de trabalho não é um sinal de mudança jitter causado jitter chamado meio ciclo. Em geral, jitter pode ser considerado variação soma incerto e ocasional do sinal de relógio em si algum processo de transmissão.

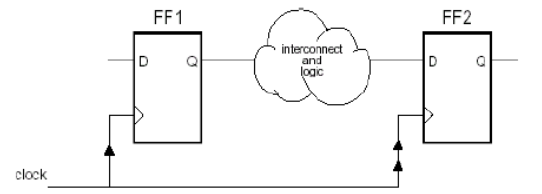

inclinação do relógio (inclinação) refere-se a uma pluralidade de sub-diferença de atraso entre os sinais de relógio gerados pelo mesmo relógio. Representa muitas formas, tanto que compreende uma pluralidade de deslocamento entre a saída do controlador de relógio, compreendendo também um deslocamento entre a extremidade de accionamento e um sinal de relógio de extremidade de recepção já que os erros causados vestígios PCB.

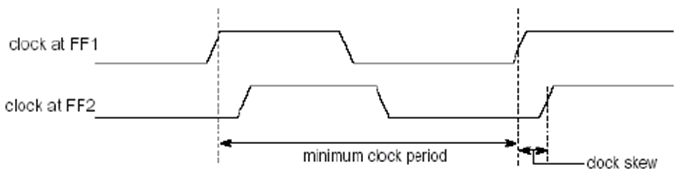

Consulte a mesma inclinação do clock um sinal de relógio diferença de tempo de chegada entre dois registros diferentes, relógio deforme sempre lá, até certo ponto, ele irá afetar seriamente o circuito de timing. Tal como mostrado abaixo:

a integridade do sinal de temporização, tais como diafonia irá afectar a linha microstrip atraso de propagação; dados de sinal de reflexão provoca flutuações perto da porta lógica limiar, afectando, assim, o tempo máximo / mínimo de voo; interferência de relógio vestígios podem causar alguns relógio de inclinação. Algum erro ou incerteza na simulação é imprevisível, o designer só para aumentar gradualmente o nível de design do sistema através da acumulação de pensamento cuidadoso e experiência prática.

A inclinação do clock e relógio jitter é o principal fator que afeta a estabilidade do sinal do relógio. Muitos livros são a partir de ângulos diferentes dentro deles explicou.

Em que a interpretação "ver" um livro dá o mais essencial:

Relógio de inclinação: A variação espacial no tempo de chegada de uma transição relógio em um circuito integrado;

jitter relógio: O vatiation temporal do período de relógio em um determinado ponto no chip;

Resumidamente, a inclinação é geralmente incerto na fase de relógio, e o jitter refere-se à incerteza (incerteza) na frequência de relógio. Causa de inclinação e jitter

Uma série de razões. Desde a fonte de clock para diferentes posições em diferentes registros experimentado caminhos de driver e de carga, as bordas do relógio varia, trazendo assim

inclinação. E razões de estabilidade, fonte de alimentação e variações de temperatura causadas pelo próprio cristal, a freqüência de clock é alterado, isto é, jitter.

Efeitos de jitter e de inclinação do circuito pode ser um modelo simples de explicar tempo. Hipótese T (CQ) representa o atraso máximo da saída registar FIG.

t (CQ, cd) representa o atraso máximo de saída; t (su) e t (hold) representam a configuração do registro, tempo de espera (para não considerar Pvt) diferença; t (lógica)

E t (lógica, cd) representam o atraso de transmissão mínima lógica de combinações atraso de propagação lógica de combinações máximo e;

No caso sem consideração de inclinação e jitter, e t (clk1) e t (clk2) mesma frequência e fase, e o período de relógio T t (hold) precisa para satisfazer

T> t (CQ) + t (lógica) + t (su)

t (hold) <t (CQ, cd) + t (lógica, cd)

De modo a assegurar o funcionamento normal do circuito, e para evitar a concorrência. Considerando fase CLK1 CLK2 mais tarde do que t1, e a inclinação = t1.

则 t (hold) <t (CQ, cd) + t (lógica, cd) - t1

Isso significa que o tempo de espera circuito violação de geração de maior tendência; consideração CLK1 CLK2 fase posterior a t2, e inclinação = t2,

则 T> t (CQ) + t (lógica) + t (su) + t2

Isto significa que o desempenho do circuito diminuiu, mas porque R2 sempre atender o tempo de espera, por isso, não há concorrência existem problemas. jitter relógio

Sempre um impacto negativo sobre o desempenho do projeto geral exige amostras especiais de cerca de margem de 10% a ser garantido.

relógio = relógio incerteza jitter + relógio de inclinação. jitter é o jitter produzido pela fonte de relógio. É a diferença de atraso da chegada de inclinação registar dois árvore relógio para o desequilíbrio. Depois cts, inclinação é calculado pela ferramenta, a incerteza relógio para sta pode ser fornecido quando um valor relativamente pequeno. Além disso, ao fazer a verificação de espera, porque o cheque é o mesmo clock, por isso não há jitter única inclinação.