DMA é acesso direto à memória. Em sistemas FPGA, existem vários requisitos de DMA comumente usados:

1. Não há PS dentro do PL (a CPU é coletivamente chamada de PS aqui) para intervir continuamente na movimentação de dados.As formas de interface comuns são AXIS e AXI, AXI e AXI;

2. Mover dados entre PL e PS é mais fácil de entender para ZYNQ. Ele pertence à interface interna de um único chip. Para outras interfaces como PCIe, será um pouco mais complicado e pertence à interface entre vários chips;

Explore o propósito da abordagem DMA:

1. Compreender os métodos de movimentação de dados dentro do chip, as interfaces comuns e métodos de implementação do DMA;

2. Compreender os métodos de movimentação de dados entre chips, interfaces comuns e métodos de implementação de DMA;

Através deste entendimento, uma estrutura de enquadramento para a migração de dados do sistema pode ser estabelecida.Se surgir uma demanda semelhante, tudo o que é realmente necessário é chamar os módulos existentes para implementá-la.

Este artigo começa com uma introdução a cada IP DMA da Xilinx, principalmente do ponto de vista das interfaces.

1 AXI4 A AXI4

1.1 Controlador Central DMA AXI

O AXI CDMA fornece acesso direto à memória (DMA) de alta largura de banda entre um endereço de origem mapeado na memória e um endereço de destino mapeado na memória usando o protocolo AXI4. Um recurso Scatter Gather (SG) opcional pode ser usado para descarregar tarefas de controle e sequenciamento da CPU do sistema. Os registros de inicialização, status e controle são acessados através de uma interface escrava AXI4-Lite, adequada para o processador Xilinx MicroBlaze™.

Por que é chamado de CDMA? Na verdade, é para lidar com a transmissão de dados dentro da memória da interface AXI montada na CPU. O cenário típico é MicroBlaze. Por que não dizer ZYNQ? O AXI do ZYNQ é montado diretamente dentro da CPU e não requer um DMA para controlá-lo. Se necessário, cópia direta do software e a ação de cópia iniciará uma operação AXI DMA internamente. Mas se o ZYNQ quiser usar DDR no lado PL, ele deve usar CDMA para operar, pois o ZYNQ não possui interface AXI Master, apenas SLAVE (aqui estamos falando de interfaces HP de alto desempenho, não de interfaces GP de baixa velocidade) .

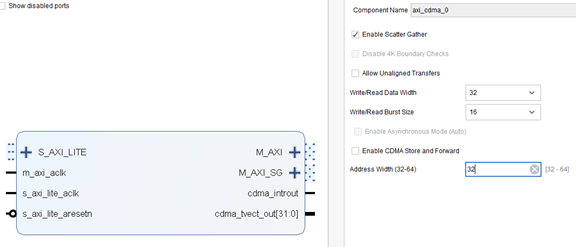

Figura 1-1 Interface AXI CDMA e opções de parâmetros, onde S_AXI_LITE está conectado à CPU de controle principal, M_AXI está conectado à memória e M_AXI_SG está conectado à memória (usado para armazenar o descritor dma no modo SG DMA)

Figura 1-2 Diagrama de blocos da estrutura interna do CMDA

Figura 1-3 Diagrama de blocos ZYNQ, apenas AXI SLAVE de alto desempenho, sem MASTER

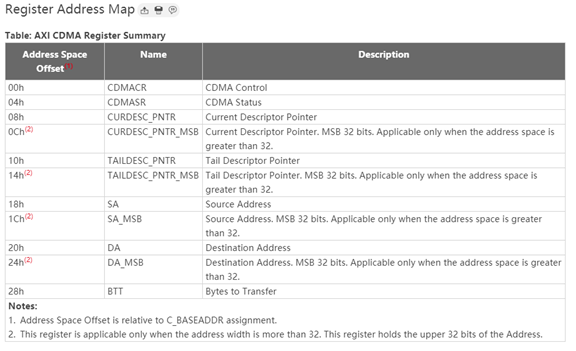

Vamos dar uma olhada nos registros internos. Na verdade, isso é mais intuitivo e informa ao usuário como configurar o módulo. A partir do método de configuração, podemos simplesmente estimar a complexidade de uso do módulo. A partir da definição do registro, controle, detecção de status, ponteiro descritor do SG DMA, endereço inicial, endereço de destino e comprimento do DMA simples não são complicados de usar. Em seguida, recomenda-se que o código do software correspondente copie diretamente o código do driver lateral ZYNQ do xilinx e, em seguida, você pode usá-lo com uma ligeira modificação.

Por fim, vamos dar uma olhada na ocupação de recursos. A ocupação de recursos é proporcional à largura de bits. Normalmente, com uma largura de bits de dados de 64 bits, ela ocupa cerca de 1.500 LUTs e 2.500 FFs. Na minha perspectiva, esse recurso é muito bom.

Figura 1-4 Uso de recursos

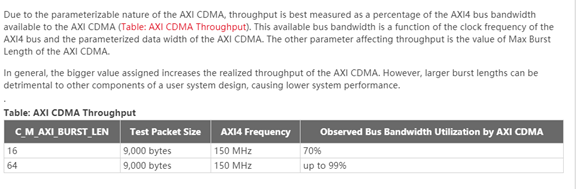

Figura 1-5 Eficiência de transmissão e largura de banda

2 Fluxo AXI para AXI4

2.1 Movedor de Dados AXI

O AXI Datamover é um IP de infraestrutura de interconexão chave que permite a transferência de dados de alto rendimento entre o domínio mapeado de memória AXI4 para o domínio AXI4-Stream. O AXI Datamover fornece canais MM2S e S2MM AXI4-Stream que operam independentemente em um método full duplex. O AXI Datamover é um componente essencial para o núcleo AXI DMA e permite proteção de limite de endereço de 4 kbytes, particionamento de burst automático, além de fornecer a capacidade de enfileirar várias solicitações de transferência usando quase todos os recursos de largura de banda do protocolo AXI4-Stream. Além disso, o AXI Datamover fornece realinhamento de dados em nível de byte, permitindo leituras e gravações de memória em qualquer local de deslocamento de byte.

AXI Datamover é um IP básico importante. Todos os IPs Xilinx DMA incluem basicamente este módulo, que pode converter dados nos formatos AXIS e AXI.

Quase todos os IPs DMA, como XDMA, VDMA, AXI DMA, AXI MCDMA, etc., incluem este módulo. Se esses DMAs existentes do xilinx não puderem atender às necessidades, o usuário poderá projetar um controlador DMA sozinho para completar a operação DMA.

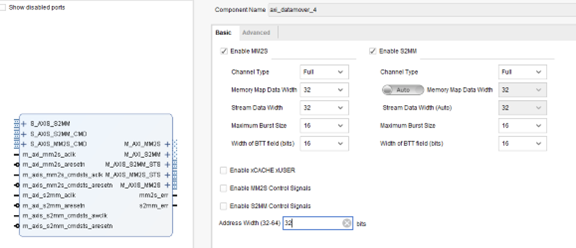

Figura 2-1 Interface e itens de configuração do AXI Datamover

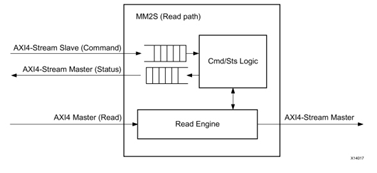

Figura 2-2 Canal de dados de leitura MM2S, leitura de dados da interface AXI4, convertendo-os em saída de dados AXIS

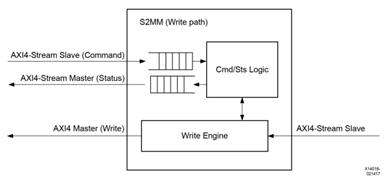

Figura 2-3 Canal de gravação de dados S2MM, entrada de dados AXIS, convertido em dados AXI4 e gravado na memória da interface AXI4

Figura 2-4 Uso de recursos

2.2 Controlador AXI DMA

O IP AXI Direct Memory Access (AXI DMA) fornece acesso direto à memória de alta largura de banda entre a memória e os periféricos de destino do tipo AXI4-Stream. Seus recursos opcionais de coleta de dispersão também aliviam tarefas de movimentação de dados da Unidade Central de Processamento (CPU) em sistemas baseados em processador. Os registros de inicialização, status e gerenciamento são acessados através de uma interface escrava AXI4-Lite.

Resumindo, o AXI DMA Controller fornece uma maneira simples de controlar a conversão (armazenamento de dados) das interfaces AXIS e AXI4 por software (por meio da interface AXI Lite).

Figura 2‑5 Diagrama de blocos internos do AXI DMA

Algo precisa ser explicado aqui: Se você optar por não habilitar o modo SG DMA, mas usar o modo de controle de registro puro, para o AXI DMA IP, o uso de recursos será reduzido e o desempenho será reduzido (outros IPs Xilinx DMA são semelhante), por que o desempenho será reduzido? Isso ocorre porque o modo de registro não suporta instruções de transferência predefinidas e só pode aguardar a conclusão de uma transferência antes de iniciar a próxima transferência, o que reduz a largura de banda e aumenta a intervenção da CPU. No entanto, este modo também é o mais simples e ainda depende dos requisitos de transmissão do projeto.

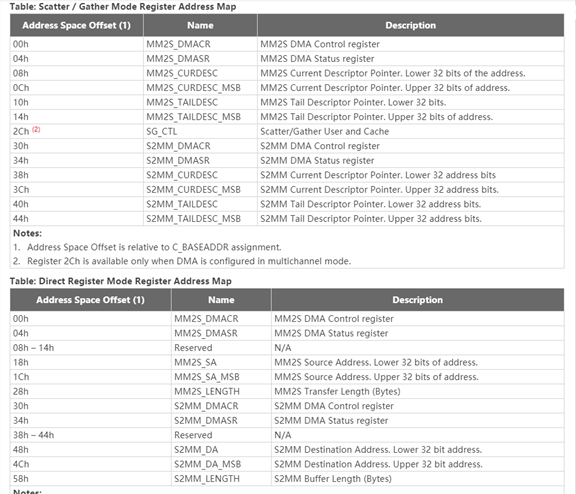

Vamos dar uma olhada na tabela de registros. A tabela lista os registros em dois modos: SG DMA e registro DMA. Como pode ser visto na tabela, não é complicado usar o AXI DMA. No entanto, ainda recomendo copiar diretamente o código do driver do Xilinx SDK., driver bare metal e exemplo são suficientes, simples, diretos e fáceis de usar.

A tabela da Figura 2-6 mostra os registros relevantes e seus significados no modo SG e no modo de registro.

Figura 2-7 Em termos de utilização de recursos, ainda é bastante.

Figura 2-8 Dados de latência, desempenho e largura de banda. Os dados de largura de banda são muito bons. De modo geral, é bom atingir 80%. A leitura é mais rápida do que a escrita, então a largura de banda do MM2S é próxima de 100% e a largura de banda do S2MM é de apenas 75%.

2.3 DMA multicanal AXI

Simplificando, é uma versão multicanal do AXI DMA. Ele foi projetado para lidar com transmissão de dados multicanal e de baixa velocidade. O AXI MCDMA suporta até 16 canais em ambas as direções, e cada canal é independente um do outro e permite configuração independente. Isso fornece muitas funções multifuncionais e de baixa velocidade. O aplicativo fornece uma solução FPGA de pequena área.

Como o AXI MCDMA é uma versão multicanal do AXI DMA, ele não será muito introduzido.

O AXI MCDMA facilita a migração de grandes volumes de dados, descarregando a tarefa do processador incorporado. Ele atua como intermediário entre um subsistema integrado AXI Memory-Mapped e um subsistema AXI Streaming. O IP MCDMA é full-duplex, scatter-gather e suporta até 16 canais. Pode ser configurado como round robin ponderado ou prioridade estrita

Figura 2-9 Diagrama de blocos estruturais do AXI MCDMA

2.4 DMA de vídeo AXI

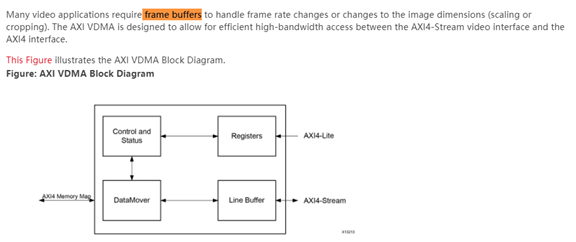

O núcleo AXI Video Direct Memory Access (AXI VDMA) é um núcleo Soft Xilinx IP que fornece acesso direto à memória de alta largura de banda entre a memória e os periféricos de destino de vídeo do tipo AXI4-Stream. O núcleo fornece operações DMA bidimensionais eficientes com operação de canal de leitura e gravação assíncrona independente. Os registros de inicialização, status, interrupção e gerenciamento são acessados através de uma interface escrava AXI4-Lite.

Por que precisamos do AXI VDMA quando temos o AXI DMA? O motivo pode ser visto no parágrafo a seguir. O processamento de vídeo Xilinx usa principalmente o formato AXIS. No entanto, em aplicações práticas, há muitas necessidades de alterar a taxa de quadros e os quadros de cache. Não é impossível usar AXI DMA diretamente, mas não pode estar bem integrado com outros AXIS O IP de vídeo da interface corresponde, então o AXI VDMA foi especialmente desenvolvido, principalmente para armazenar quadros de imagens em cache.Um amigo quer perguntar, o BRAM não pode ser usado para armazenamento em cache? Não, pois cada quadro correspondente à imagem pode ser muito grande e os recursos BRAM não são suficientes.

O uso do AXI VDMA é semelhante ao de outros IPs DMA. Nenhuma introdução adicional será dada aqui. Se quiser usá-lo, você pode verificar diretamente o manual oficial.

3 DMA PCIe

A Xilinx também lançou a interface AXI DMA para a interface PCIe, que corresponde ao Xilinx DMA para PCIe. Da mesma forma, semelhante a outras interfaces como USB e SRIO, os usuários também podem projetar soluções DMA semelhantes para construir uma arquitetura interna de sistema altamente confiável e flexível. .

O Xilinx® LogiCORE™ DMA para PCI Express® (PCIe) implementa um Scatter Gather DMA configurável e de alto desempenho para uso com o bloco integrado PCI Express. O IP fornece uma interface de usuário opcional AXI4-MM ou AXI4-Stream

Figura 3-1 Interface XDMA e itens de configuração de parâmetros

Figura 3-2 Diagrama de blocos interno XDMA

Então, o que o XDMA pode fazer? Isso é muito. Com este módulo, seu dispositivo PCIe Endpoint pode ser construído no barramento AXI e você terá uma arquitetura de sistema em chip flexível, confiável e de alto desempenho.

4 inspiração

Os usuários podem construir um sistema FPGA flexível e confiável baseado na arquitetura de diagrama de blocos Xilinx DMA e interconectado com interfaces AXI e AXIS.Se esses IPs não puderem atender aos requisitos, eles também podem imitar a arquitetura de PCIe XDMA e outros IPs para construir seu próprio sistema Arquitetura no chip.