contente

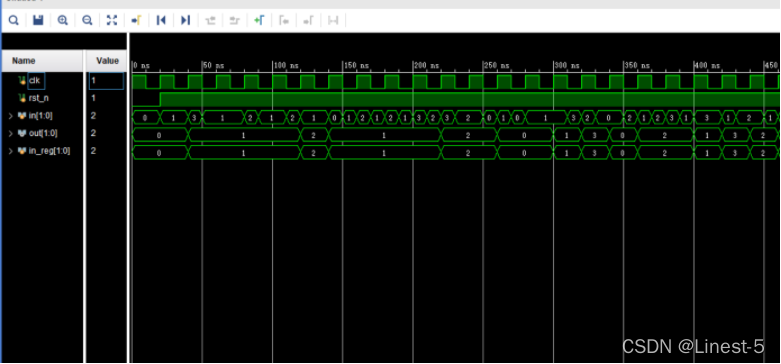

Simulação de atribuição de bloqueio

Escreva o código do arquivo de teste

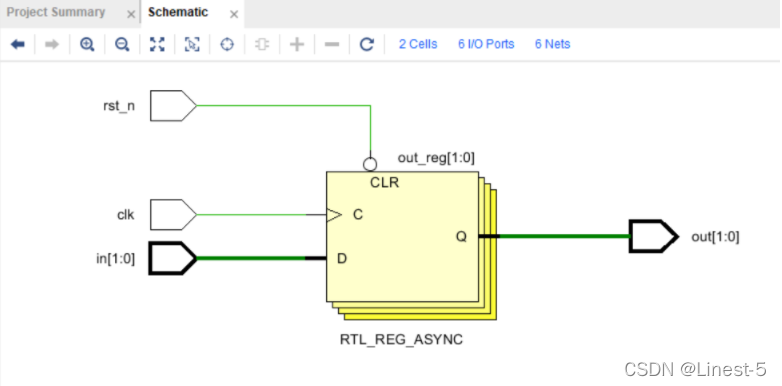

Visão abrangente do diagrama RTL

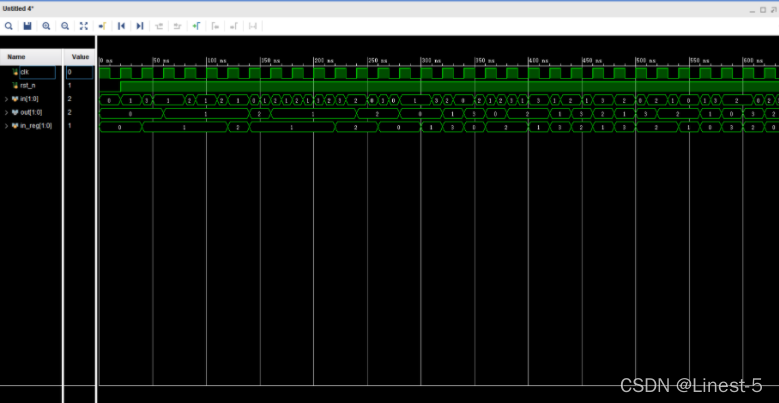

Simulação de atribuição sem bloqueio

Escreva o código do arquivo de teste

Visão abrangente do diagrama RTL

atribuição de bloqueio

O número de atribuição de atribuição de bloqueio é representado por "=", e a estrutura de circuito correspondente geralmente não tem nada a ver com o disparo de Yan Ni, mas está relacionada apenas à mudança do nível de entrada. Sua operação pode ser considerada como uma operação de uma etapa, ou seja, calcular a instrução do lado direito do número de atribuição e atualizar a instrução do lado esquerdo do número de atribuição. Neste momento, nenhuma interferência de qualquer outra instrução Verilog é permitido e o próximo não é permitido até que a atribuição atual seja concluída.

Um bloco serial também é chamado de begin end e as instruções de atribuição de bloqueio são executadas na ordem em que são listadas no bloco sequencial.

atribuição sem bloqueio

O número de atribuição de atribuição sem bloqueio é representado por "<=", a estrutura de circuito correspondente geralmente está relacionada à borda de disparo e a atribuição sem bloqueio pode ser realizada apenas no momento da borda de disparo.

Sua operação pode ser vista como um processo de duas etapas: ao final da atribuição, a instrução à esquerda do número da atribuição é atualizada.

Outras instruções Verilog podem operar simultaneamente enquanto a instrução à direita do número de atribuição da instrução sem bloqueio atualiza a instrução à esquerda do número de atribuição.

Os slots esquerdos não bloqueantes só podem ser usados para atribuição a variáveis de tipo de registro (reg), portanto, eles só podem ser usados em blocos "inicial" e "sempre" e não são permitidos para atribuição contínua "atribuir".

Simulação real de engenharia

Simulação de atribuição de bloqueio

Escrever código Verilog

A primeira é a simulação de atribuição de bloqueio (blocking), utilizando "=" para atribuição, indicando a atribuição de bloqueio.

module blocking

(

input wire clk,

input wire rst_n,

input wire [1:0] in,

output reg [1:0] out

);

reg [1:0] in_reg;

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

in_reg = 2'b0;

out = 2'b0;

end

else begin

in_reg = in;

out = in_reg;

end

end

endmoduleEscreva o código do arquivo de teste

`timescale 1ns / 1ns

module tb_blocking();

reg clk;

reg rst_n;

reg [1:0] in;

wire [1:0] out;

initial begin

clk = 1'b1;

rst_n <= 1'b0;

in <= 2'b0;

#20

rst_n <= 1'b1;

end

always #10 clk = ~clk;

always #10 in <= {$random} % 4;

blocking tb_blocking(

.clk(clk),

.rst_n(rst_n),

.in(in),

.out(out)

);

endmoduleVisão abrangente do diagrama RTL

Pode-se ver que há apenas um registrador, então o diagrama de simulação real deve mostrar que os sinais in_reg e out devem mudar ao mesmo tempo, e ambos os sinais são atrasados por uma batida do sinal in.

Faça a simulação real

como esperado

Simulação de atribuição sem bloqueio

Escrever código Verilog

Da seguinte forma: Basta alterar o código de atribuição de bloqueio de "=" para "

module blocking

(

input wire clk,

input wire rst_n,

input wire [1:0] in,

output reg [1:0] out

);

reg [1:0] in_reg;

always @(posedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

in_reg <= 2'b0;

out <= 2'b0;

end

else begin

in_reg <= in;

out <= in_reg;

end

end

endmoduleEscreva o código do arquivo de teste

Igual ao arquivo de teste para tarefas de bloqueio

`timescale 1ns / 1ns

module tb_blocking();

reg clk;

reg rst_n;

reg [1:0] in;

wire [1:0] out;

initial begin

clk = 1'b1;

rst_n <= 1'b0;

in <= 2'b0;

#20

rst_n <= 1'b1;

end

always #10 clk = ~clk;

always #10 in <= {$random} % 4;

blocking tb_blocking(

.clk(clk),

.rst_n(rst_n),

.in(in),

.out(out)

);

endmoduleVisão abrangente do diagrama RTL

Pode-se ver que existem dois registradores, um registrador é atribuído do sinal in para o sinal in_reg, e também há um registrador que é atribuído do sinal in_reg para o sinal out, então o diagrama de simulação real deve mostrar que o O sinal in_reg é atrasado em relação ao sinal de entrada. O tempo é de uma batida, e o sinal de saída é atrasado em uma batida em relação ao sinal de entrada, ou seja, duas batidas em relação ao sinal de entrada.

Diagrama de simulação real

Consistente com o que foi assumido após observar o gráfico RTL.

Resumir

A atribuição de bloqueio e a atribuição sem bloqueio não podem ser usadas indiscriminadamente no uso real, caso contrário, podem ocorrer consequências imprevisíveis. De acordo com as recomendações oficiais, ao escrever circuitos lógicos combinatórios, use atribuição de bloqueio; ao escrever lógica sequencial, use atribuições não bloqueantes. Atribuição de bloqueio .