Programação Concorrente - reordenação

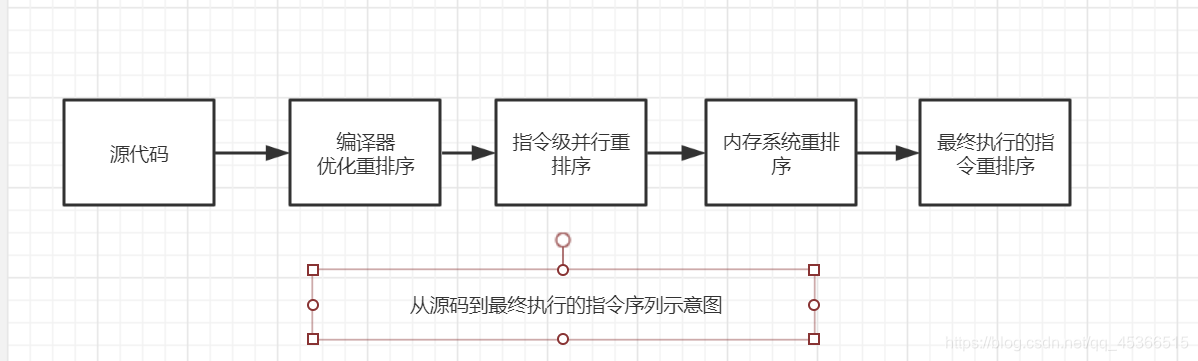

Ao executar o programa, a fim de melhorar o desempenho, muitas vezes têm instruções do compilador e processador não reordenação.

(1) optimizações do compilador reordenação .

O compilador não alterar a semântica da premissa de programas single-threaded, pode reorganizar a ordem de execução da instrução

(2) ILP reordenamento .

instrução do processador técnicas modernas nível de paralelismo a sobrepor-se uma pluralidade de instruções executadas. Se não existir nenhuma dependência de dados, o processador pode alterar a sequência de instruções de máquina correspondentes à ficha

(3) reordenação sistema de memória .

Desde o processador usando o cache e ler / buffer de gravação, o que torna as operações de carga e armazenamento parece provável para ser executado fora de ordem

reordenamento pode resultar em um de vários segmentos problemas de visibilidade de memória programa. tipos específicos de proibição de compiladores e processadores reordenação dar visibilidade para garantir programador memória consistente.

Para o compilador para compilar a atenção de JMM regras de classificação proibir um tipo particular de compilador pensa muito do tipo (nem todos os compiladores têm desencorajado o tipo proibida).

Para reordenar processador, a JMM processador reordenação regras afirmam compilador Java gera sequência de instruções novamente, o tipo particular de instrução barreira de memória inserido para proibir um tipo particular de instrução barreira de memória do processador, reordenando.

barreira de memória

| tipo barreira | tipo de instrução | explicação |

|---|---|---|

| Barreiras LoadLoad | Load1; LoadLoad; CARREG2 | Load1 assegurar dados CARREG2 carregado antes de toda a carga de instruções carga subsequente |

| Barreiras StoreStore | Store1; StoreStore; store2 | armazenamento de dados para garantir store1 visíveis para outros processadores (memória de atualização) antes da store2 e todos posterior instrução de armazenamento |

| Barreiras LoadStore | Load1; LoadStore; store2 | Load1 salgada store2 garantir um carregamento de dados e armazenamento de todas as instruções subsequentes são liberadas para a memória |

| Barreiras StoreLoad | Store1; grande carga; CARREG2 | Loja1 garantir que os dados se torna visível (referem-se a memória de actualização) é carregada pela primeira vez em CARREG2 e toda instrução subsequente carga para outros processadores. Todas as instruções de acesso à memória (instruções de carga e armazenamento) Barreiras StoreLoad vai após a barreira antes da conclusão, antes da implementação da instrução de acesso à memória após a barreira |

Barreiras StoreLoad é um "versáteis" barreiras, ele também tem o efeito de outros três barreira. Mais suporte multi-processador moderno para a barreira. Implementação da sobrecarga barreira vai ser muito caro, porque o processador atual tipicamente quer escrever todos os dados no buffer de memória de atualização (Tampão totalmente nivelado)