DMA는 직접 메모리 액세스입니다.FPGA 시스템에는 일반적으로 사용되는 몇 가지 DMA 요구 사항이 있습니다.

1. PL 내부에는 데이터 이동에 지속적으로 개입하는 PS(여기서는 CPU를 총칭하여 PS라고 함)가 없습니다. 일반적인 인터페이스 형태는 AXIS와 AXI, AXI와 AXI입니다.

2. PL과 PS 간 데이터 이동은 ZYNQ의 경우 이해하기 더 쉽습니다. 이는 단일 칩의 내부 인터페이스에 속하지만 PCIe와 같은 다른 인터페이스의 경우 약간 더 복잡하고 여러 칩 간의 인터페이스에 속합니다.

DMA 접근 방식의 목적을 살펴보세요.

1. 칩 내 데이터 이동 방법, 공통 인터페이스 및 DMA 구현 방법을 이해합니다.

2. 칩, 공통 인터페이스 및 DMA 구현 방법 간의 데이터 이동 방법을 이해합니다.

이러한 이해를 통해 시스템 데이터 마이그레이션을 위한 프레임워크 구조를 구축할 수 있으며, 유사한 요구가 발생하면 실제로 필요한 것은 기존 모듈을 호출하여 이를 구현하는 것뿐입니다.

이 기사는 주로 인터페이스 관점에서 Xilinx의 각 DMA IP를 소개하는 것으로 시작됩니다.

1 AXI4에서 AXI4까지

1.1 AXI 중앙 DMA 컨트롤러

AXI CDMA는 AXI4 프로토콜을 사용하여 메모리 매핑된 소스 주소와 메모리 매핑된 대상 주소 간에 고대역폭 DMA(직접 메모리 액세스)를 제공합니다. 선택적 SG(Scatter Gather) 기능을 사용하여 시스템 CPU에서 제어 및 시퀀싱 작업을 오프로드할 수 있습니다. 초기화, 상태 및 제어 레지스터는 Xilinx MicroBlaze™ 프로세서에 적합한 AXI4-Lite 슬레이브 인터페이스를 통해 액세스됩니다.

CDMA라고 부르는 이유는 실제로 CPU에 장착된 AXI 인터페이스 메모리 내에서 데이터 전송을 처리하는 것입니다. 일반적인 시나리오는 MicroBlaze입니다. ZYNQ라고 하면 어떨까요? ZYNQ의 AXI는 CPU 내부에 직접 탑재되어 이를 제어하기 위한 DMA가 필요하지 않으며, 필요한 경우 소프트웨어를 직접 복사하고 복사 작업을 수행하면 내부적으로 AXI DMA 작업이 시작됩니다. 그러나 ZYNQ가 PL 측에서 DDR을 사용하려면 CDMA를 사용해야 작동합니다. 왜냐하면 ZYNQ에는 AXI 마스터 인터페이스가 없고 SLAVE만 있기 때문입니다(여기서는 GP 저속 인터페이스가 아닌 고성능 HP 인터페이스에 대해 이야기하고 있습니다). .

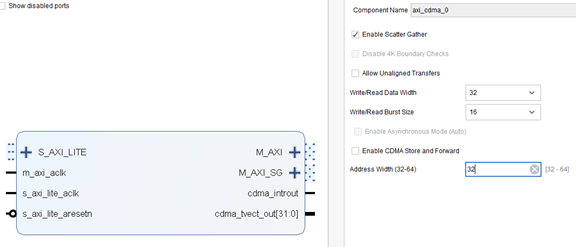

그림 1-1 AXI CDMA 인터페이스 및 매개변수 옵션, 여기서 S_AXI_LITE는 주 제어 CPU에 연결되고 M_AXI는 메모리에 연결되며 M_AXI_SG는 메모리에 연결됩니다(SG DMA 모드에서 dma 설명자를 저장하는 데 사용됨)

그림 1-2 CMDA 내부 구조 블록도

그림 1-3 ZYNQ 블록 다이어그램, 고성능 AXI SLAVE만 있고 MASTER는 없음

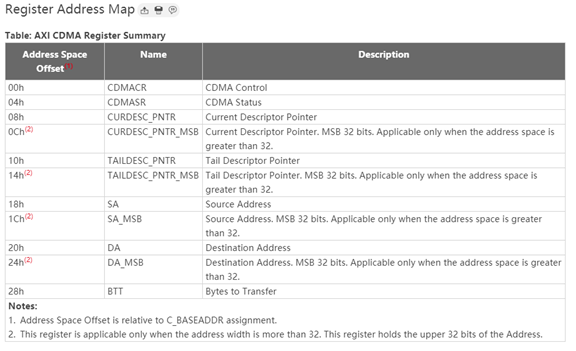

내부 레지스터를 살펴보면 실제로는 이게 더 직관적이고 사용자에게 모듈 구성 방법을 알려준다. 구성 방법을 보면 모듈 사용의 복잡도를 간단하게 추정할 수 있다. 레지스터 정의부터 제어, 상태 감지, SG DMA의 디스크립터 포인터, 시작 주소, 대상 주소 및 단순 DMA 길이는 사용이 복잡하지 않습니다. 그런 다음 해당 소프트웨어 코드를 사용하여 Xilinx의 ZYNQ 측 드라이버 코드를 직접 복사하는 것이 좋으며 약간 수정하여 사용할 수 있습니다.

마지막으로 리소스 점유율을 살펴보면, 리소스 점유율은 비트 폭에 비례하는데, 일반적으로 64비트 데이터 비트 폭에서 1500 LUT, 2500 FF 정도를 차지하는데, 제가 보기엔 이 리소스가 꽤 좋은 것 같습니다.

그림 1-4 리소스 사용량

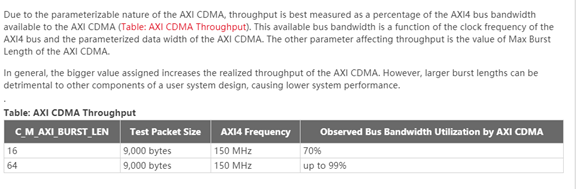

그림 1-5 전송 효율 및 대역폭

2 AXI 스트림을 AXI4로

2.1 AXI 데이터무버

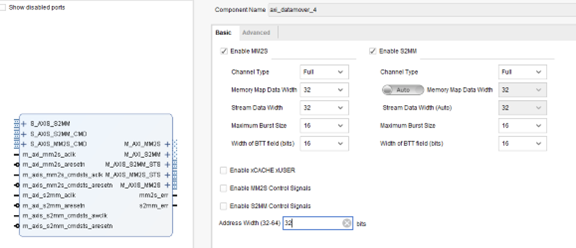

AXI Datamover는 AXI4 메모리 매핑 도메인과 AXI4-Stream 도메인 간에 높은 처리량의 데이터 전송을 가능하게 하는 핵심 상호 연결 인프라 IP입니다. AXI Datamover는 전이중 방식과 유사하게 독립적으로 작동하는 MM2S 및 S2MM AXI4-Stream 채널을 제공합니다. AXI Datamover는 AXI DMA 코어의 핵심 구성 요소이며 4KB 주소 경계 보호, 자동 버스트 파티셔닝을 지원하고 AXI4-Stream 프로토콜의 거의 전체 대역폭 기능을 사용하여 여러 전송 요청을 대기열에 추가하는 기능을 제공합니다. 또한 AXI Datamover는 바이트 수준 데이터 재정렬 기능을 제공하므로 모든 바이트 오프셋 위치에 대한 메모리 읽기 및 쓰기가 가능합니다.

AXI Datamover는 중요한 기본 IP로, 모든 Xilinx DMA IP에는 기본적으로 이 모듈이 포함되어 있어 AXIS 및 AXI 형식의 데이터를 변환할 수 있습니다.

XDMA, VDMA, AXI DMA, AXI MCDMA 등과 같은 거의 모든 DMA IP에는 이 모듈이 포함되어 있습니다.xilinx의 기존 DMA가 요구 사항을 충족할 수 없는 경우 사용자는 DMA 컨트롤러를 직접 설계하여 DMA 작업을 완료할 수 있습니다.

그림 2-1 AXI Datamover 인터페이스 및 구성 항목

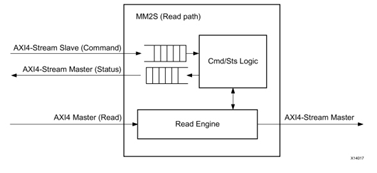

그림 2-2 MM2S 데이터 채널 읽기, AXI4 인터페이스 데이터 읽기, AXIS 데이터 출력으로 변환

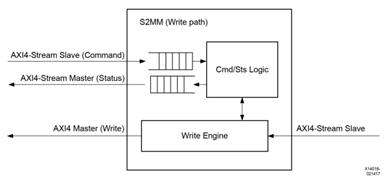

그림 2-3 S2MM 쓰기 데이터 채널, AXIS 데이터 입력, AXI4 데이터로 변환되어 AXI4 인터페이스 메모리에 기록됨

그림 2-4 리소스 사용량

2.2 AXI DMA 컨트롤러

AXI DMA(AXI 직접 메모리 액세스) IP는 메모리와 AXI4-Stream 유형 대상 주변 장치 간에 고대역폭 직접 메모리 액세스를 제공합니다. 또한 선택적 분산 수집 기능은 프로세서 기반 시스템의 중앙 처리 장치(CPU)에서 데이터 이동 작업을 오프로드합니다. 초기화, 상태 및 관리 레지스터는 AXI4-Lite 슬레이브 인터페이스를 통해 액세스됩니다.

즉, AXI DMA 컨트롤러는 AXI Lite 인터페이스를 통해 소프트웨어로 제어할 수 있는 AXIS 및 AXI4 인터페이스의 변환(데이터 저장)을 위한 간단한 방법을 제공합니다.

그림 2-5 AXI DMA 내부 블록 다이어그램

여기에 설명이 필요합니다. SG DMA 모드를 활성화하지 않고 순수 레지스터 제어 모드를 사용하도록 선택하면 AXI DMA IP의 경우 리소스 사용량이 줄어들고 성능이 저하됩니다(다른 Xilinx DMA IP는 유사), 왜 성능이 저하되나요? 이는 레지스터 모드가 사전 설정된 전송 명령을 지원하지 않고 다음 전송을 시작하기 전에 하나의 전송이 완료될 때까지만 기다릴 수 있기 때문에 대역폭이 줄어들고 CPU 개입이 증가하기 때문입니다. 그러나 이 모드는 가장 단순하며 여전히 설계의 전송 요구 사항에 따라 달라집니다.

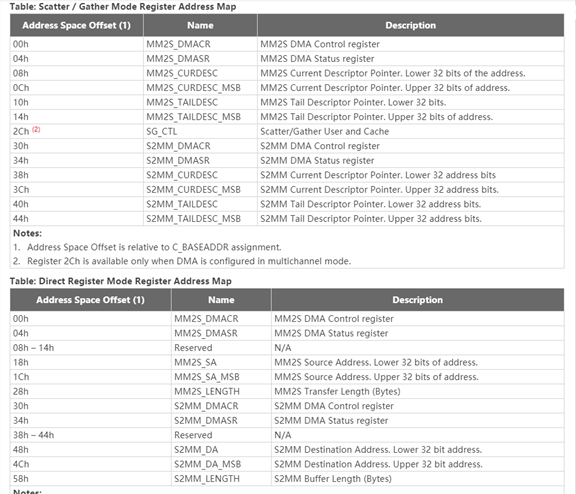

레지스터 테이블을 살펴보면 SG DMA와 레지스터 DMA 두 가지 모드의 레지스터가 나열되어 있는데, 표에서 볼 수 있듯이 실제로 AXI DMA를 사용하는 것은 복잡하지 않지만 그래도 직접 복사하는 것을 추천한다. Xilinx SDK의 드라이버 코드, 베어 메탈 드라이버 및 예제는 충분하고 간단하며 직접적이며 사용하기 쉽습니다.

그림 2-6 표는 SG 모드와 레지스터 모드에서 관련 레지스터와 그 의미를 보여줍니다.

그림 2-7 리소스 사용량 측면에서는 여전히 많은 양을 차지하고 있습니다.

그림 2-8 지연 시간, 성능 및 대역폭 데이터 대역폭 데이터는 꽤 좋습니다. 일반적으로 80%를 달성하는 것이 좋습니다. 읽기가 쓰기보다 빠르므로 MM2S의 대역폭은 100%에 가깝고 대역폭은 S2MM의 비율은 75%에 불과합니다.

2.3 AXI 다중채널 DMA

간단히 말하면 AXI DMA의 다채널 버전으로 다채널, 저속 데이터 전송에 대응하도록 설계되었으며, AXI MCDMA는 양방향 최대 16채널을 지원하며, 각 채널은 서로 독립적이며, 독립적인 구성이 가능하며 이는 다양한 저속 다기능을 제공합니다. 이 애플리케이션은 작은 면적의 FPGA 솔루션을 제공합니다.

AXI MCDMA는 AXI DMA의 다중 채널 버전이므로 많이 소개되지는 않을 것입니다.

AXI MCDMA는 내장형 프로세서에서 작업을 오프로드하여 대규모 데이터 마이그레이션을 용이하게 합니다. 이는 AXI 메모리 매핑 임베디드 하위 시스템과 AXI 스트리밍 하위 시스템 사이의 중개자 역할을 합니다. MCDMA IP는 전이중, 분산 수집 및 최대 16개 채널을 지원합니다. 가중치가 부여된 라운드 로빈 또는 엄격한 우선순위로 구성될 수 있습니다.

그림 2-9 AXI MCDMA 구조 블록 다이어그램

2.4 AXI 비디오 DMA

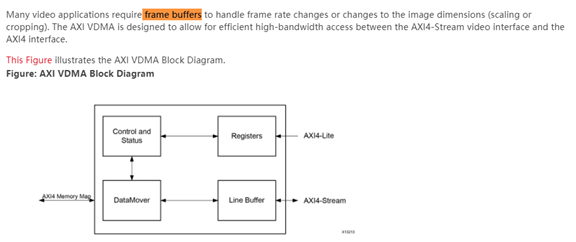

AXI VDMA(AXI Video Direct Memory Access) 코어는 메모리와 AXI4-Stream 유형 비디오 대상 주변 장치 간에 고대역폭 직접 메모리 액세스를 제공하는 소프트 Xilinx IP 코어입니다. 코어는 독립적인 비동기 읽기 및 쓰기 채널 작업을 통해 효율적인 2차원 DMA 작업을 제공합니다. 초기화, 상태, 인터럽트 및 관리 레지스터는 AXI4-Lite 슬레이브 인터페이스를 통해 액세스됩니다.

AXI DMA가 있는데 왜 AXI VDMA가 필요한가요? 그 이유는 다음 단락을 보면 알 수 있는데, Xilinx의 영상처리에서는 대부분 AXIS 포맷을 사용하는데, 실제 응용에서는 프레임 레이트와 캐시 프레임을 변경해야 하는 경우가 많으며, AXI DMA를 직접 사용하는 것이 불가능하지는 않지만 불가능합니다. 다른 AXIS와 잘 통합됩니다. 인터페이스의 비디오 IP가 일치하므로 AXI VDMA는 주로 이미지 프레임을 캐시하기 위해 특별히 개발되었습니다. 친구가 묻고 싶습니다. BRAM을 캐싱에 사용할 수 없나요? 아니요, 이미지에 해당하는 각 프레임이 매우 클 수 있고 BRAM 리소스가 충분하지 않기 때문입니다.

AXI VDMA의 사용법은 다른 DMA IP와 유사하므로 여기서는 더 이상 소개하지 않겠습니다. 사용을 원할 경우 공식 매뉴얼을 직접 확인하면 됩니다.

3개의 PCIe DMA

Xilinx는 또한 PCIe용 Xilinx DMA에 대응하는 PCIe 인터페이스용 AXI DMA 인터페이스를 출시했습니다. 마찬가지로 USB 및 SRIO와 같은 다른 인터페이스와 마찬가지로 사용자는 유사한 DMA 솔루션을 설계하여 매우 안정적이고 유연한 시스템 내부 아키텍처를 구축할 수 있습니다. .

PCI Express®(PCIe)용 Xilinx® LogiCORE™ DMA는 PCI Express 통합 블록과 함께 사용하기 위해 구성 가능한 고성능 Scatter Gather DMA를 구현합니다. IP는 선택적 AXI4-MM 또는 AXI4-Stream 사용자 인터페이스를 제공합니다.

그림 3-1 XDMA 인터페이스 및 매개변수 구성 항목

그림 3-2 XDMA 내부 블록 다이어그램

그렇다면 XDMA는 무엇을 할 수 있습니까? 이 모듈을 사용하면 PCIe 엔드포인트 장치를 AXI 버스에 구축할 수 있으며 유연하고 안정적인 고성능 시스템 온 칩 아키텍처를 갖게 됩니다.

4 영감

사용자는 Xilinx DMA 블록 다이어그램 아키텍처를 기반으로 AXI 및 AXIS 인터페이스와 상호 연결된 유연하고 안정적인 FPGA 시스템을 구축할 수 있습니다. 이러한 IP가 요구 사항을 충족할 수 없는 경우 PCIe XDMA 및 기타 IP의 아키텍처를 모방하여 자체 시스템을 구축할 수도 있습니다. -온칩 아키텍처. .