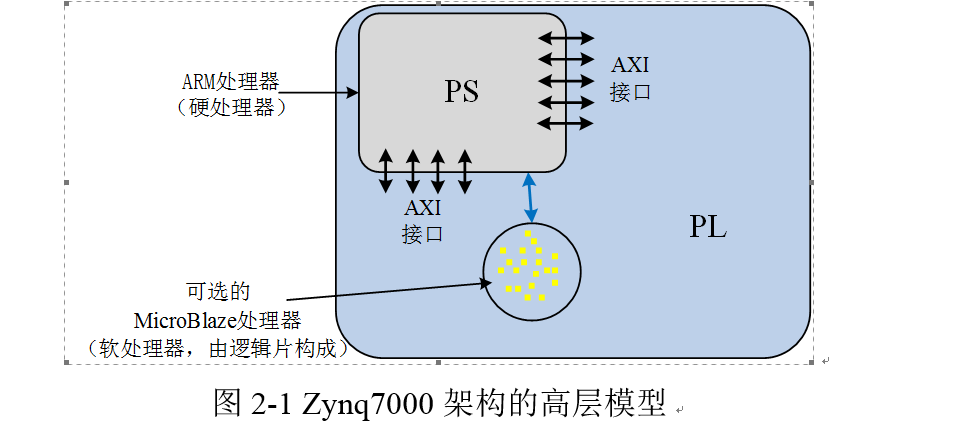

一連APSOC Zynq7000スケーラブルな処理プラットフォーム基づいて、その本質的な特徴は、デュアルコアプロセッサとARMのCortex-A9シートにシステムに統合プログラマブルFPGAチップです。詳細な説明Zynq7000を実行する前に、高レベルのアーキテクチャモデルのこの最初のセクションは、図2-1に示すように、導入されます。

ARMプロセッサ、典型的には記憶及び処理システム(プロセッサシステム、PS)と呼ばれる様々な周辺リソースは、FPGAの部分は、プログラマブルロジック(プログラマブルロジック、PL)と呼ばれます。ARMのCortex-A9は、アプリケーションレベルのプロセッサで、Linuxのようなオペレーティングシステムの実行をサポート。FPGA使用Xilinx7業界標準アーキテクチャは、効率的な結合がARMとFPGAとの間に形成されたAXIインタフェースを可能にする、別個のチップももたらし、高帯域幅、低レイテンシ接続を達成するだけでなく、生成、追加の電力を低減します物理的な大きさと生産コストを低減します。

それは言及する価値がある、PL部はZynq7000ソフトプロセッサMicroBlazeのように構成することができます。MicroBlazeではからプログラマブルロジック部分の要素の組み合わせである[19] IPコアのMicroBlazeのFPGA実装と展開が正常等価です。ソフトプロセッサが一緒に働くことができるとARMは、特定の基礎となる機能とシステム間の調整を担当して、アームのCortex-A9プロセッサから分社未満要求タスクの一部は、システム性能を向上させます。

高速ロジック・サブシステムのPL Zynq7000部は、並列データストリームを実装するために、処理は、理想的なPSまたは部分的に、オペレーティング・システム・ソフトウェアの制御によって支持されています。これは、このプラットフォームに基づいて、ほとんどのシステムは、システム全体で最高のパフォーマンスを発揮するように、PSとPLは、自分の強みに再生することができますすること、機能のソフトウェアとハードウェア部門になるように設計されていることを意味します。図2-2に示すチップ内部アーキテクチャにZynq7000システム

PSリソースの部分は、[14] [16] [20] 。

(1)アプリケーション処理ユニット(APU):ARMのCortex-A9デュアルコアプロセッサ、1GHz以上までの最大動作周波数を。任意の2つの核コア(32キロバイトであり、それぞれが二つの部分に分け命令およびデータ)キャッシュ、メモリ管理ユニット(MMUは、仮想アドレスと物理アドレスとの間で変換する)を含みます。さらに、2つのコアが命令とデータを格納するための二次キャッシュ512キロバイトを共有しています。さらに他のシステムリソースがNEONTMメディア処理エンジンと、浮動小数点ユニット(FPU)を備え、オンチップメモリ(OCM)、制御ユニット(SCU)、割り込みコントローラの一貫。前記SCUとARMコアOCM二次キャッシュメモリとドッキングPLのための部分的な原因も形成橋、との間。

(2)PS部AXIインタフェースのメインのZynqとPL間のAXIインタフェース接続形態について詳細に説明します。

(3)メモリインタフェースを、16ビット/ 32ビット幅のDDR3、DDR2および四線式SPIコントローラをサポートします。

(4)多重入力/出力ピンを含むI / O周辺機器インタフェース(MIO)、(共通PLを達成するために、I / Oリソースを介してEMIO)MIO拡張、および通信インタフェース規格汎用入力/出力ピン(GPIO )。4線式コントローラSPI、CANコントローラ、UARTコントローラとIに基づいて、また、イーサネットコントローラ(サポートの10Mbps、100Mbpsの、および1Gbpsのモード)、USBコントローラ、SD / SDIOコントローラ2 Cコントローラ。

含むPLリソースセクション[21-23] :

(1)一般的なFPGAロジック。ブロックの入力/出力インターフェースに加えて、構成可能論理ブロック、を含むロジックチップ。FPGAロジック部と図2-3に示される構成単位。

(2)XADCブロック。これは、専用のアナログである - デジタルコンバータ(アナログデジタル変換器、ADCへの)混合信号ハードウェア、二つの独立した12 ADCを有し、各アナログ信号は1Mspsの外部入力のサンプリング周波数でサンプリングすることができます。PS内に位置するインターフェース制御ブロックPS-XADCはXADCを実施し、PS-プログラム制御ブロック自体は、APUによって制御されてもよいことでXADCを制御します。

(3)時計PLがPSから4つの別個のクロック入力を受け、もう一方はそれ自身の独立したクロック信号PSを生成して配布することができます。この独立したPL 7シリーズFPGAリソースと場所は同じです。