目次

- 1 はじめに

- 2. ここにある GT 高速インターフェイス ソリューション

- 3. GTP ネットワークの最も詳細な解釈

- 4. デザイン思考のフレームワーク

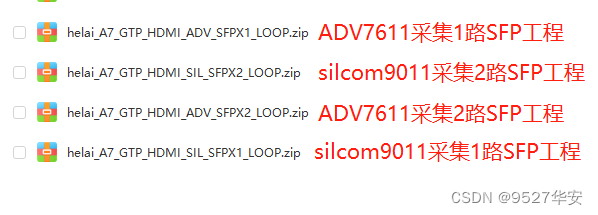

- 5. vivado プロジェクト 1 --> ADV7611 の取得 --> 双方向 SFP 送信

- 6. vivado プロジェクト 2 --> ADV7611 取得 --> 1 チャネル SFP 送信

- 7. vivado プロジェクト 3 --> Silicon9011 の取得 --> 双方向 SFP 送信

- 8. vivado プロジェクト 4 --> シリコン 9011 取得 --> 1 チャネル SFP 送信

- 9. ボードのデバッグと検証

- 10. 福利厚生:技術コード取得

1 はじめに

GT リソースをプレイしたことがないのに、FPGA をプレイしたことがあると言うのは恥ずかしいことです。これは CSDN の偉い人が言った言葉で、私はそれを強く信じています。。。

GT リソースは、ザイリンクス シリーズ FPGA の重要なセールス ポイントであり、高速インターフェイスの基盤でもあり、PCIE、SATA、MAC などのいずれであっても、データの高速シリアル化および逆シリアル化には GT リソースが必要です。ザイリンクスの各 FPGA シリーズには異なる GT リソース タイプがあり、ローエンドの A7 には GTP、K7 には GTX、V7 には GTH、ハイエンドの U+ シリーズには GTY などがあります。それらの速度はますます高速になり、そのアプリケーションはシナリオはますますハイエンドになっています。。。

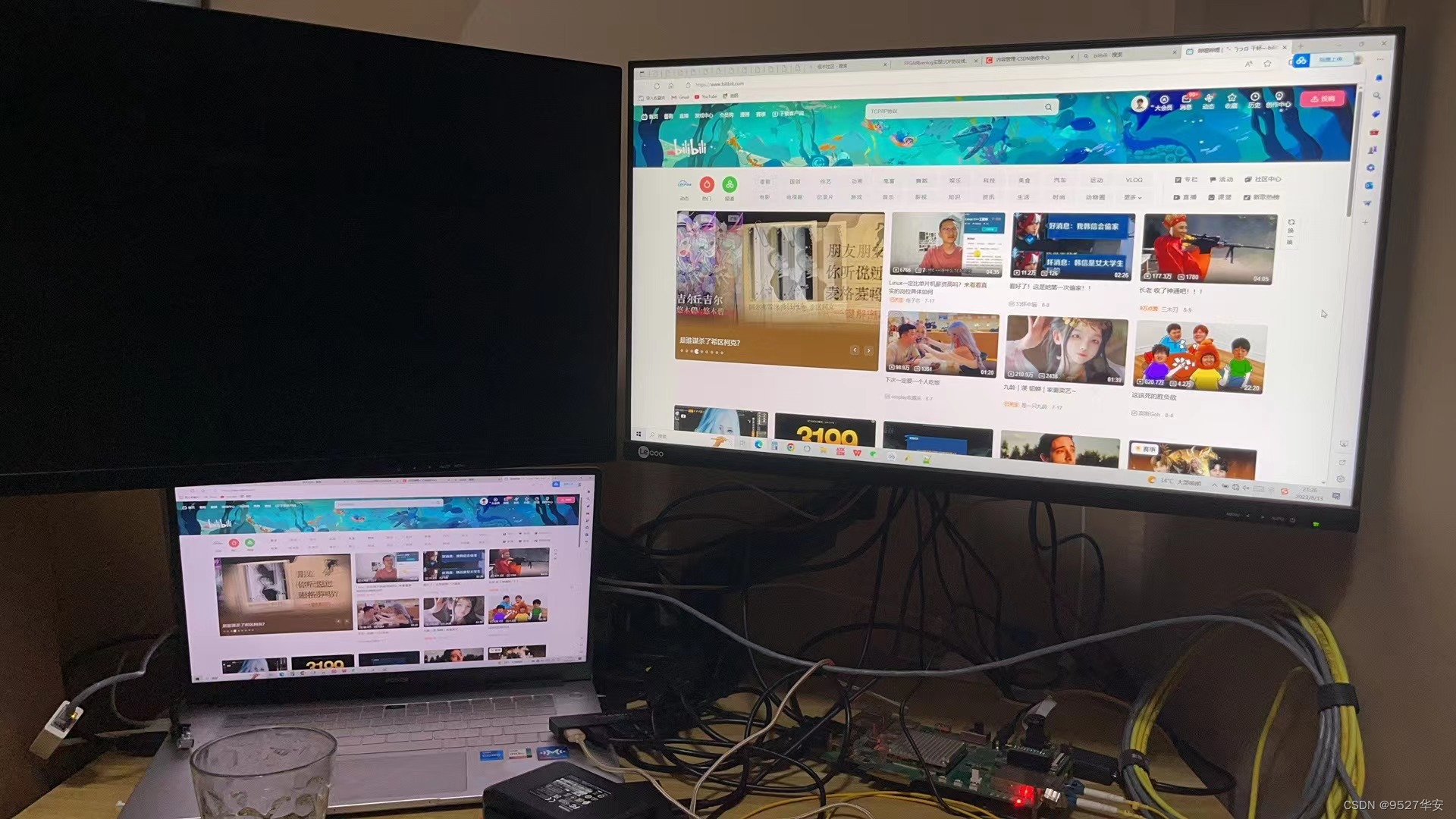

この記事では、ザイリンクスの Artix7 FPGA の GTP リソースを使用してビデオ伝送実験を行います。ビデオ ソースはラップトップを使用してアナログ HDMI ビデオ入力を出力し、GTP IP コアを呼び出し、verilog を使用してビデオ データ コーデック モジュールとデータ アラインメント モジュールを書き込みます。開発ボード ハードウェアを使用します。データの送受信を実現するために 1 つまたは 2 つの SFP 光ポート。このブログでは 4 セットの vivado プロジェクト ソース コードを提供します。4 セットのプロジェクトの違いは、送信と受信に 1 つの SFP 光ポートを使用するかどうかです。受信または送受信用の 2 つの 2 SFP 光ポート。ここでは基本的に、さまざまな HDMI 取得チップがあります。1 つは HDMI 取得チップとしての ADV7611、HDMI 出力は純粋な Verilog コード送信モジュールによって完了され、もう 1 つは HDMI 取得チップとしての Silicon9011、 HDMI ビデオを出力するための HDMI エンコーディング チップとしての Silicon9134; ブログでは FPGA GTP ビデオ伝送の設計スキームを詳細に説明しています. エンジニアリング コードはボード上で包括的にコンパイルおよびデバッグでき、直接移植できます. 学生および大学院生に適していますプロジェクト開発だけでなく、実務エンジニアの学習向上にも適しており、医療、医療、軍需産業やその他の産業の高速インターフェースまたは画像処理分野に適用でき、完全でスムーズなエンジニアリングソースコードを提供します

。エンジニアリングソースコードと技術サポート

の入手方法は記事の最後に記載されていますので、最後までお待ちください。

免責事項

このプロジェクトとそのソース コードは、一部は私自身が作成したものであり、一部はインターネット上のパブリック チャネル (CSDN、ザイリンクス公式 Web サイト、アルテラ公式 Web サイトなどを含む) から入手したものであり、プロジェクトとそのソース コードは個人的な研究および目的に限定されています。読者やファンの研究、商用利用は禁止します 読者やファンが独自の理由で商用利用することによって生じる法的問題が当ブログおよびブロガーと無関係の場合は、慎重にご利用ください。。。

2. ここにある GT 高速インターフェイス ソリューション

私のホームページには FPGA GT 高速インターフェイスのコラムがあり、そこには GTP、GTX、GTH、GTY などの GT リソースのビデオ送信ルーチンと PCIE 送信ルーチンが含まれています。そのうち GTP は A7 シリーズ FPGA 開発ボードに基づいており、GTX はK7 または ZYNQ シリーズ FPGA 開発ボードに基づいて構築され、GTH は KU または V7 シリーズ FPGA 開発ボードに基づいて構築され、GTY は KU+ シリーズ FPGA 開発ボードに基づいて構築されます。以下は列アドレスです: クリックして直接

移動

3. GTP ネットワークの最も詳細な解釈

GTP の最も詳細な入門書は、ザイリンクスの公式「ug482_7Series_GTP_Transceivers」である必要があります。これを解釈するために使用します。「ug482_7Series_GTP_Transceivers」の

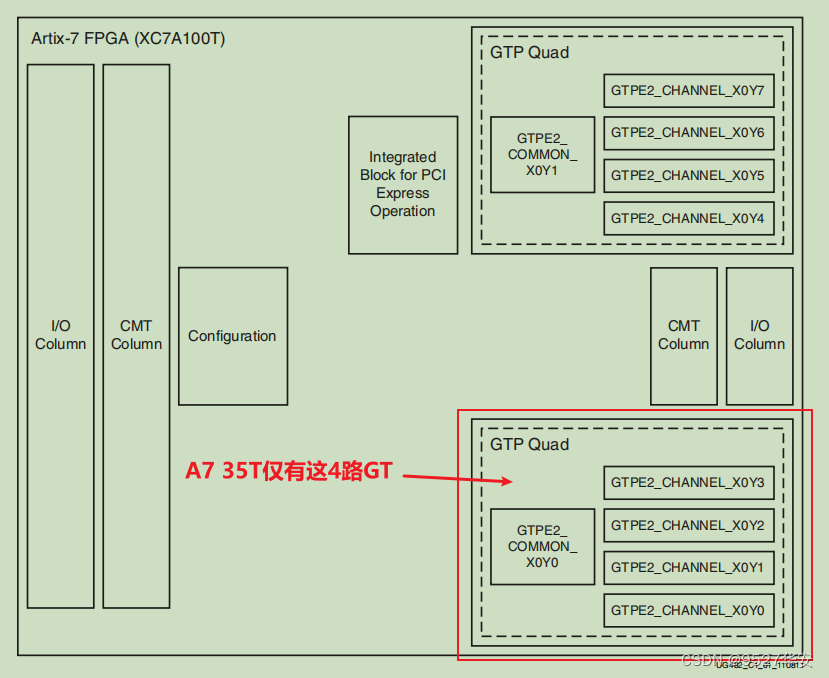

PDF ドキュメントを情報パッケージに入れました。この記事の最後に入手方法があります。私が使用した開発ボードのFPGA

モデルは Xilinx Artix7 xc7a35tfgg484-2 で、GTP リソースが 4 チャネルあり、各チャネルの送受信速度は 500 Mb/s ~ 6.6 Gb/s です。GTP トランシーバーは、PCIE 1.1/2.0 インターフェイス、10 ギガビット ネットワーク XUAI インターフェイス、OC-48、シリアル RapidIO インターフェイス、SATA (シリアル ATA) インターフェイス、デジタル コンポーネント シリアル インターフェイス (SDI) などのさまざまなシリアル伝送インターフェイスまたはプロトコルをサポートします。

GTPの基本構造

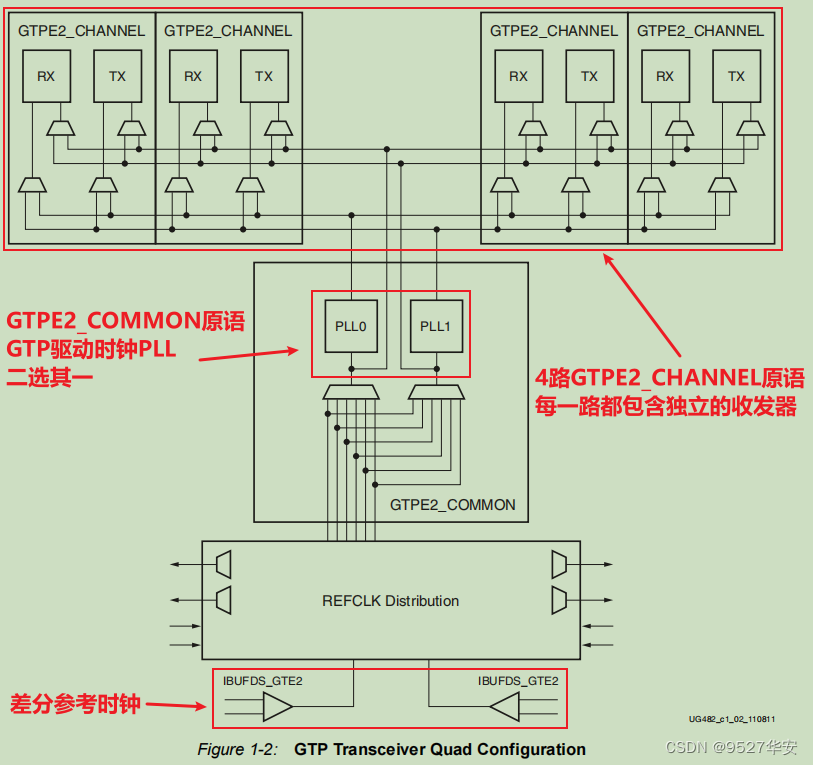

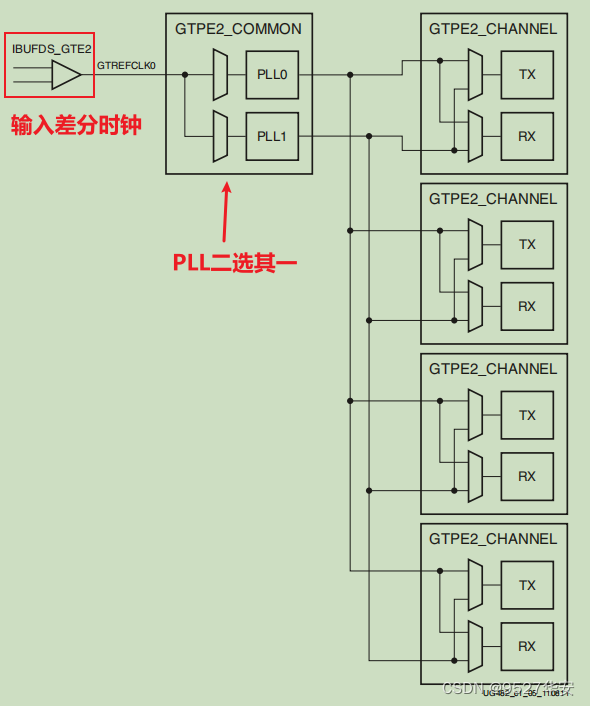

ザイリンクスは、シリアル高速トランシーバーをグループ化するためにクワッドを使用しています。4 つのシリアル高速トランシーバーと COMMOM (QPLL) がクワッドを形成します。各シリアル高速トランシーバーは、チャネル (チャネル) と呼ばれます。下の図は、4 つのシリアル高速トランシーバーを示しています。 Artix-7 FPGA チップの GTP トランシーバー: 「ug482_7Series_GTP_Transceivers」13 ページ;

GTP の具体的な内部ロジック ブロック図を以下に示しますが、これは 4 つのトランシーバー チャネル GTPE2_CHANNEL プリミティブと GTPE2_COMMON プリミティブで構成されます。各 GTPE2_CHANNEL には送信回路 TX と受信回路 RX が含まれています。「ug482_7Series_GTP_Transceivers」14 ページ。

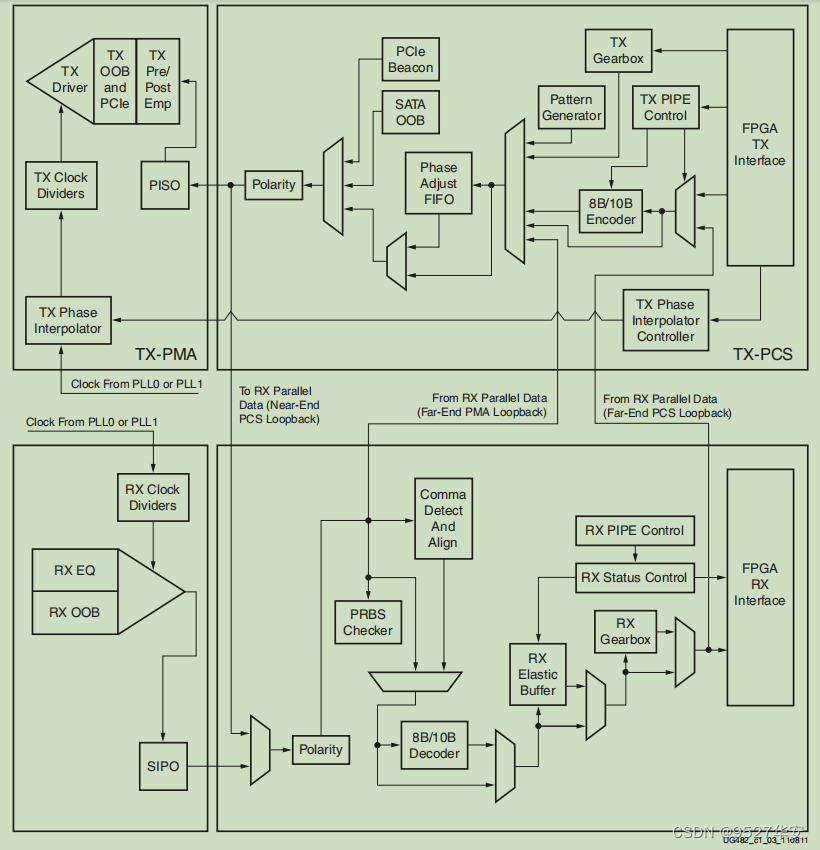

各 GTPE2_CHANNEL の論理回路は次の図に示されています。「ug482_7Series_GTP_Transceivers」15 ページ。GTPE2_CHANNEL の

送信側と受信側の機能は次のとおりです。独立、両方 PMA (Physical Media Attachment、物理メディア アダプテーション層) と PCS (Physicalcoding Sublayer、物理コーディング サブレイヤ) の 2 つのサブレイヤで構成されます。PMA サブレイヤには、高速シリアル/パラレル変換 (Serdes)、プリ/ポストエンファシス、受信イコライゼーション、クロック ジェネレーター、およびクロック リカバリ回路が含まれています。PCS サブレイヤには、8B/10B コーデック、バッファ、チャネル ボンディング、クロック補正などの回路が含まれます。

ここで多くを語ることはあまり意味がありません。いくつかの大きなプロジェクトを実行したことがなければ、その内容を理解できないからです。初めてのユーザーや高速ユーザーの場合は、より多くのエネルギーを呼び出しに集中する必要があります。と IP コアの使用については、後で IP コアの呼び出しと使用にも焦点を当てます。

GTP送受信処理の流れ

まず、ユーザー ロジック データは 8B/10B でエンコードされた後、送信バッファ (位相調整 FIFO) に入ります。このバッファは主に PMA サブレイヤと PCS サブレイヤの 2 つのクロック ドメイン間のクロック分離に使用され、クロック レートの問題を解決します。両者間のマッチングと位相調整を行います。差分の問題に対しては、高速 Serdes を介してパラレルシリアル変換 (PISO) が実行されます。必要に応じて、プリエンファシス (TX プリエンファシス) とポストエンファシスが可能です。実行されました。PCB 設計中に誤って TXP と TXN の差動ピンを相互接続した場合でも、極性制御 (Polarity) によってこの設計エラーを補うことができることに注意してください。受信側と送信側の処理は逆であり、類似点が多いため、ここでは詳しく説明しませんが、RX 受信側のエラスティック バッファーにはクロック補正機能とチャネル バインディング機能があることに注意してください。ここにあるすべての機能ポイントは論文や本を書くことができるため、ここでは概念を知るだけでよく、それを特定のプロジェクトで使用することも、同じ文章で使用することもできます。初めて使用する場合、またはすぐに使用したい場合心配している人は、IP コアの呼び出しと使用にもっとエネルギーを集中する必要があります。

GTPの基準クロック

GTP モジュールには 2 つの差動リファレンス クロック入力ピン (MGTREFCLK0P/N および MGTREFCLK1P/N) があり、ユーザーはこれらを GTP モジュールのリファレンス クロック ソースとして選択できます。一般的な A7 シリーズ開発ボードには、GTP リファレンス クロックとして MGTREFCLK0/1 に接続された 125Mhz GTP リファレンス クロックがあります。差動リファレンス クロックは、IBUFDS モジュールによってシングルエンド クロック信号に変換され、GTPE2_COMMOM の PLL0 および PLL1 に入力されて、TX および RX 回路で必要なクロック周波数を生成します。TX と RX のトランシーバー速度が同じ場合、TX 回路と RX 回路は同じ PLL で生成されたクロックを使用できますが、TX と RX トランシーバーの速度が同じでない場合は、異なる PLL クロックで生成されたクロックを使用する必要があります。使用済み。リファレンス クロック ここで、ザイリンクスが提供する GT リファレンス ルーチンは非常によくできており、呼び出すときに変更する必要はありません。GTP のリファレンス クロック構造は次のとおりです。

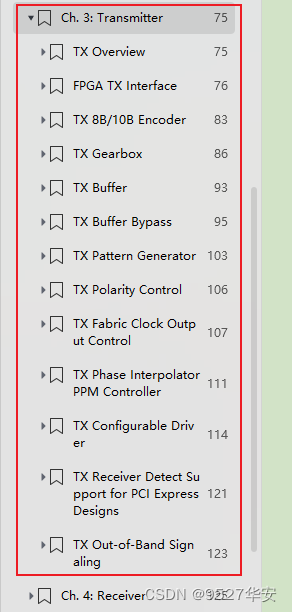

GTP送信インターフェース

「ug482_7Series_GTP_Transceivers」の 75 ページから 123 ページでは、送信プロセスが詳細に紹介されていますが、マニュアルは基本的に彼自身の設計アイデアについて述べており、ユーザーが操作できるインターフェイスやこれに基づいたものは多くないため、ユーザーはほとんどの内容を無視できます。このアイデアでは、GTP インスタンス化中にユーザーに任せられる送信部分に必要なインターフェイスに焦点を当てます。

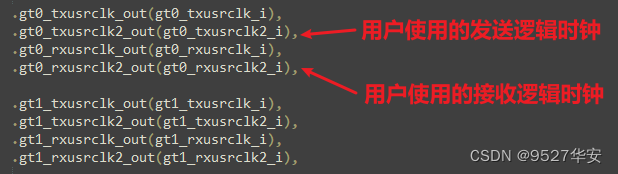

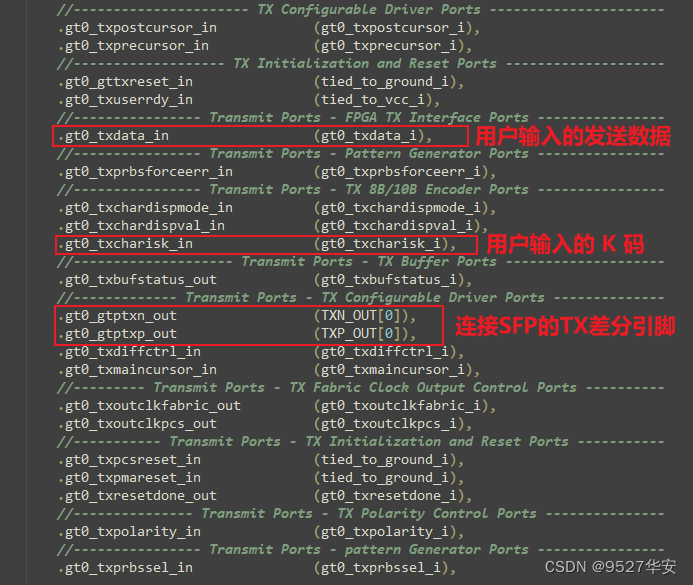

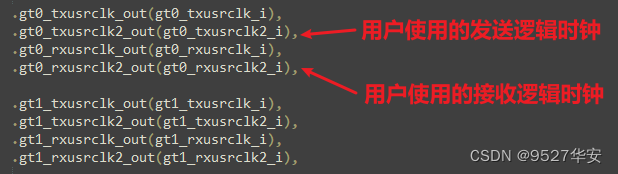

ユーザーは送信インターフェイスのクロックとデータのみを気にする必要があります。GTP インスタンス化モジュールのこの部分のインターフェイスは次のとおりです。

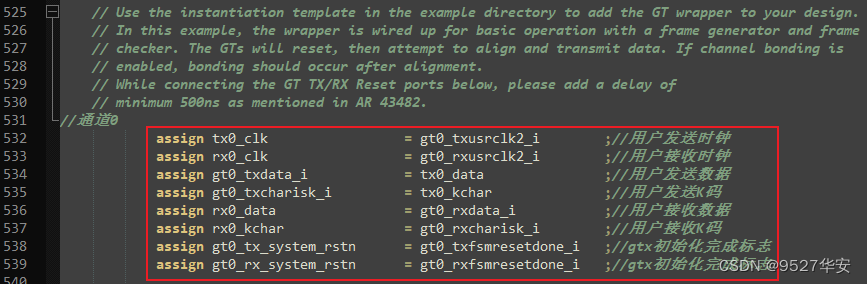

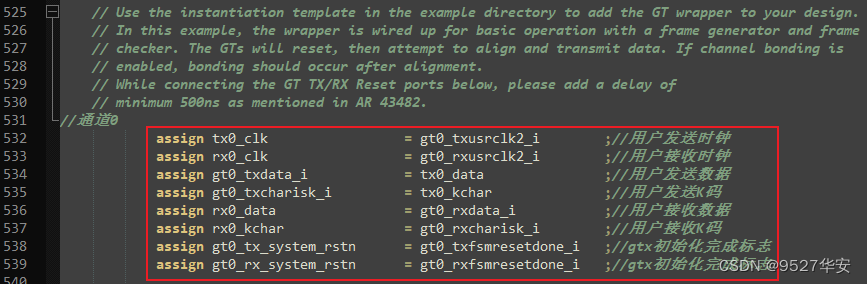

コードでは、私が再バインドしてモジュールの最上位にしました。コード部分は次のとおりです。

GTP受信インターフェース

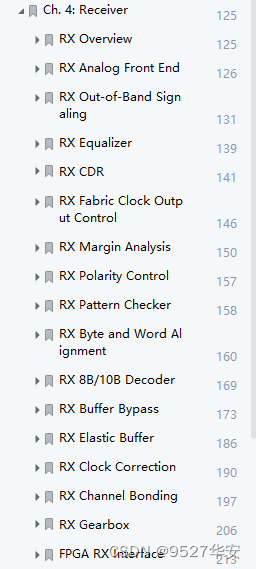

「ug482_7Series_GTP_Transceivers」の 125 ページから 213 ページでは、送信プロセスが詳細に紹介されていますが、マニュアルは基本的に彼自身の設計アイデアについて述べており、このアイデアに基づいてユーザーの操作可能なインターフェイスを残し、多くは多くないため、ユーザーにとってほとんどの内容は無視できます。 , GTP インスタンス化中にユーザーに任せられる送信部分に必要なインターフェイスに焦点を当てます。

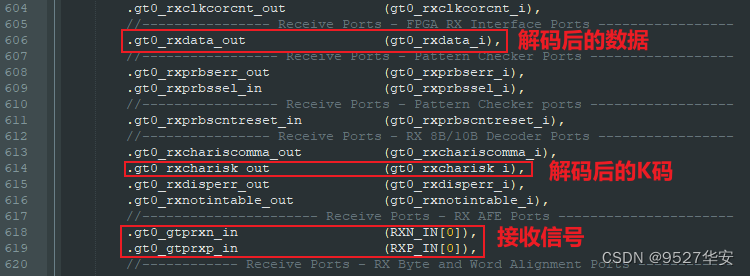

ユーザーは受信インターフェイスのクロックとデータのみを気にする必要があります。GTP インスタンス化モジュールのこの部分のインターフェイスは次のとおりです。 :

コードでは、私があなたのために再バインドしてモジュールのトップレベルにしました。コード部分は次のとおりです。

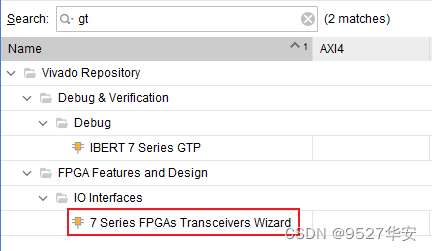

GTP IP コアの呼び出しと使用

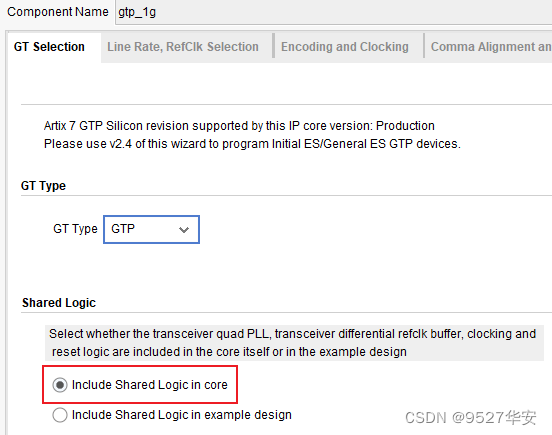

インターネット上の他のブロガーのチュートリアルとは異なり、私は個人的には、次の図に示すような共有ロジックを使用するのが好きです。

この選択には 2 つの利点があります。1 つは DRP 速度の変更を容易にすること、もう 1 つは変更を容易にすることです。 IP コアの変更後、直接コンパイルしますが、サンプル プロジェクトを開いて、以下のファイル群を自分のプロジェクトなどにコピーする必要はなくなりました。それほど複雑な作業が必要ですか? GTPをプレイするには?

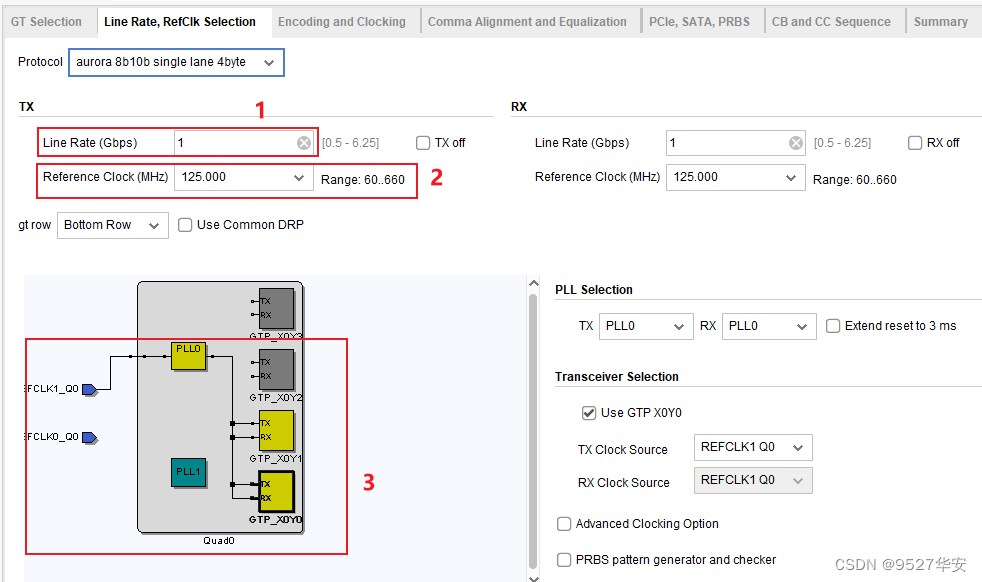

上の図のラベルの説明は次のとおりです:

1: ライン レート、独自のプロジェクト要件によると、GTP の範囲は 0.5 ~ 6.25G です。私のプロジェクトはビデオ伝送であるため、GTP レートの範囲内に収まります。 、一般的な使用向け 具体的には、vivado プロジェクトで 5 つの GTP をインスタンス化し、レートは 1G、2G、4G、5G です。2: 基準クロック、これは回路図によって異なり、80M、125M、148.5M、156.25 になります

。 M 待ってください、私の開発ボードは 125M です;

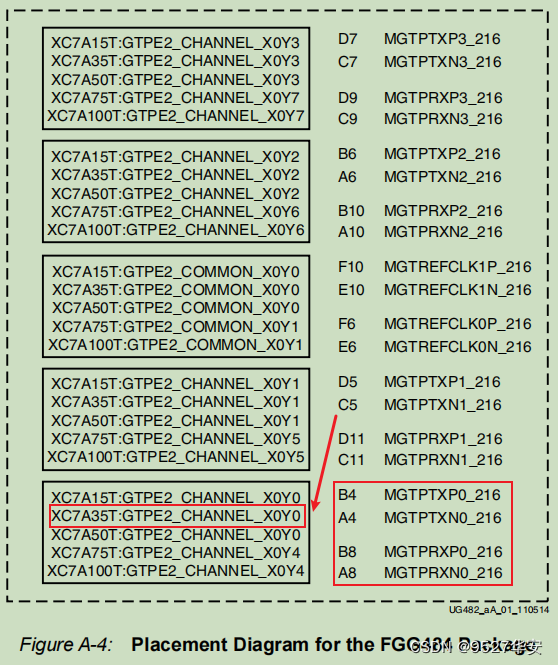

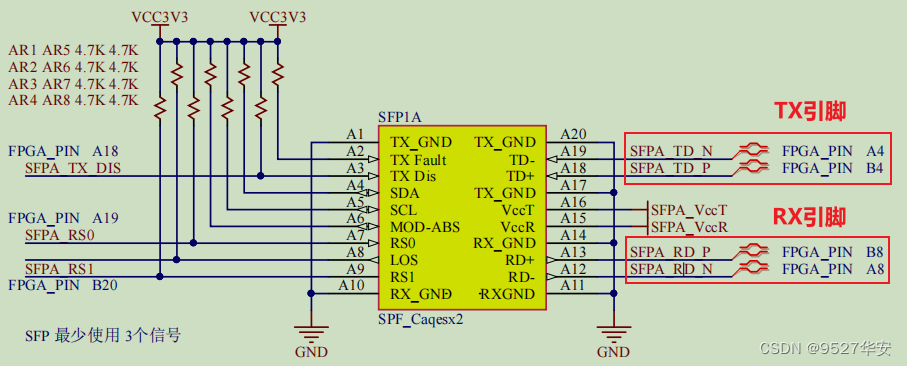

4: GTP グループ バインディング、これは非常に重要です。バインディング リファレンスが 2 つあります。これは開発ボードの回路図ですが、公式リファレンス「ug482_7Series_GTP_Transceivers」、公式 GTP リソースは 4 つに分かれています。グループの名前は X0Y0、X0Y1、X0Y2、X0Y3 です。GT リソースはザイリンクス シリーズ FPGA の専用リソースであり、専用の Bnak を占有するため、ピンも専用です。では、これらの GTP グループとブーツの足はどのように対応しますか? 「ug482_7Series_GTP_Transceivers」の説明は次のとおりです: 赤いボックスは、開発ボードの回路図に対応する FPGA ピンです。私のボードの回路図は次のとおりです: 外部

データ

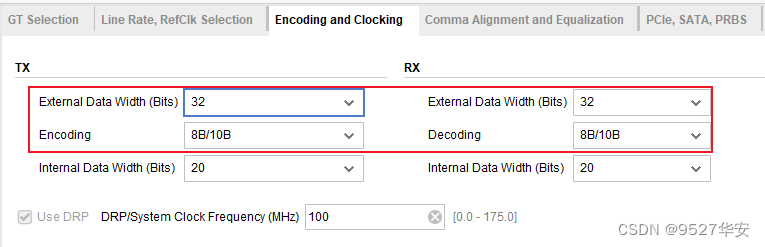

ビット幅の 8b/10b コーデックを選択します。 32 ビット、以下の通り

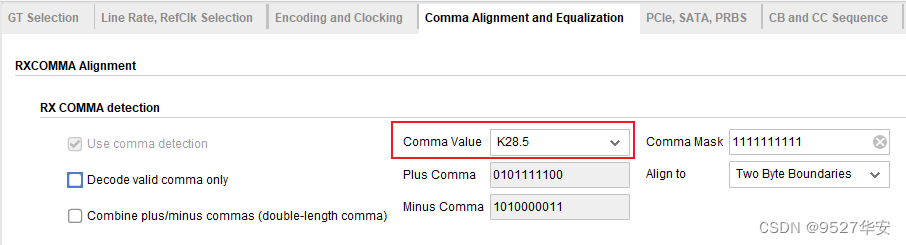

: K コード検出です:

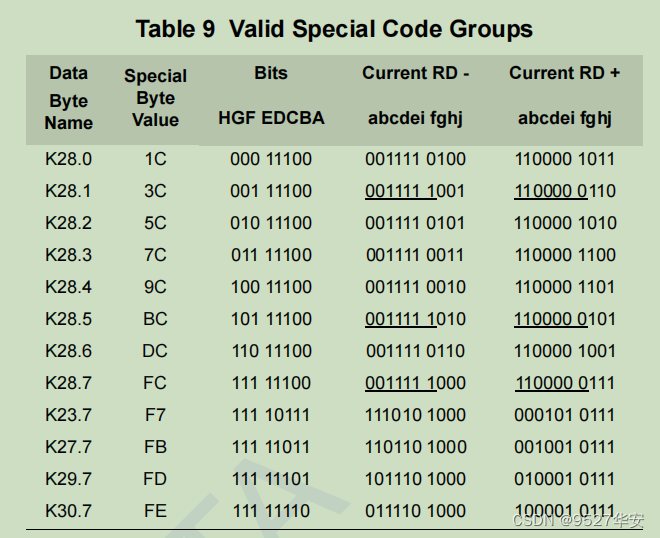

ここでは K28.5 を選択します、これはいわゆる COM コードであり、16 進数系は bc です。多くの機能があり、アイドル状態の乱れたシンボルやデータの位置ずれマークを表現できます。データの不整合をマークするために使用されます。8b/10b プロトコルでは、K コードを次のように定義します。

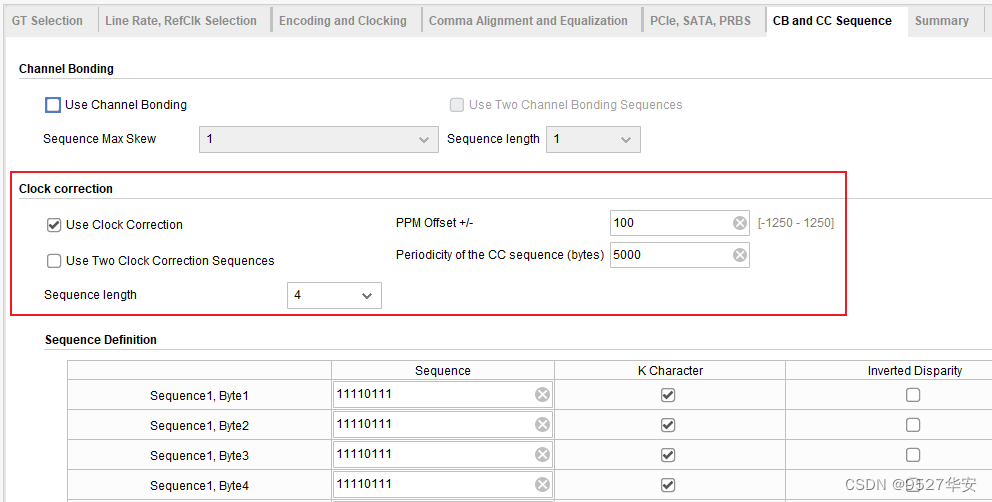

以下はクロック補正、つまり GTP の内部受信部分に対応するエラスティック バッファです。

ここにクロック周波数オフセットの概念があり、特に送信側と受信側のクロック ソースが異なる場合、ここでの周波数オフセットが設定されます。パケットの送信者は 4 バイトのシーケンスを送信し、受信者のエラスティック バッファは 4 バイトのシーケンスに従って 4 バイトのシーケンス内のバイトを削除または挿入することを決定します。バッファ内のデータの順序と位置は、送信側から受信側までのデータの安定性を確保し、クロック周波数オフセットの影響を排除するためのものです。

4. デザイン思考のフレームワーク

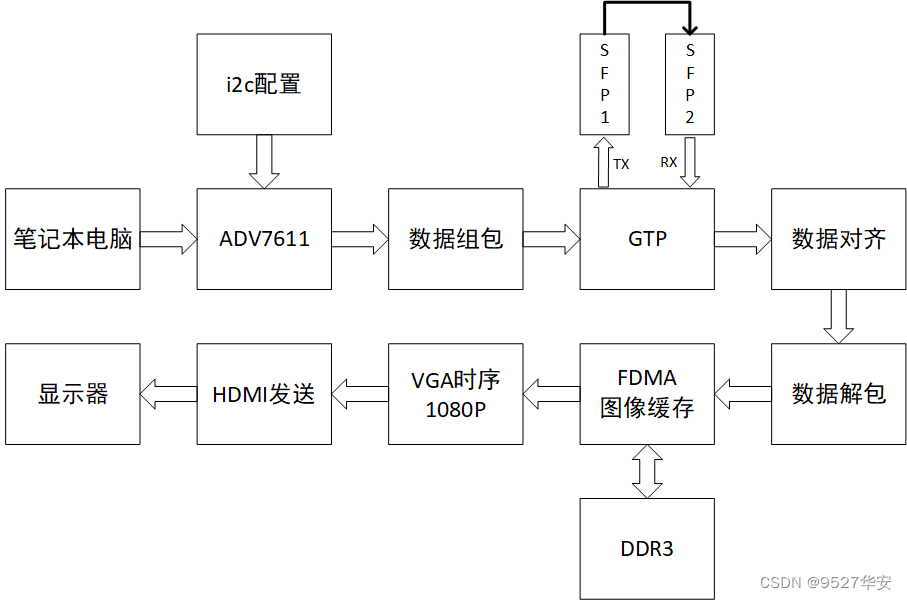

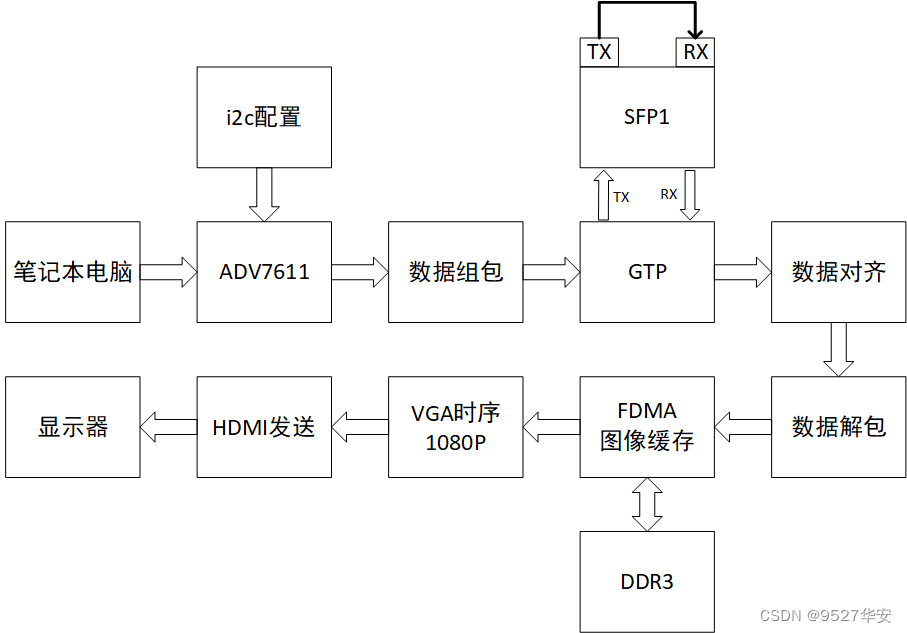

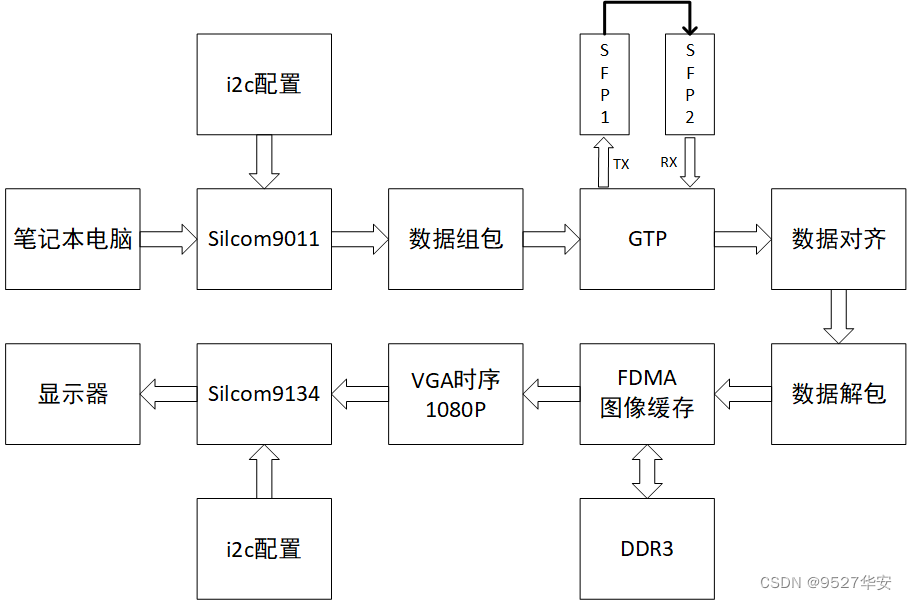

このブログでは、vivado プロジェクトのソース コードを 2 セット提供しています。2 セットのプロジェクトの違いは、送信と受信に 1 つの SFP 光ポートを使用するか、送信と受信に 2 つの 2 SFP 光ポートを使用するかであり、送信と受信に 1 つの SFP 光ポートを使用します。受信はSFPのRXを光ファイバとTXで接続すること、SFPの光ポートを2つ使って送受信することは一方のSFPのRXともう一方のSFPのTXを光ファイバで接続すること、設計思想の骨子は以下の通りです。 DHMI ビデオ入力 ADV7611 キャプチャは

2 つの SFP 光ポートを使用します。 ブロック図は次のとおりです。

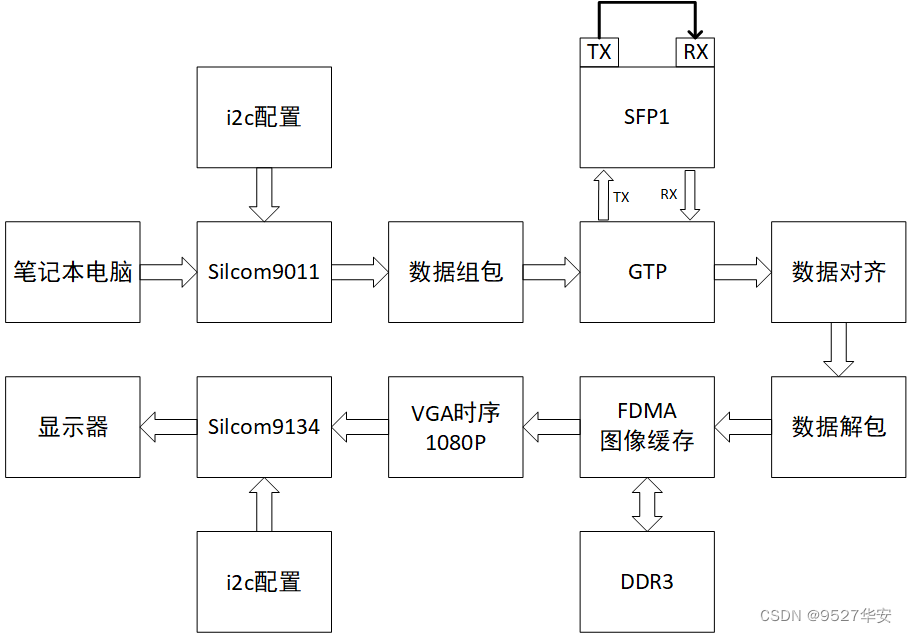

DHMI ビデオ入力 ADV7611 取得用の 1 つの SFP 光ポートのブロック図は次のとおりです。 DHMI ビデオ入力用の 2 つの SFP 光ポートのブロック

図 silcom9011

DHMI ビデオ入力 silcom9011 取得用の 1 SFP 光ポートのブロック図は次のとおりです。

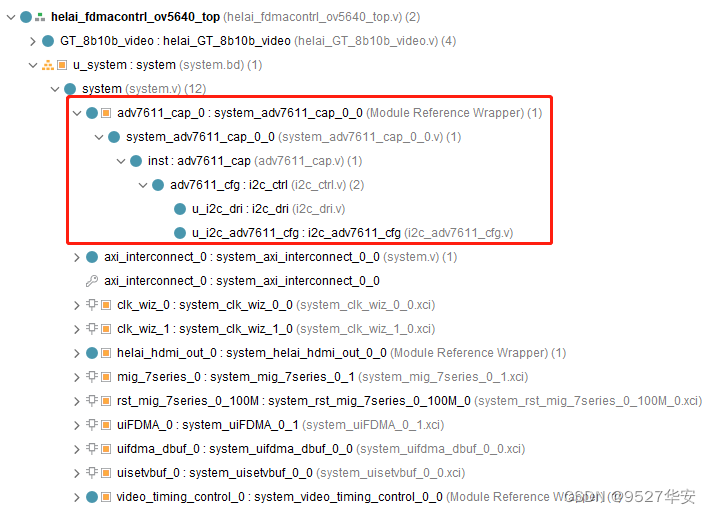

HDMI入力ビデオの設定とキャプチャ

プロジェクト 1 の HDMI 入力デコードは ADV7611 チップによって完了します。プロジェクト 1 の HDMI 入力デコードは Silicon9011 チップによって完了します。どちらも使用するには i2c 構成が必要で、どちらも純粋な Verilog コードで実装された i2c 構成モジュールによって完了します。コード位置は次のとおりです。

Silicon9011 チップの構成については、以前のブログを参照してください。ブログ アドレス:クリックして直接移動します。

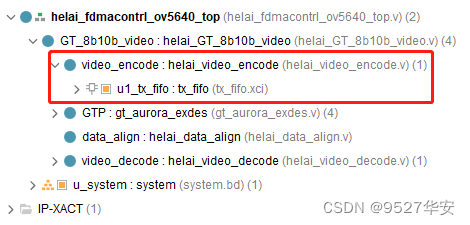

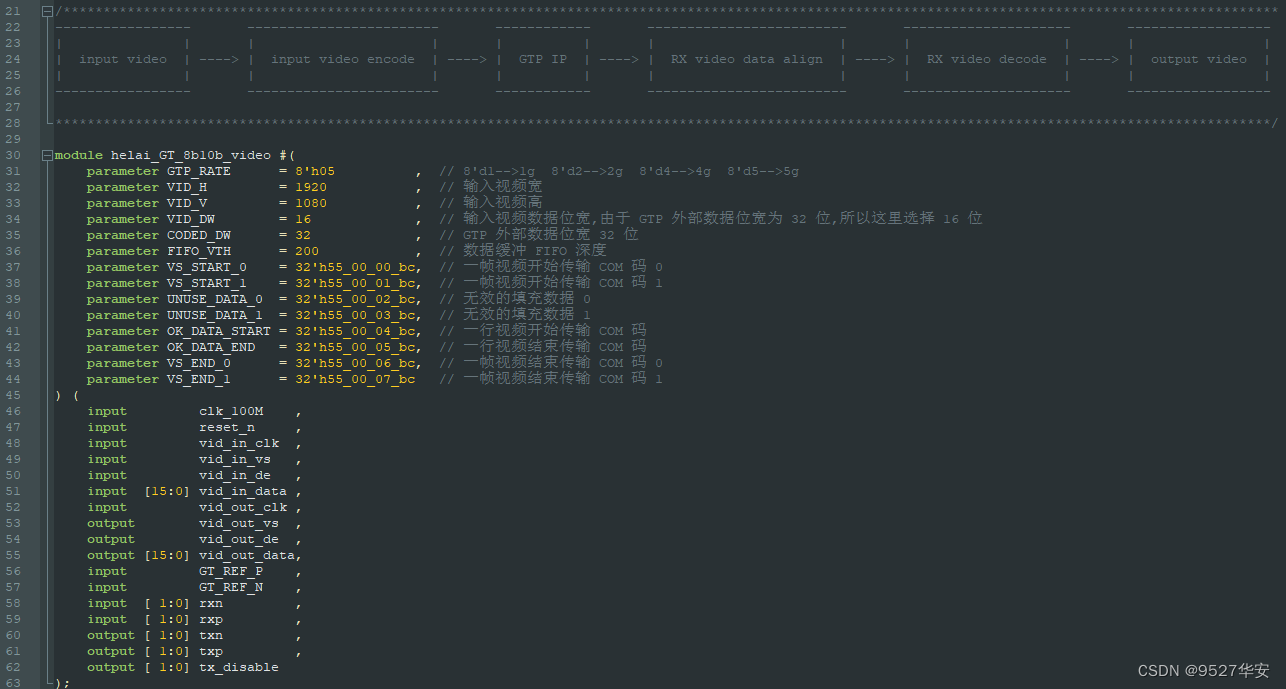

ビデオパケット

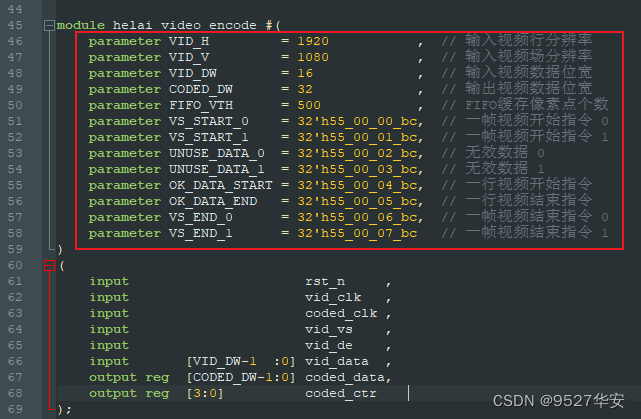

ビデオは GTP の aurora 8b/10b プロトコルを通じて送受信する必要があるため、aurora 8b/10b プロトコル標準に適合するようにデータをパッケージ化する必要があります。ビデオ データ パッケージ モジュールのコード位置は次のとおりです。 16 ビット ビデオを FIFO に保存します

。行がいっぱいになると、FIFO から読み取られて GTP に送信されて送信されます。その前に、ビデオのフレームに番号を付ける必要があります。これは命令とも呼ばれます。GTP がパックするとき、このコマンドは、ビデオフィールド同期信号とビデオ有効信号を復元し、ビデオフィールド同期信号のフレームの立ち上がりエッジが到着するとビデオ開始命令 0 のフレームを送信し、立ち下がりエッジが到着するとビデオ開始命令 0 のフレームを送信します。ビデオフィールド同期信号のフレームの到着、フレームを送信 ビデオ開始コマンド 1、ビデオブランキング期間中に無効データ 0 と無効データ 1 を送信、ビデオ有効信号が到着したらビデオの各ラインに番号を付け、最初にビデオのラインを送信ビデオの 1 ラインが送信されると、開始コマンドが送信され、現在のビデオ ライン番号が送信されます 完了後、ビデオのラインの終了コマンドが送信されます ビデオのフレームが送信された後、最初にビデオのフレームの終了コマンド 0 が送信され、次にビデオの終了コマンドが送信されます動画のフレーム終了コマンド 1; ここまでで動画のフレームが送信されます このモジュールはわかりにくいので、コード内に中国語の詳細なコメントを入れました なお、中国語の表示が乱れるのを防ぐため、コメントは、notepad++ エディタを使用してコードを開いてください。コマンド定義は次のとおりです。コマンドは任意に変更できますが、最下位バイトは

bc である必要があります。

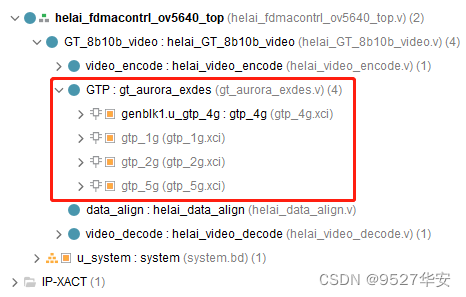

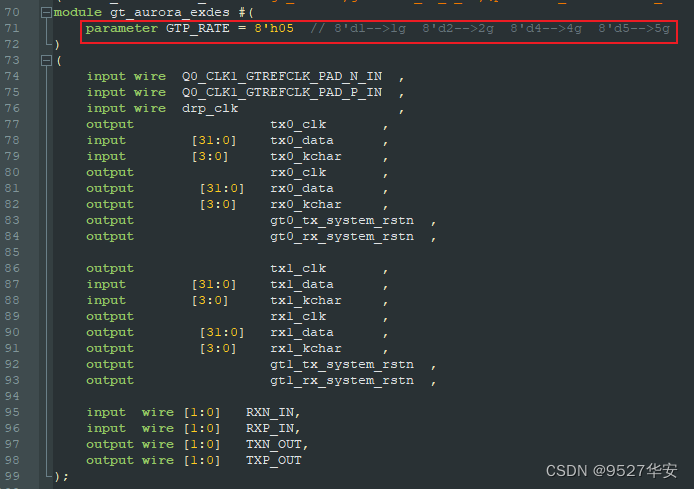

GTP オーロラ 8b/10b

これは、GTP を呼び出して、aurora 8b/ 10b プロトコルのデータ エンコードとデコードを行うためのものです。GTP の詳細な概要はすでに説明したので、ここでは説明しません。2G

GTP_RATE=8'd1、GTP は 1G ライン レートで実行; GTP_RATE

=8'd2、GTP は 2G ライン レートで実行;

GTP_RATE=8'd4、GTP は 2G ライン レートで実行; 4G ライン レート;

GTP_RATE=8'd5、GTP は 5G ライン レートで実行されます。

私のテストによると、GTP が 4G ライン レートで実行される場合にビデオ伝送効果が最も優れています。

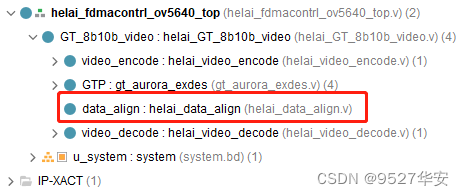

データアライメント

aurora 8b/10b の GT リソースのデータ送受信では当然データのずれがあるため、受信したデコードデータに対してデータのアライメント処理を行う必要があります データアライメントモジュールのコード位置は以下の通りです: K コード制御文字フォーマット私が定義したのは XX_XX_XX_BC なので、

1 つを使用します。 rx_ctrl は、データが K コード COM シンボルであるかどうかを示します。rx_ctrl

= 4'b0000 は、4 バイト データに COM コードがないことを示します。rx_ctrl

= 4'b0001 は、[7: 0] であることを示します。 ] は 4 バイト データの COM コードです。rx_ctrl

= 4'b0010 は 4 バイト データの [15:8] が COM コードであることを意味します。rx_ctrl

= 4'b0100 は 4 バイト データの [23:16] を意味します。バイト データは COM コードです。rx_ctrl

= 4'b1000 は、データ内の 4 バイト [31:24] が COM コードであることを意味します。

これに基づいて、K コードを受信すると、データは整列されます。データはパッティングされ、新しい受信データと結合されます。これが FPGA 動作の基礎ですが、ここではこれ以上の詳細は説明しません。

動画データの解凍

データのアンパックは、データのグループ化の逆のプロセスであり、コードの位置は次のとおりです:

GTP のアンパック時には、ビデオ フィールド同期信号とビデオ有効信号が一定の命令に従って復元されます。これらの信号は、後続の画像キャッシュにとって重要な信号です

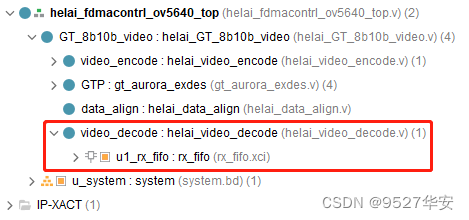

。 、データが GTP に出入りする部分は完成し、プロセス全体のブロック図は次のようにコードで記述されます。

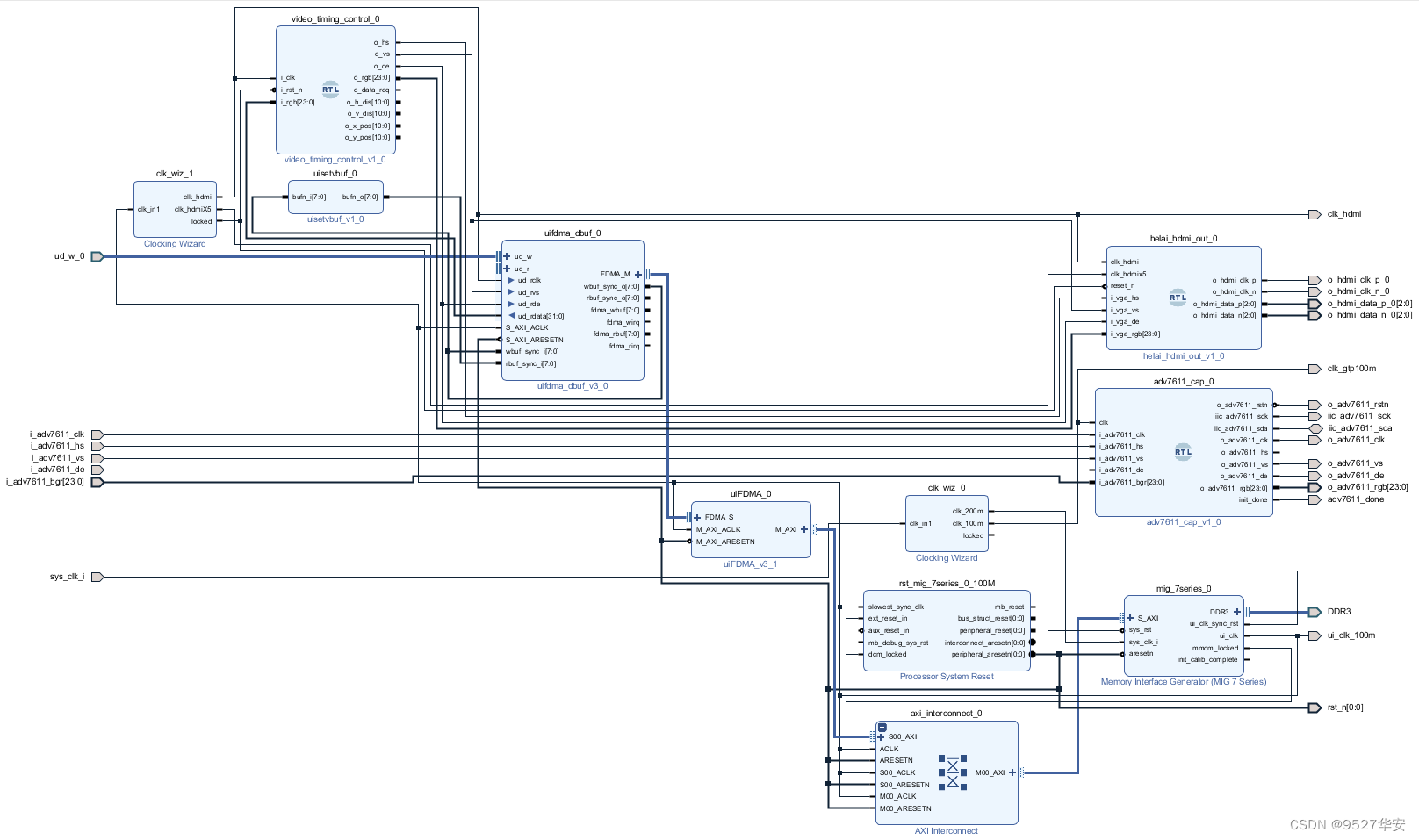

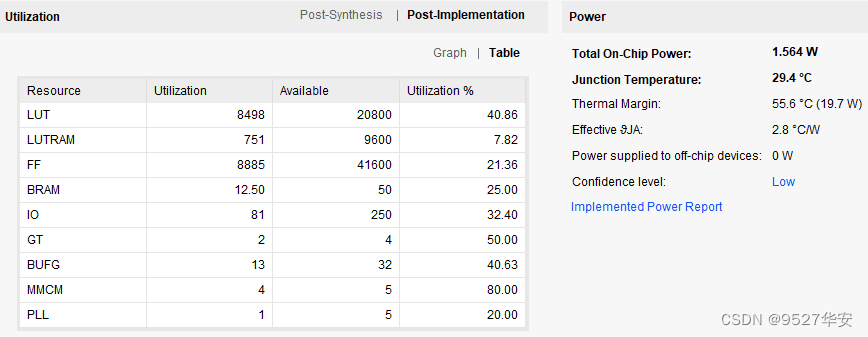

画像キャッシュ

私のブログをよく読んでいる古いファンは、私の画像キャッシュのルーチンが FDMA であることを知っていると思います。その機能は、画像を 3 フレーム バッファの DDR に送信し、表示のために読み出すことです。目的は、入力と出力のクロック差を一致させることです。ビデオ品質、FDMA については、以前のブログを参照してください。ブログ アドレス:クリックして直接移動します

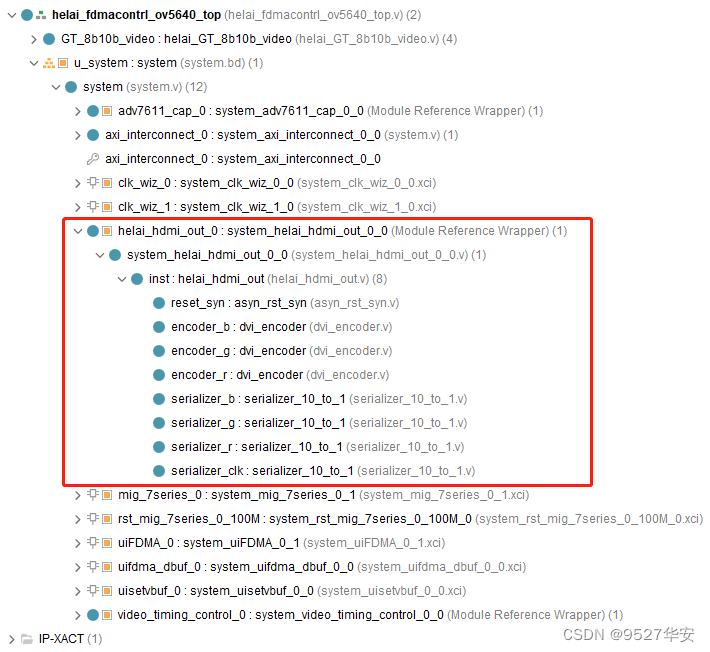

HDMIビデオ出力

プロジェクト 1 とプロジェクト 2 では、ビデオが FDMA から読み取られた後、VGA タイミング モジュールと HDMI 送信モジュールを通過した後にディスプレイに出力されます。コードの場所は次のとおりです: VGA タイミング構成は 1920X1080 で、 HDMI 送信モジュールは Verilog コードで手書きされており、FPGA HDMI 送信アプリケーションに使用できます

。このモジュールについては、以前のブログを参照してください。ブログ アドレス:クリックして直接移動します。

プロジェクト 3 とプロジェクト 4 の HDMI 出力エンコーディングは、silicon9134 チップによって完成されており、使用するには i2c 構成が必要です。silicon9134 チップの構成については、以前のブログを参照してください。ブログ アドレス: クリックして直接移動します。

5. vivado プロジェクト 1 –> ADV7611 の取得 –> 双方向 SFP 送信

開発ボード FPGA モデル: Xilinx–Artix7–xc7a35tfgg484-2;

開発環境: Vivado2019.1;

入力: ラップトップ出力アナログ HDMI ビデオ入力、解像度 1920x1080@60Hz、ADV7611 デコード;

出力: HDMI ディスプレイ; 純粋な verilogHDMI 伝送モジュール;

アプリケーション: 2 -way SFP 光ポート GTP aurora 8b/10b コーデック ビデオ伝送;

プロジェクトのブロック設計は次のとおりです: プロジェクトの

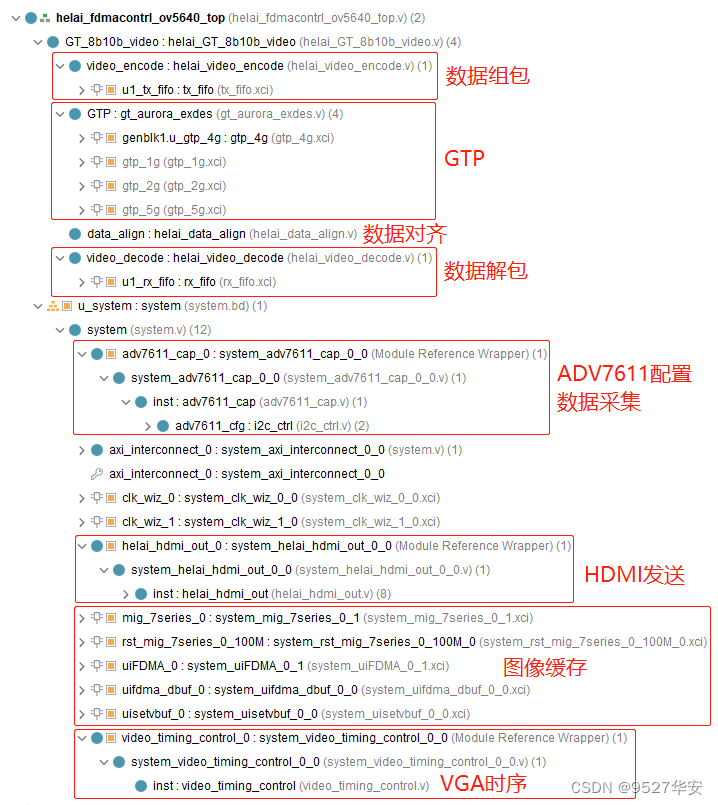

コード構造は次のとおりです:

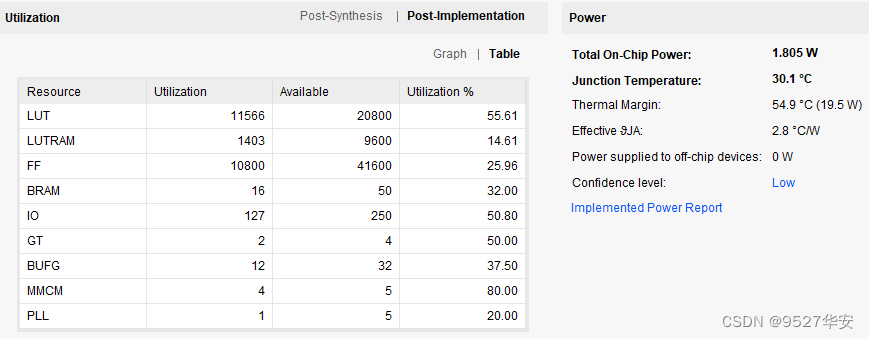

包括的なコンパイル後の FPGA リソース消費量と消費電力の見積もりは次のとおりです:

6. vivado プロジェクト 2 –> ADV7611 取得 –> 1 チャネル SFP 送信

開発ボード FPGA モデル: Xilinx–Artix7–xc7a35tfgg484-2;

開発環境: Vivado2019.1;

入力: ラップトップ出力アナログ HDMI ビデオ入力、解像度 1920x1080@60Hz、ADV7611 デコード;

出力: HDMI ディスプレイ; 純粋な verilogHDMI 伝送モジュール;

アプリケーション: 1チャネル SFP 光ポート GTP aurora 8b/10b コーデック ビデオ伝送、

プロジェクトのブロック デザイン、プロジェクトのコード構造、総合コンパイル後の FPGA リソース消費量および消費電力の見積もりは第 5 章と同じです。

7. vivado プロジェクト 3 –> Silicon9011 の取得 –> 双方向 SFP 送信

開発ボード FPGA モデル: Xilinx–Artix7–xc7a35tfgg484-2;

開発環境: Vivado2019.1;

入力: ラップトップ出力アナログ HDMI ビデオ入力、解像度 1920x1080@60Hz、シリコン 9011 デコーディング;

出力: HDMI ディスプレイ、シリコン 9134 エンコーディング;

アプリケーション: 2 SFP オプティカルポート GTP aurora 8b/10b エンコードおよびデコードビデオ伝送;

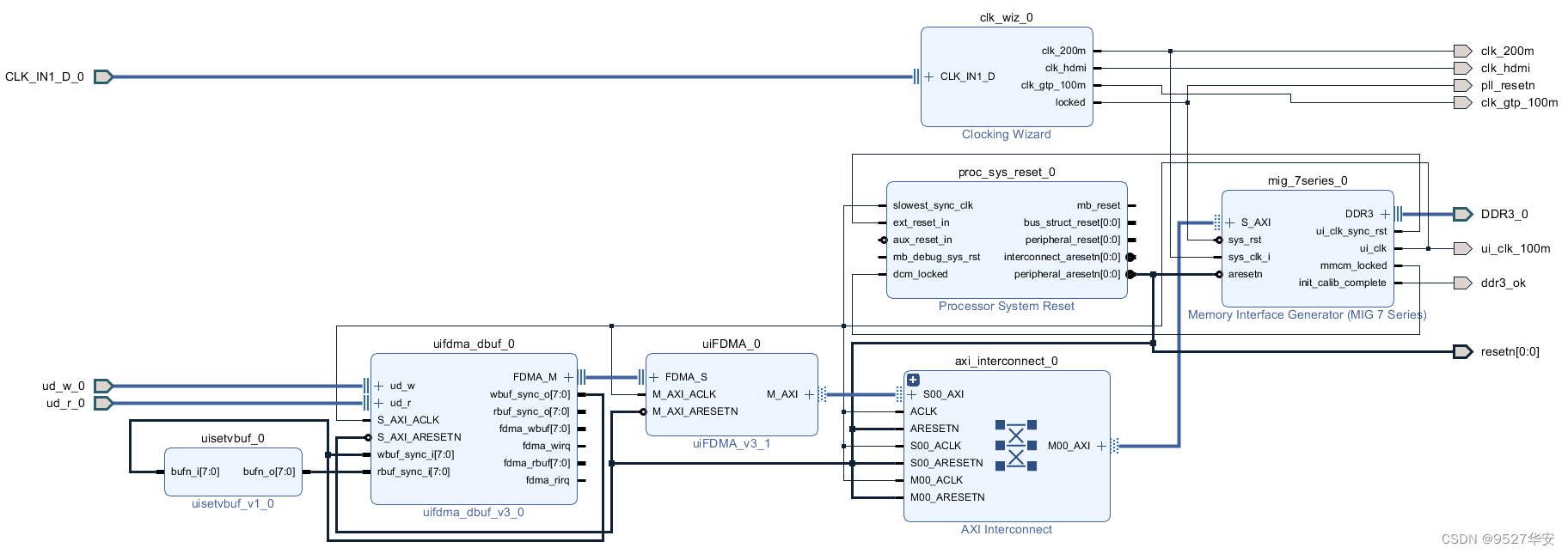

プロジェクトのブロック設計は次のとおりです: プロジェクトの

コード構造は次のとおりです:

包括的なコンパイル後の FPGA リソース消費量と消費電力は次のように推定されます。

8. vivado プロジェクト 4 –> Silicon9011 取得 –> 1 チャネル SFP 送信

開発ボード FPGA モデル: Xilinx–Artix7–xc7a35tfgg484-2;

開発環境: Vivado2019.1;

入力: ラップトップ出力アナログ HDMI ビデオ入力、解像度 1920x1080@60Hz、シリコン 9011 デコーディング;

出力: HDMI ディスプレイ、シリコン 9134 エンコーディング;

アプリケーション: 1 チャネルSFP 光ポート GTP aurora 8b/10b コーデック ビデオ伝送、

プロジェクトのブロック デザイン、プロジェクトのコード構造、総合コンパイル後の FPGA リソース消費量および消費電力推定は第 5 章と同じです。

9. ボードのデバッグと検証

光ファイバー接続

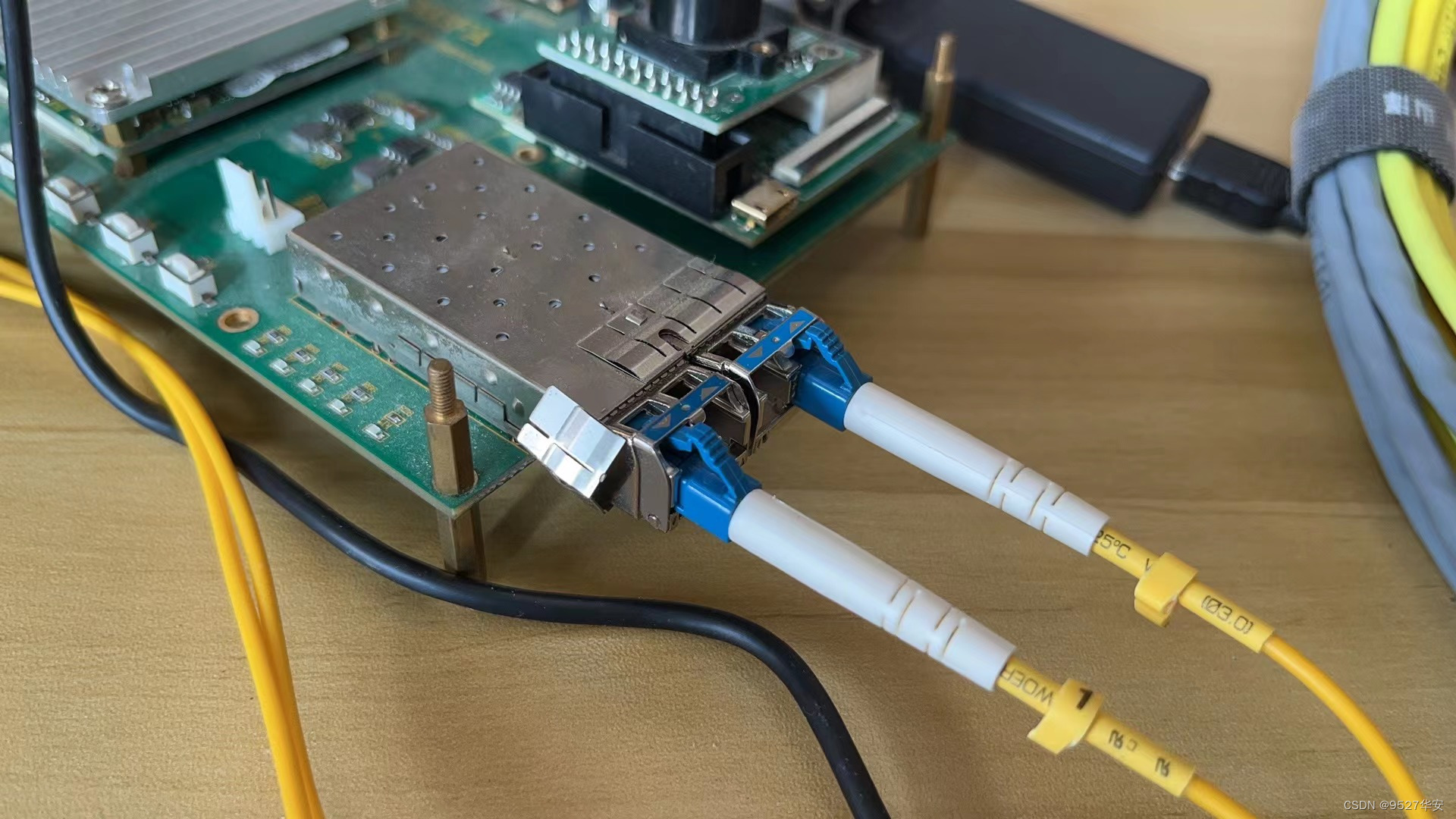

プロジェクト 1: 双方向 SFP 伝送のファイバー接続方法は次のとおりです。

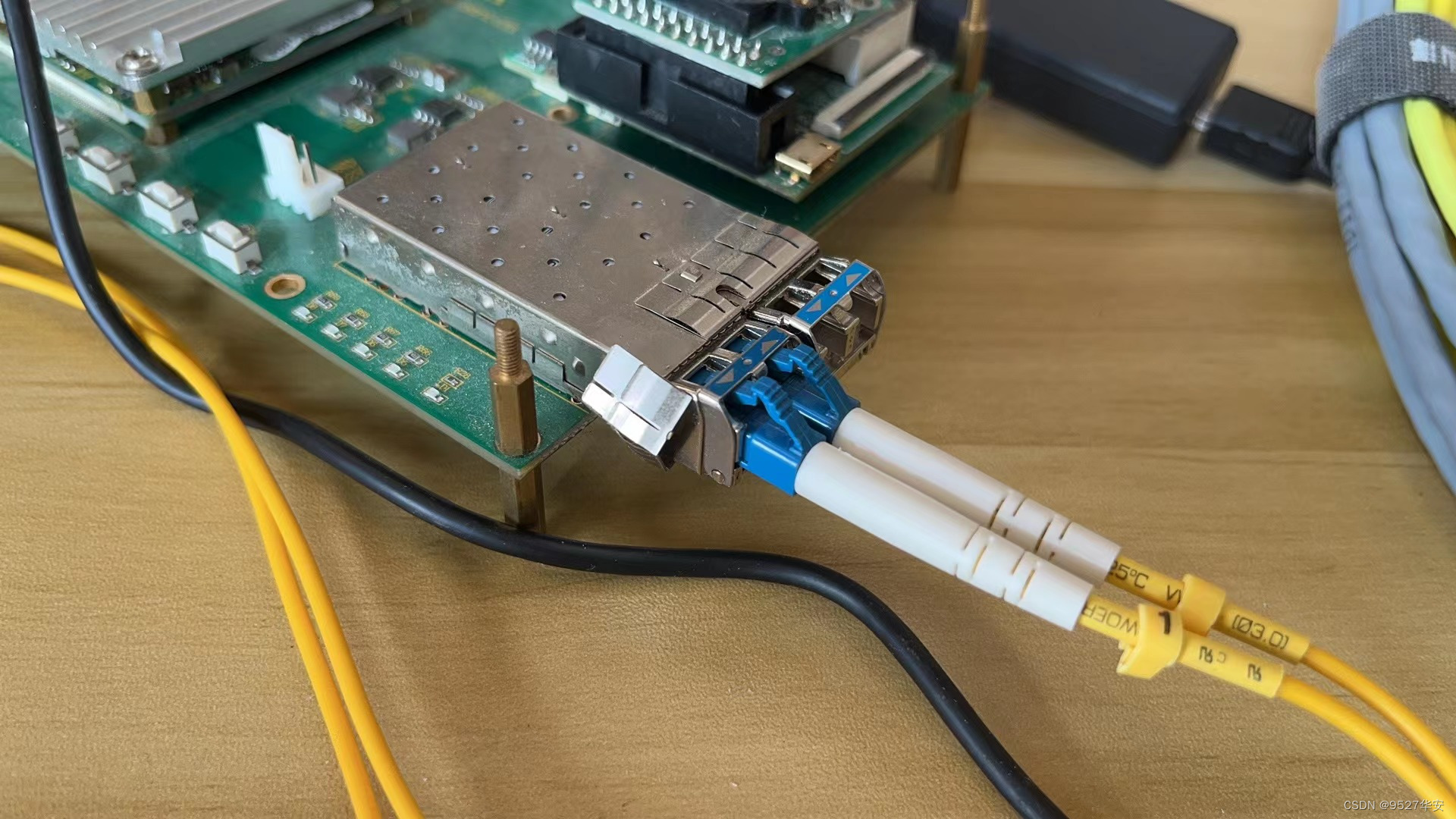

プロジェクト 2: 1 方向 SFP 伝送のファイバー接続方法は次のとおりです。

静的デモ

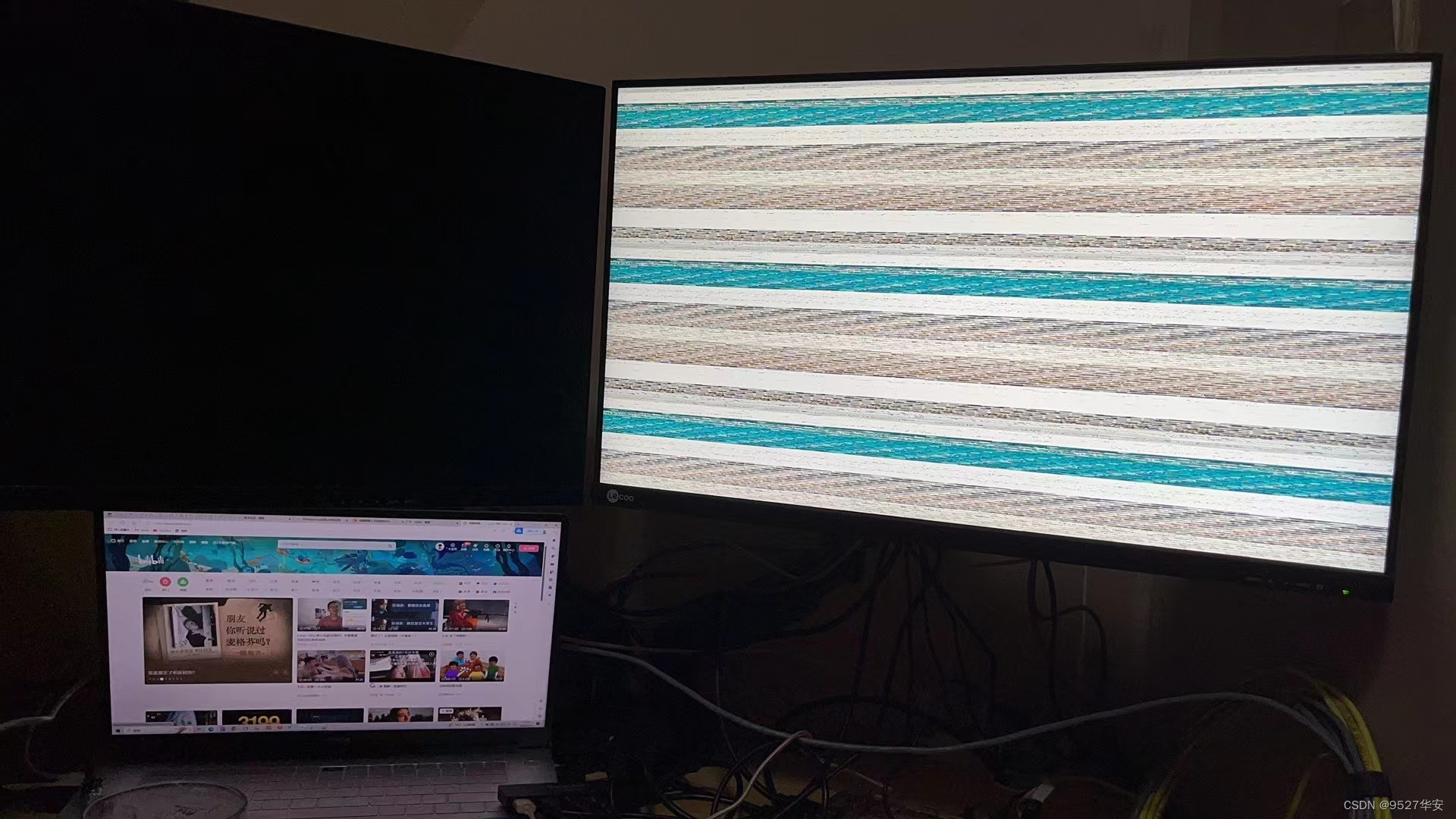

以下では、プロジェクト 1: 双方向 SFP 伝送を例として出力効果を示します。GTP が

1G および 2G ライン レートで実行されている場合、出力は次のようになります。

出力ビデオが乱れていることがわかります。レートが低すぎる。

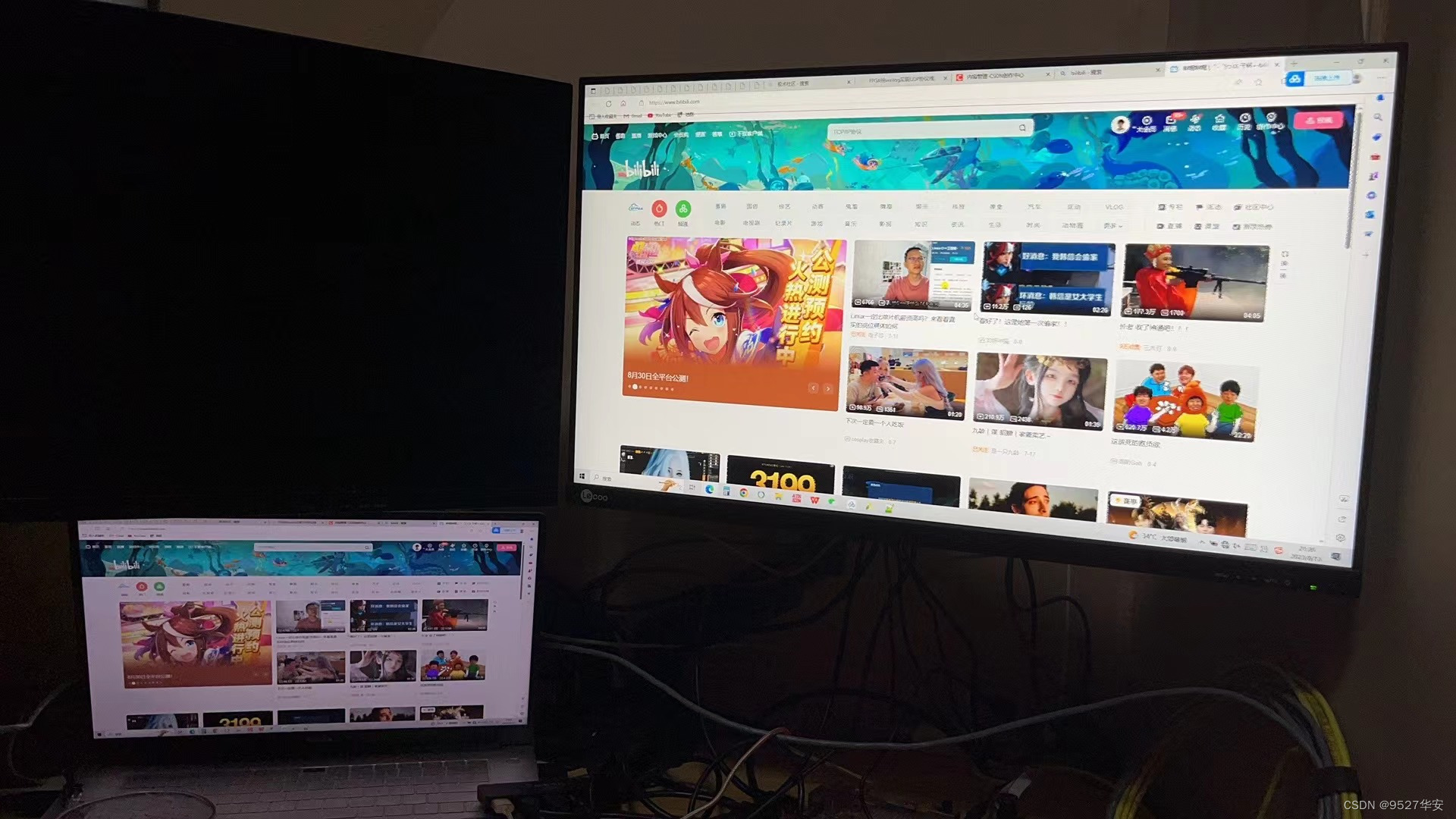

GTP ライン レートを 4G に増やすと、出力は次のようになります。

ご覧のとおり、この時点で出力ビデオ品質はすでに非常に高くなっています。

GTP ライン レートを 5G に上げると、出力は次のようになります。

注意深く観察すると、この時点で出力ビデオにノイズがあることがわかります。これは、ライン レートが高すぎるためです。

ダイナミックなプレゼンテーション

慎重に比較した結果、GTP が 4G ライン レートで動作する場合、出力ビデオ品質が最も高くなることがわかりました。以下は、GTP が 4G ライン レートで動作する場合の短いビデオを示しています。

GTP_HDMI_7611

10. 福利厚生:技術コード取得

メリット: エンジニアリングコードの取得

コードは電子メールで送信するには大きすぎるため、ある程度のネットワークディスクリンクで送信

データの取得方法: 非公開、または記事末尾の V 名刺

ネットワークディスク情報は以下のとおりです。